Изобретение относится к гибридной вычислительной технике.

Известны сумматоры-внтеграторы, содержащие суммир;ующую .резистивную матрицу, вертикальные шины которой соединены с основными входами, а горизонтальные подключены ко входам соответствующих сумматоров, блоки переноса, линии задержки, резисторы и инверторы с резистивными обратными связями.

С .щелью повыщения точности выполнения математических в каждом разряде предлагаемого устройства выход сумматора через резистор соединен со входом соответствующего илвертора, выход которого через последовательно соединенные линию задержии и входной резистор подключен -ко входу сумматора.

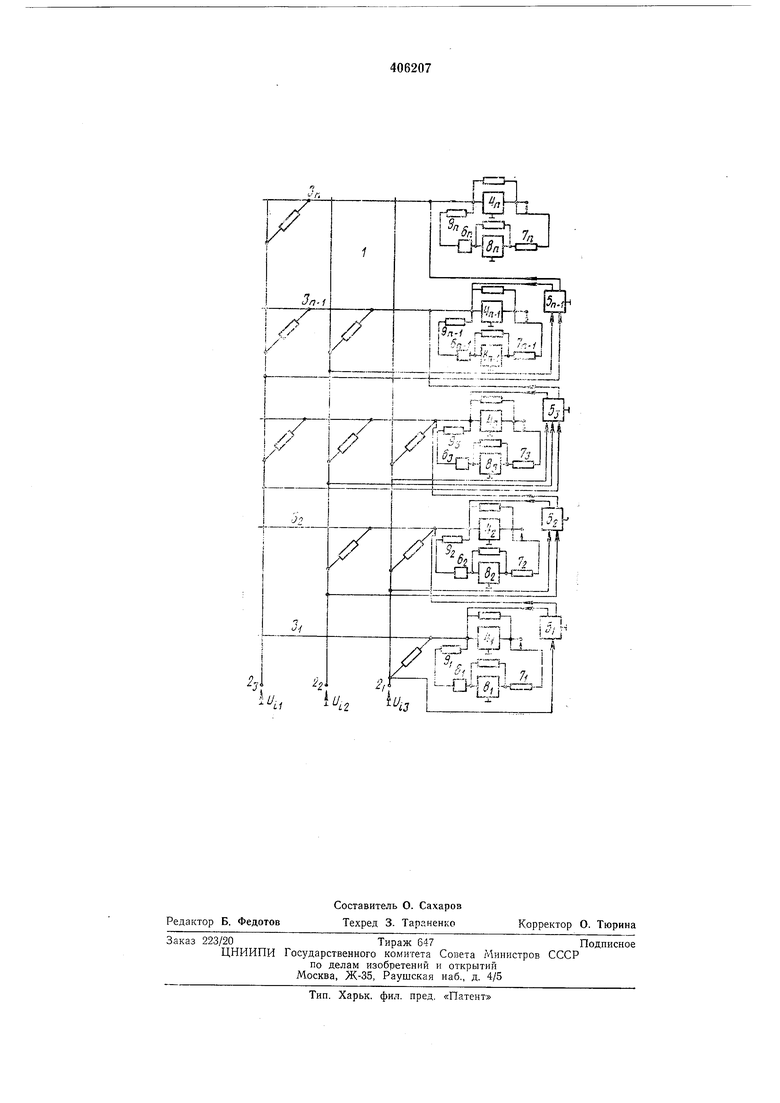

Принципиальная схема устройства приведена на чертеже.

Сумматор-интегратор содержит суммирующую резистивную Матрицу 1 с вертикальными щинами и горизонтальными , сумматоры с резистивными обратными связями 4i-4п, блоки переноса 5i-5„ 1, линии задержки 6i -6 п на один такт, резисторы 7i - 7п, инверторы с резистивными обратными связями 5i - 5„ и входные резисторы ...

Интегрируемые функции времени Fi, Vz, УЗ в каждый момент представляются соответственно векторами напряжений

f7, (f/i,J7,2t/.3), U2 (), f/3 (t/3,).

Ком1ПОненты векторов пропордиональны

значениям соответствующих разрядов чисел

(для рассмотренля принципа работы предлапаемого устройства интегрируемые функции

представлены тремя разрядами).

В момент времени О, т. е. на первом щаге иятелрирования, на входы устройства поступают векторы напряжений

f/i (U,,U,U,), U, (U2,L)22U,,),

из (f/31 32f/33).

На выходах устройства образуется вектор напряжений

Uo (/7о1 о2 /оз) f/i + U2 + f/3

(UnUizU s) + (f/21 22 23) + -f (3lf/32 33),

компоненты .которого через линии задержки 6i - 6п на один та.кт опять подаются на входы сумматоров 4i - 4„. Умножение вектора /о на it дает приближенное значение интеграла суммы йинтегрируемых функций на первом щаге. При t ti, на входы устройства поступают векторы наПряжений , , z, соответствующие знач1ениям входных функций на втором шаге интегрирования, которые, складываясь с вектором + U2+03, поступающим «а входы суММаторов 4i - 4„ в лачале второго такта из линий задержки 6i - 6п, образуют вектор наяряжен-ий ( Uo + . Умножение вектора (У на t дает приближеЕное значение интеграла суммы функций ,на яервом и втором шагах интегрирования. Таким Образом, интеграл суммы трех функций «а т шагах интегрирования определяется выражением SZ7,,, ; 1 « 1 где т - количество Ш1агов интегрирования; t - шаг интегрирования, который в обш;ем случае может быть многоразрядным. Выбор числа разряда шага интегрировапия определяется, с одной стороны, разрядностью представления чисел входных функций, с другой стороны - удобствами тактирования работы устройства и упрошения его схемы. Для случая представления интегрируемых функций тремя разрядами он может достигать только трехразрядного числа, т. е. At - . Лучше всего шаг интегрирования выбирать таким, чтобы значащая цифра была в одном из разрядов, например /ь а 4 0. Это упрош:ает схему устройства, так как резистивная матрица 1 становится при этом квадратной и диагональной. Если проводимости матриц /-3 удовлетворяют соотношениям г Ь giZ, tz, giz tz, (где ,мер .матрицы), работа устройства в точности описывается выражением (1), т. е. устройство интегрирует сумму трех функций по методу прямоугольников и умножает их на единичные коэффициенты. Чтобы получить устройство, интегрируюш,ее сумму функций и умножающее их на постоянные коэффициенты, отличные от единицы, необходимо предварительно умножить величины этих коэффициентов на шаг интегрирования и параметры .матриц подбирать пропорциональными разрядам этого произведения. Работа устройства в этом случае описывается выражениемi/o - 2 S (Д й„) и„, где т - количество шагов интегрирования; t - шаг ияте.грирова.ния; а„ - величина постоянного коэффициента, на которую умножается /г-ная функция. Блоки переноса 5i - 5„ выполняют межразрядный перенос с одновременной компенсацией напряжения в усилителе, из которого возник перенос. Предмет изобретения Сумматор-интеграто.р, содержащий сум.мирующую резистивную матрицу, вертикальные шины которой соединены со входами сумматора-интегратора, а .горизонтальные подключены ко входам соответствующих п сумматоров с резистивными обратными связями, п-1 блоков переноса, входы которых соедине.ны с вертикальными шинами суммирующей резистивной матрицы, а выходы подключены ко входам сумматоров да.нного и следующего разрядов, п линий задержки, резисторы и п инверторов с резистивными обратными связями, отличающийся тем, что, с целью повышения точности, в каждом его разряде выход сумматора через резистор соединен со входом соответствующего инвертора, выход которого через последовательно соединенные линию аадержки и входной рез|Истор подключен ко входу сумматора.

Зп.

n-i

/

jFil И

ST

&

„,™ i /.v i I I

- Л--,

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегратор | 1980 |

|

SU928351A1 |

| ОПТОЭЛЕКТРОННОЕ УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙ В ЧАСТНЫХ ПРОИЗВОДНЫХ | 1991 |

|

RU2042180C1 |

| Устройство для решения систем линейных алгебраических уравнений | 1985 |

|

SU1265810A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" | 2011 |

|

RU2475812C1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ СИСТЕМДИФФЕРЕНЦИАЛЬНЫХ И АЛГЕБРАИЧЕСКИХУРАВНЕНИЙ | 1972 |

|

SU428405A1 |

| УСТРОЙСТВО для ИНТЕГРИРОВАНИЯ ФУНКЦИЙ в ДВОИЧНО-ДЕСЯТИЧНОМ ЦИКЛИЧЕСКОМ КОДЕ | 1967 |

|

SU203321A1 |

| Матричный умножитель по модулю чисел Ферма | 1990 |

|

SU1783513A1 |

| РЕШАЮЩИЙ БЛОК ДЛЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО | 1972 |

|

SU355631A1 |

| Устройство для приема четверично-кодированных сигналов | 1991 |

|

SU1818693A1 |

| КОРОТКОВОЛНОВЫЙ ПРИЕМНЫЙ ЦЕНТР | 2011 |

|

RU2461873C1 |

-7//

(-1.г--.

h

|.-|1Л-4-.

.-mi- --- --

J,;,-S--1,

,,

(771-.-..- : ГГ 3 ,

П

-;ЛЗ-&1

/X ,5, I-j I)

L |jin:u-jf

i i- jrrjij u

J./

f

1//,

pjTD--,

I f- -ff-c I

I f ,

( , :i-/

7: rfi4:№ :i Г-4 .3 i

i У; f.

,J-Hr: J

Авторы

Даты

1973-01-01—Публикация