1

Изобретение относится к вычислительной технике.

Известны устройства контроля информационного тракта запоминающее устройство (ЗУ) команд - процессор, содержащее схему контроля на четность, соединенную с выходным регистром запоминающего устройства, и схему управления, вход которой подключен к выходу схемы контроля на четность, входные и выходные вентили.

Недостаток этих устройств - отсутствие коррекции обнарул иваемых ошибок. В то же время известные устройства обнаружения и коррекции ошибок с применением контрольных кодов используют значительное количество дополнительного оборудования.

Цель изобретения - повышение надежности работы устройства.

Поставленная цель достигается тем, что в устройство введен сумматор по модулю 2, счетный вход каждого разряда которого соединен с выходом входных вентилей, первые входы которых соединены со схемой управления, а вторые - с выходным регистром запоминающего устройства, выходы сумматора по модулю 2 соединены со входами выходных вентилей, вторые входы которых соединены со схемой управления, а выходы - со входом выходного регистра.

В одну из ячеек ЗУ, разбитого па зоны по k слов (величина k выбирается в зависимости от необходимой скорости исправления ошибки), записывается контрольная сумма слов зоны по модулю 2.

После обнаружения устойчивого сбоя в слове, поступившем из ЗУ в выходной регистр памяти, оно суммируется по модулю 2 с массивом зоны, содержащим это число, и в том числе с контрольной суммой, что дает возможность на выходе регистра, суммирующего по модулю 2, получить исправленное число.

Представим зону ЗУ из //n-paзpядныx слов в виде матрицы

15

Л

20

где - k-ая строка представляет собой контрольную сумму k-1 строк по модулю 2.

/k-i

Oki ai. mod 2 : (л -f ayj mod 2, /

/1 aki -uji I

Предположим, что в строке (слове) / в /-ом столбце (разряде) появилась ошибка Xj .

В этом случае матрица примет вид

В

Тогда сумма по k-I строкам t-oro столбца (для простоты рассматривают суммирование по модулю 2 только в одном разряде памяти) будет

aki (a-ki - Oji + )vj) mod 2 () mod 2,

Просуммировав по модулю 2 Kf и i-ый столбец м.атрицы В, получают

5 : (Х, + uft + tti) mod 2 -

hi + + -h+f + -/i 2 r 12(, + «),+ a, mod-2 a..

Получают исходную информацию.

Таким образом можно исправлять информацию в любом разряде одного слова памяти для каждой зоны из k слов.

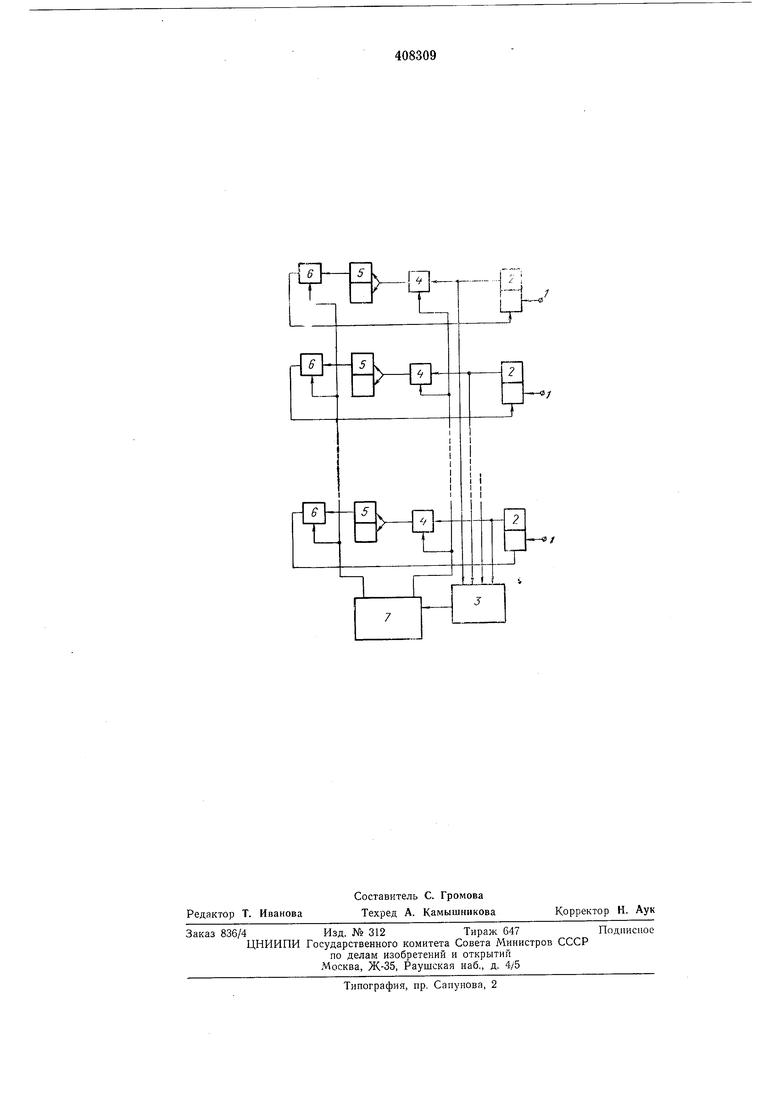

На чертеже приведена структурная схема, реализующая исправление обнаруживаемых ошибок в информационном тракте «ЗУ команд - процессор. При решении ЦВМ некоторой задачи производится систематический запрос ЗУ и считывание информации из ЗУ по информационным шинам 1 в выходной регистр запоминающего устройства 2. При этом информация, поступающая из регистра памяти в процесеор, постоянно контролируется схемой контроля по четности 3.

Входное вентили 4, управляющие передачей чирла из регистра памяти на регистр-сумматор 5, суммирующий по модулю 2, выходние вентили 6, управляющие передачей числа из суммирующего регистра 5, закрыты сигналом едицичного уровня.

При в регистре памяти искаженной информации схема контроля вырабатырает соответствующий сигнал, который поступает в схему управления управления вырабатывает сигнал блокировки микроопераций и производит повторный запрос ЗУ по этому же адресу.

При тревдратном считывании искаженной информации по этоаду адресу сбой считается устойчивым.

В этом случае схема управления вырабатывает сигнал сброса регистра 5 (щина сброса на схеме не показана) и записывает адрес отказавшей ячейки в адресный регистр в устройстве приоритетного прерывания по имеющемуся каналу связи счетчик команд - адресный регистр устройства приоритетного прерывания.

После этого схема управления записывает начальный адрес зоны ЗУ, в которой имеется нарушение информации (начальный адрес зоны ЗУ получают сбросом младших разрядов счетчика команд).

После этого схема управления открывает входные вентили 4 и выдает в ЗУ k последовательных запросов ЗУ, позволяющих опросить все слова неисправной зоны.

Это позволяет произвести неразрядное суммирование но модулю 2 неисправного слова со всей заданной зоной ЗУ, содержащей это слово (в том числе и с контрольной суммой). Сигналом окончания суммирования служит сигнал переполнения соответствующих разрядов счетчика команд.

После окончания суммирования схема управления вырабатывает сигнал, закрывающий входные вентили 4, и открывает вентили 6, что позволяет переписать исправленную информацию в регистр памяти.

Одновременно вырабатывается сигнал переписи адреса отказавшей ячейки из регистра памяти устройства приоритетного прерывания в счетчик команд, сигнал, снимающий блокировку микрооперации, и потом схема управления закрывает выходные вентили 6.

Таким образом выполняется возврат в задачу и продолжается нормальное ее выполнение.

В предлагаемом устройстве может быть использована любая схема контроля информации на правильность считывания.

Предмет изобретения

Устройство для контроля информационного

тракта «заноминающее устройство команд - процессор, содержащее схему контроля на четность, соединенную с выходным регистром запоминающего устройства, и схему управления, вход которой подключен к выходу схемы

контроля на четность, входные и выходные вентили, отличающееся тем, что, с целью повыщения надежности работы устройства, в него введен сумматор по модулю 2, счетный вход каждого разряда которого соединен с выходом

входных вентилей, первые входы которых соединены со схемой управления, а вторые с

выходным регистром запоминающего устройства, выходы сумматора по модулю 2 соединены со входами выходных вентилей, вторые

входы которых соединены со схемой управления, а выходы - со входом выходного регистра запоминающего устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков памяти | 1979 |

|

SU771733A1 |

| Устройство для контроля информационного тракта "запоминающее устройство команд-процессор | 1980 |

|

SU1005060A2 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1026165A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU942164A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

| Запоминающее устройство с исправлениемОшибОК | 1979 |

|

SU842979A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Устройство для задания программы | 1979 |

|

SU862118A1 |

| Микропрограммное устройство с контролем переходов | 1977 |

|

SU711573A1 |

| Запоминающее устройство с коррекцией ошибок | 1978 |

|

SU744740A1 |

Авторы

Даты

1973-01-01—Публикация