1

Изобретение относится к запоминающим устройствам.

Известно устройство, содержащее накопитель, схему контроля для проверки каждого выходного слова, схему для записи- сигнала ощибки, цепи для автоматической идентификации неправильного бита l .

Недостатком данного устройства являются большие аппаратурные затраты. ю

Наиболее близким по технической сущности к предлагаемому является запоминающее устройство с BBTOHOMHbnvi контролем, содержащее накопитель, регистр числа, блок свертки по модулю два, сумма- is тор, регистр контрольного слова и блок анализа количества единиц.

В устройстве при записи информации в сумматоре формируется контрольное слово, которое затем пересылается в ре- 20 гистр контрольного слова. В рехлмб считывания с помощью блока свертки по мо-; дулю два производится контроль считьшаемых слов и в случае сбоев производится поочередное считывание всех слов из массива информации накопителя и сложение их с кoнтpoльньпvI словом в сумматоре. При этом в сумматоре образуется слово, содержащее нули в разрядах, соответствующих разрядам запоминающего устройства (ЗУ), в которых нет ощибки или есть ощибки четной кратности и единицы в разрядах, где есть ощибки нечетной кратности. Одиночная ошибка исправляется считыванием слова с ошибкой из накопителя, сложением его с содержанием сумматора и записью его по прежнему адресу в накопитель Г 2 .

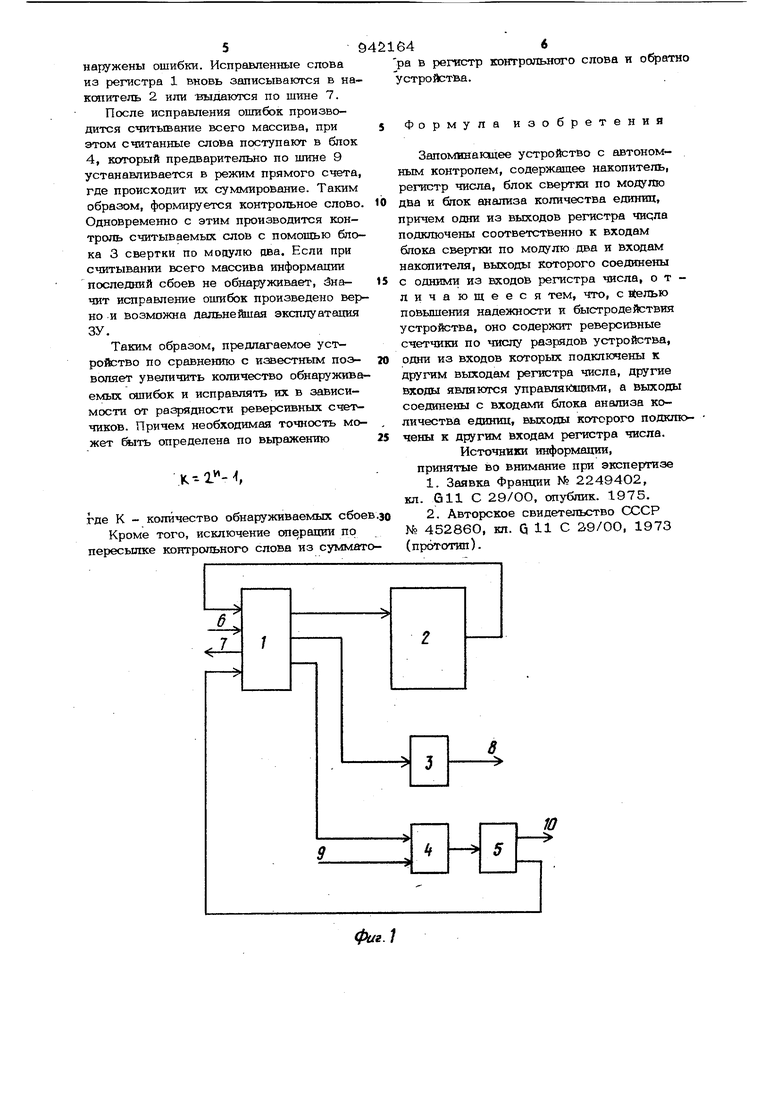

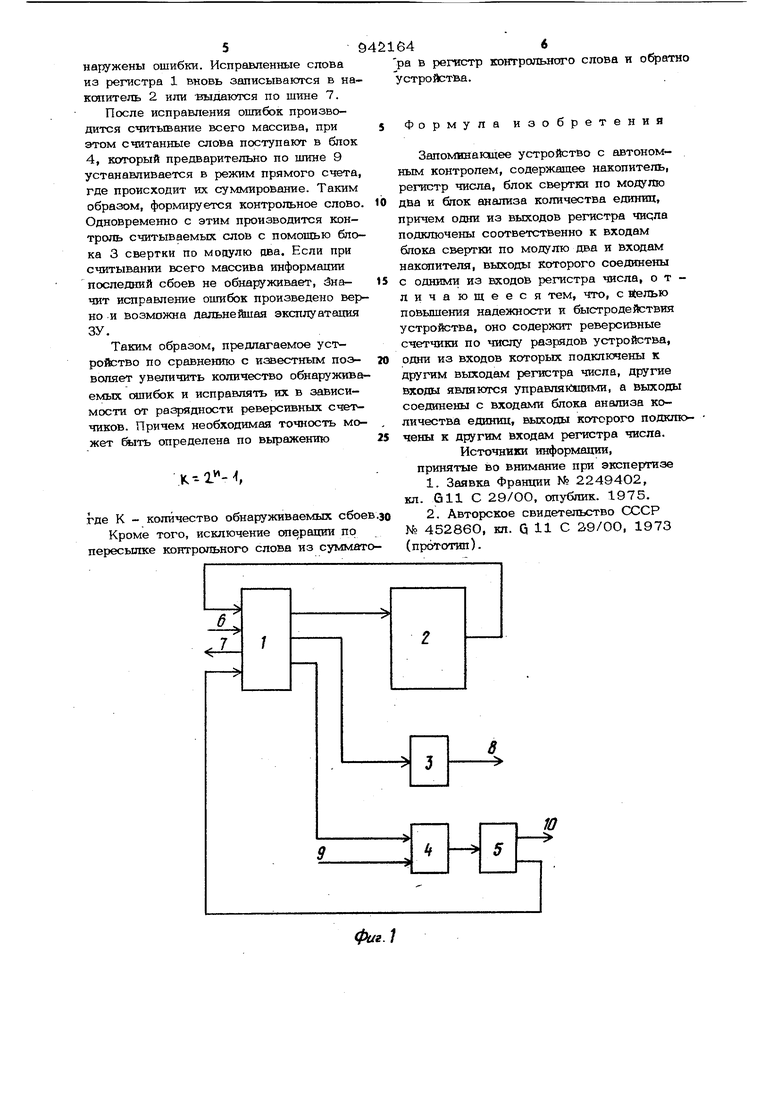

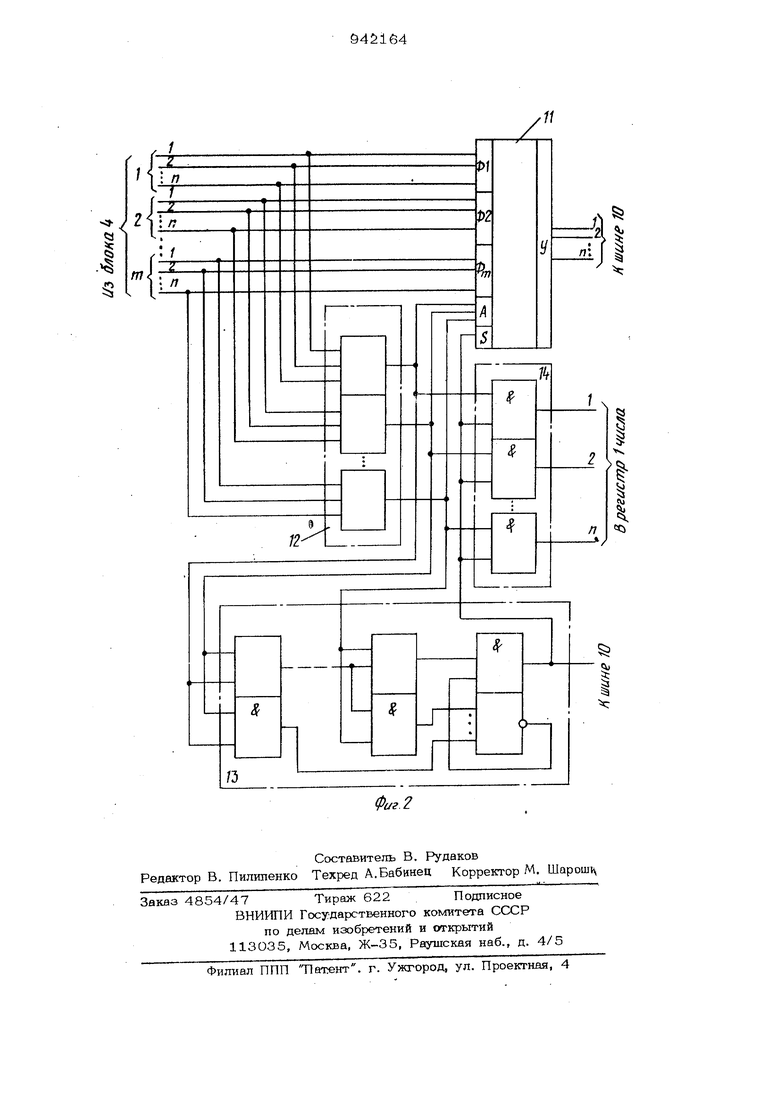

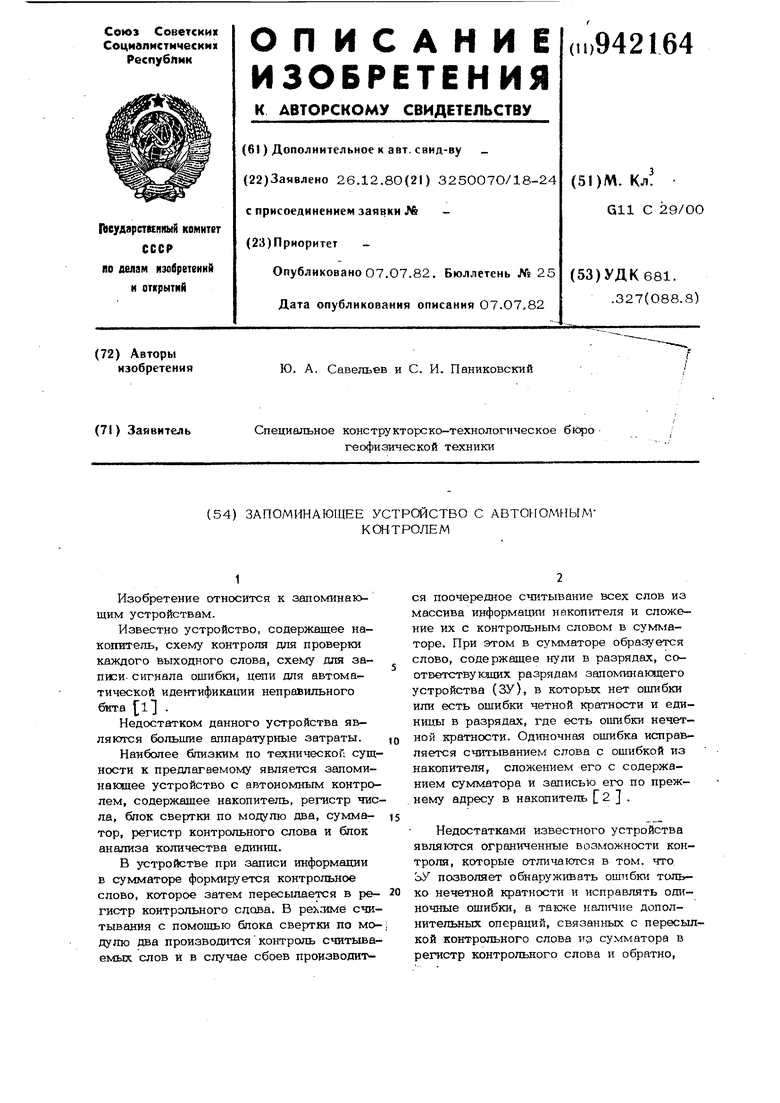

Недостатками известного устройства являются ограниченные возможности контроля, которые отличаются в том. что оУ позволяет обнаруживать ошибю только нечетной кратности и исправлять одиночные ощибки, а также нал11чие дополнительных операций, связанных с пересылкой контрольного слова кр сумматора в регистр контрольного слова и обратно, что снижает надежность и быстродействие устройства. Цель изобретения - повьЕпение надеж ности устройства, сокращение количества оборудования и повышение быстродействия устройства. Поставленная цель достигается тем, что в запоминающее устройство с автоматным контролем, содержащее накопитель, регистр числа, блок свертки по мйдулю два и блок анализа количества единиц, причем одни из выходов регистр числа подключены соответственно к входам блока свертки по модулю два и входам накопителя, выходы которого соединены с одними из Входов регистра числа введены реверсивные счетчики по числу разрядов устройства, одни из входов которых подключены к другим выходам регистра числа, другие входы являются управляющими, а выходы соединены с входами блока анализа количества единиц, выходы которого подключены к другим входам регистра числа. На фиг. 1 изображена функциональная схема запоминающего устройства с автоно ушым контролем; на фиг. 2 структурная схема блока анализа количества единиц. Устройство (фиг. 1) содержит регист 1 числа, накопитель 2, блок 3 свертки по модулю, два, И-разрядные реверсивн счетчики, объединенные в блок 4 (где М7/1), блок 5 анализа количества едшгац Регистр 1 имеет входные 6 и выходные 7 кодовые шины числа, блок 3 свертки по модулю два - выходную шину 8, блок 4 - входную шину 9 управления ревер сом, блок 5 анализа числа единиц - выходную шину 1О. Блок 5 содержит (фиг. 2) мультиплексор 11 кодов ошибо узел 12 объединения единиц, узел 13 формирования команд и выходной ключ 1 Устройство работает следующим образом. При записи по выбранному адресу первоначального считывается ранее запи санное слово из накопителя 2 в регистр 1. Одновременно с этим по шине 9 подается команда, которая подготавливает блок 4 к реверсному режиму работы. За тем проверяется четность слова с помощью блока 3 сзертю по модулю два при появлении на шине 8 сшнала об отсутствии ошибки считанное слово из регистра 1 пересылается в блок 4, где происходит его вычтание из контрольного слова, храняшегос;я в блоке 4. Записьшаемое слово поступает по входной кодовой шине числа 6 в регистр 1, Одновременно с этим по шине 9 подается команда, которая подготавливает блок 4 к режиму прямого счета. Затем записываемое слово из регистра 1 передается и записывается по ранее выбранному адресу в накопитель 2 и переписывае-1х;я в блок 4, где оно складывается с контрольньп словом. Таким образом, формируется контрольное слово для массива слов ЗУ. ,При считывании из накопителя 2 слово поступает в регистр 1, после чего с помошью блока 3 проверяется отсутствие в нем ошибок. Если слово считано с ошибкой, блоком 3 вырабатывается сигнал ошибки, который по шине 8 выдается из ЗУ в устройство, формирующее адреса записи и считывания, для запоминания адреса сбоя (не показано). По шине 9 по; ается команда реверса. После этого производится поочередное считывание всех слов из накопителя 2 и вычитание их из контрольного слова, хранящегося в блоке 4. В случае, если при этом воэникаюгг сбои, блоком 3 вырабатываются сигналы ошибки для управления запоминанием адресов сбоев. После считывания всего массива информации в блоке 4 образуется код, содержащий группы нулей в счетчиках, соответствующих разрядам ЗУ, в которых нет ошибок или есть ошибки кратности VI , или комбинация единиц в разрядах, где произошли ошибки, число которых не равно кратности У{ . Количество сбоев определяется в блоке 5 анализа количества единиц, куда контрольное слово передается из блокл 4. Если количество сбоев, поступивших с блока 3 свертки по модулю два, соответствует числу лишних единиц, выявленных блоком 5 анализа -количества единиц, то произошло исчезновение единиц в данном разряде слова; если количество сбоев соответствует числу недостающих единиц, значит произошло накопление ложные: единиц. В двух случаях производитсй исправление ошибок по адресам, поступающим в ЗУ из устройства, в котором было произведено запоминание адресов сбоев. При этом слова с ошибками считьюаются из накопителя 2 в регистр 1. Затем по сигналам, поступающим из блока 5 анализа количества единиц, в регистре 1 производится их исправление путем инвертирования информации в разрядах, где были обнаружены ошибки. Исправленные слова из регистра 1 вновь записываются в накопитель 2 или -выдаются по шине 7. После исправления ошибок производится считьгоание всего массива, при этом считанные слова поступают в блок 4, ксугорый предварительно по шине 9 устанавливается в режим прямого счета, где происходит их суммирование. Таким образом, формируется контрольное слово Одновременно с этим производится контроль считываемых слов с помощью блока 3 свертки по модулю два. Если при считывании всего массива информашга последний сбоев не обнаруживает, Значит исправление ошибок произведено вер но и возможна дальнейшая эксплуатация ЗУ. Таким образом, предлагаемое устройство по сравнению с и жестным позволяет увеличить количество обнаружива емых ошибок и исправлять их в зависимости от разрядности реверсивных счетчиков. Причем необходимая точность может определена по выражению , где К - количество обнаруживаемых сбое Кроме того, исключение операции по пересылке контрольного слова из суммат 9 644 ра в регистр контрольного слова и обратно устройства. Формула изобретения Запоминакщее устройство с автономным контролем, содержащее накопитель, регистр числа, блок свертки по модулю два и блок анализа количества единиц, причем одни из выходов регистра чидла подключены соответственно к входам блока свертки по модулю два и входам накопителя, выходы которого соединены с одними из входов регистра числа, отличающееся тем, что, с йелью повышения надежности и быстродействия устройства, оно содержит реверсивные счетчики по числу разрядов устройства, одни из входов которых подключены к другим выходам регистра числа, другие входы являются управлянлцими, а выходы соединены с входами блока анализа количества едишщ, выходы которого ПОДКЛКУчены к другим входам регистра числа. Источники информашга, принятые во внимание при экспертизе 1.Заявка Франции № 2249402, кл. Q11 С 29/ОО, опублик. 1975. 2.Авторское свидетельство СССР № 452860, кл. Q 11 С 39/ОО, 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1983 |

|

SU1081669A1 |

| Запоминающее устройство с автономным контролем | 1973 |

|

SU452860A1 |

| Устройство для обнаружения и исправления ошибок в блоке памяти | 1980 |

|

SU888213A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1048520A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2008 |

|

RU2384899C2 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1157575A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU926726A1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1987 |

|

SU1481863A1 |

8

фиг.1

//

/

Авторы

Даты

1982-07-07—Публикация

1980-12-26—Подача