/ 1

Из вестнЫ аиалого-цифровые преобразователи, содержащие сравнивающее устройство, соединенное с выходом цифро-аналогового Преобразователя, регистр - ре1Вбрсивный счетчик со схемами «ИЛИ на сумгмирующем и вычитающем входах, одновнбратор и блокуправлелйя, обеспечивающий режим комбимированного преойразо ва1НИЯ с поразрядйьш и следящим уравновешиванием. Такие преобразователи не обладают свойством помехозащИщеияости.

В помехозащищенных аиалого-цифровых преобразователях используются интегрирование входного сигнала, способ синхронного детектирования, способ выделения и суммирования инвертированной помехи. Однако все они требуют специальных прецизионных аналоговых узлов (операционных усилителей, компараторов и т. д.) и узлов выделения периода помехи, что усложняет их реализацию и снижает скорость работы. Этот недостаток сильнее всего оказывается в многоканальных преобразователях, предназначенных для работы в системах, где входные сигналы различных каналов лодвержоны помехам, отличающимся по частоте и амплитуде.

Цель изобретения - увеличение помехозащищенности аналого-цифрового преобразователя. Это достигается введением логической схемы определения изменения знака приращения ураШновещивающего сигнала, дополнительного реве,рси1В1Ного счетчика и схемы разрешвния счета, одвн вход которой соединен с выходом логической схемы определения знака приращения уравновешивающего сигнала, а два других - с выходами блока управления, с двумя входами логической схемы определения изменения знака приращения уравновешивающего сигнала и с двумя входами схем,

«ИЛИ. Выходы схемы разрещения счета соединены с суммирующим и вычитающим входами дополните льного реверсииного счетчика, суммирующий и вычитающий входы второго младщего разряда которого подключены к

выходам блока управления и к соответствующим вторым входам схем «ИЛИ, а выход старщего разряда соединен с входом блока управления.

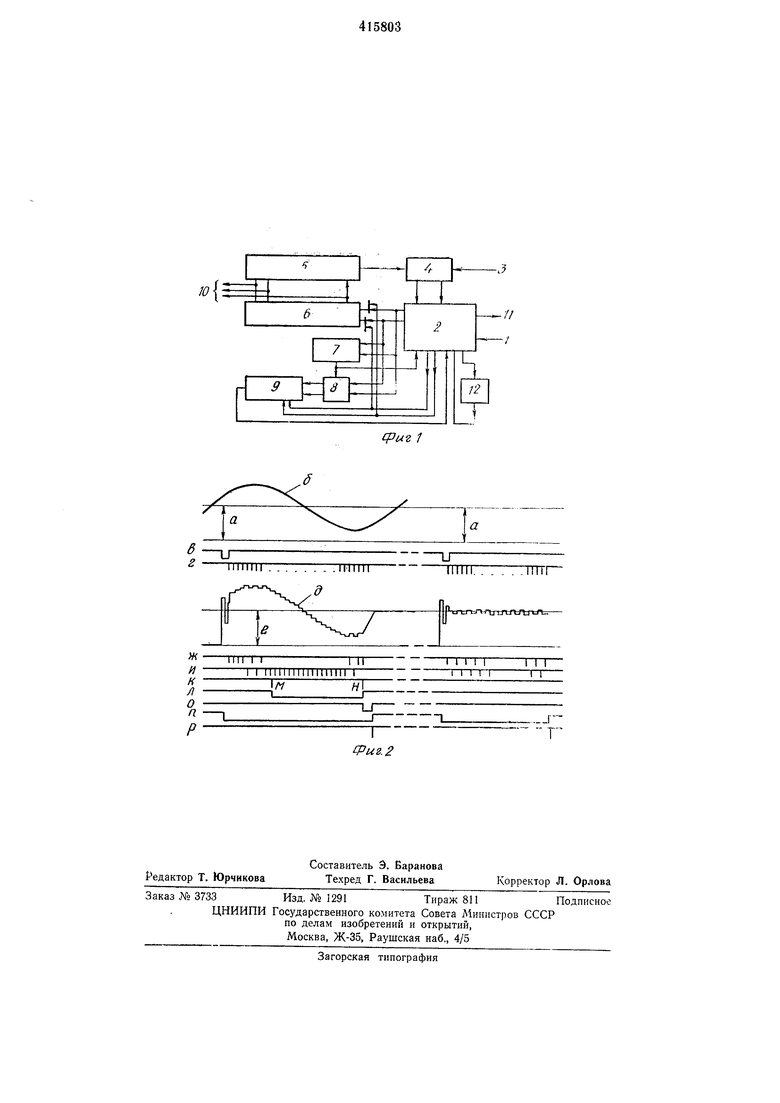

На фиг. 1 изображена блок-схема предлагаемого ареобразователя; на фиг. 2 - временная диаграмма его работы.

По сигналу начала преобразования, поступающему на вход / блока 2 управления, начинается выполнение поразрядного уравновещивания поступающего на вход 3 сравнивающего устройства 4 входного сигнала а (см. фиг. 2) с наложенной помехой б. Оно продолжается в течение длительности импульсов в. После этого от блока управления начинают поступать импульсы г для режима еледящего уравновешивания. Входной сигнал с наложенной помехой уравновешивается сигн-алом д, при этом уравновешивающий сигнал, йоответ1Ствующий Ьходному сигналу а, равен уровню е. Ураонавешивающий сигнал подается с выхода цифро-аналогового преобразователя 5, подключенного к регистру - реверсивному счетчику 6. В режиме слежения блок управления вырабатывает импульсы ж при увеличении ура(В1навеши1вающего сигнала д или И|М:пульсы и при его уменьшении. Из этих и1М1пульсав логическая схема 7 определения изменения знака формирует импульсы к в моменты появления второго ггоследующе Го KBaiHTa одного знака, противоположного злаку предшествующего изменения уравновешивающего сигнала. По сигналу от схемы 7 схема 8 разрешает прохождение импульсов ж илИ и в дополнительный реверсивный счетЧИ1К 9. Эти имтульсы подсчитываются в течение времени л, определяемого моментами м и « появления лмлульсов последовательности к. По окончании счета в момент м блок управления вырабатывает импульсы подсчета для счетчиков 5 и 5. Пересчет продолжается в течение времени о. Причем, чтобы код в счетчике 9 при пересчете был уменьшен вдвое, эти Импульсы подаются во второй младший разряд, в отличие от режима подсчета, когда импульсы ж или и поступают на первый младший разряд. При переполнении счетчика 9 пересчет заканчивается и в счетчике 6 получается скорректированный результат преобразования, в котором исключены погрешности от помехи и который снимается с выходов 10. Бели величина помехи .не вызывает изменения уравновешивающего оигаала более, чем на один квант, то преобразование заканчивается через интервал времени, равный половине периода помехи после начала преобразования. В этом случае форми,рова,н1ие им-пульсов п, в течение которых осуществляется преобразование, и форМИраваиие сигнала окончания преобразования р, выдаваемого с выхода //, осуществляется по сигналам оДновибратора 12.

ТаКИ|м образом, данная схема обладает помехозащищенностью и преобразование в

ней выполняется за время периода помехи, наложенной на входной сипнал. При этом длительность -преобразова1ния автоматически устанавливается в соответствии с частотой помехи, если она превыщает величину кванта. При а1мнлитуде помехи, меньшей кванта, время преобразования автоматически уменьшается.

Предмет изобретения

Аналого-цифровой преобразователь, содержащий сравнивающее устройство, соединенное с выходом дифро-а1налогового преобразователя, регистр - реве,рси1вный счетчи.к со

схемами «ИЛИ на суммирующем и вычитающем входах, одновибратор и блок управления, обест1ечивак щий режим ком1бИ|Нированного преобразования с поразрядным и следящим уравновешиванием, отличающийся тем, что, с

целью увеличения помехозащищенности, он содержит логическую схему определения изменения 31нака лрэращения уравн-овешивающего сигнала, дополнительный реверсивный счетчик и схему разрещения счета, одвн вход

которой соединен с выходом логической схемы определения знака приращ-ения уравновешиваюшего сигнала, а два других - с выходами блока управления, с двумя входами логической схемы определения изменения знака

приращения уравновеш.ивающего сигнала и с двумя входами схем «ИЛИ, выходы схемы разрещения счета соеди1нены с суммирующим и вычитающим входами дополнительного реверсивного счетчика, су1М|Мирующий и вычитающий входы второго младшего разряда которого подключены к выходам блока управления и к соответствующи/м вторым входам схем «ИЛИ, а выход старшего разряда соедннен с входом блока управления.

}pT3-t3T rvitrtrtft rtrtrt ж и к л о п

м

р

1 1 ТТ IIT

I

fpuz.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный аналого-цифровой преобразователь | 1974 |

|

SU493911A2 |

| СПОСОБ УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2020724C1 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ ПОМЕХ | 1990 |

|

RU2074516C1 |

| Преобразователь напряжения в код | 1980 |

|

SU884126A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU873405A1 |

| СЛЕДЯЩИЙ АЦП МНОГОРАЗРЯДНЫХ ПРИРАЩЕНИЙ | 2016 |

|

RU2619887C1 |

| Аналого-цифровой преобразователь | 1976 |

|

SU661783A1 |

| Аналого-цифровой преобразователь знакопеременных сигналов | 1987 |

|

SU1483641A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU1003331A1 |

| Комбинированный аналого-цифровой преобразователь | 1986 |

|

SU1367157A1 |

Даты

1974-02-15—Публикация

1971-02-08—Подача