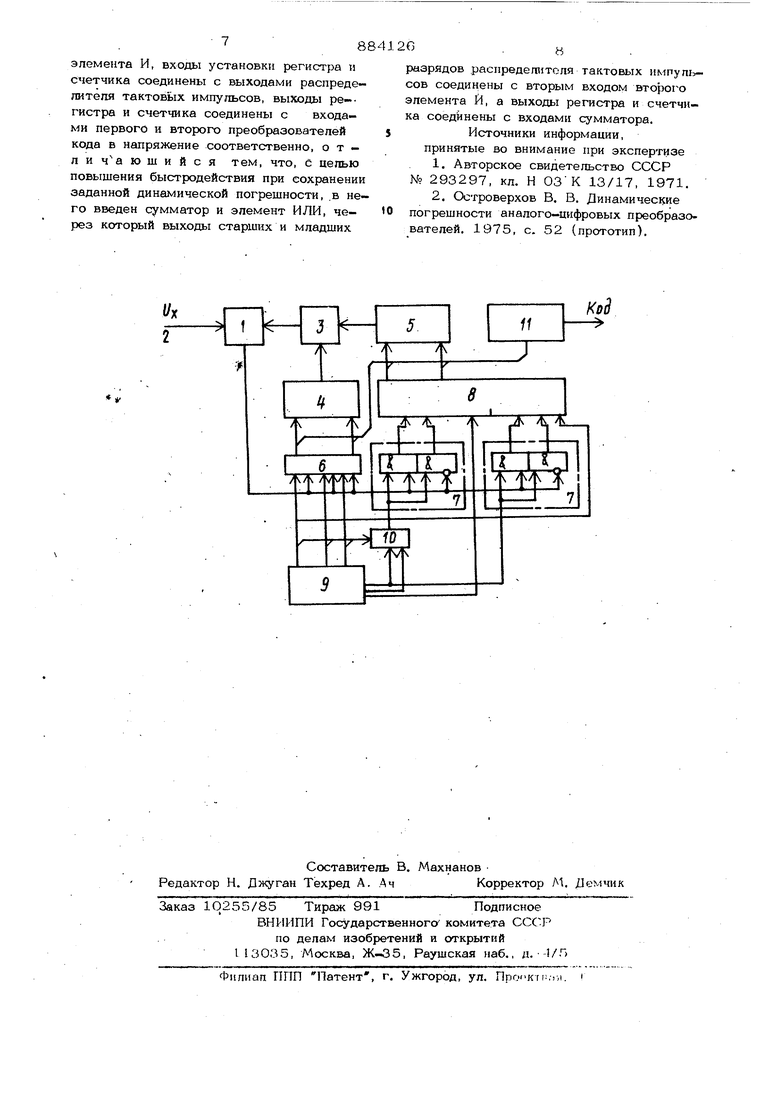

(54) ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В КОД Устройство относится к измерительной и вычислительной технике и может быть использовано в различных информационноизмерительных системах. Для расширения полосы частот преоб разуемых напряжений при сохранении заданной динамической погрешнорти используют преобразователи напряжения в код поразрядного уравновешивания с последовательной коррекцией динамической погрешности, выполняемой начиная с некоторого такта уравновешивания.V Известен преобразователь напряжения в код, содержащий блок сравнения, вход которого соединен с входной ши ной источника измеряемого сигнала, вто рой вход блока сравнения соединен с выходом блока суммирования напряжений, входы которого соединены с выходами пер вого и второго преобразователей кода в напряжение, выход блока сравнения соеди- иен с входами управления регистра-счетчика .и первым входом элемента И, выход КОТ011ОГО соединен с входом сложения ре- гистра-счетчика, .вход управления элемента И, входы установки первого преобразователя кода в напряжение и регистра-счетчика соединены с выходами распределителя тактовых импульсов, выходы регистра счетчика соединены с входами второго преобразователя кода в напряжение l. Недостатками устройства являются значительная величина динамической погрешности, которая.возникая в тактах коррекции и при определении младших разрядов кода, не устраняется, а также низкое быстродействие при сохранении заданной динамической погрешности, вследствие выполнения значительного числа дополнительных тактов уравновешивания для коррекции динамической погрешности Известен также преобразователь напряжения в код, содержащий блок сравнения, первый вход которого соединен с входной шиной источника измеряемого сигнала, второй вход блока сравнения соединен с выходом блока суммирования напряжений входы которого соединены с выходами перврго и второго преобразователей кода в напряжение, выход блока сравнения соединен с входами управления регистра и первыми входами двух элементов И, выходы которых соединены с входами ело- жёния и вычитания счетчика, второй вход первого элемента И, входы установки регистра и счетчика соединены с выходами распределителя тактовых импульсов, выходы регистра и счетчика соединены с входами первого и второго преобразователя кода в напряжение, соответственно 2. Однако устройство обладает низким быстродействием при сохранении заданной динамической погрешности, так как велико число дополнительных тактов для коррекции динамической погрешности. Кроме того, длительность каждого такта уравновешивания в данном устройстве увеличивается за счет дополнительной задержки сигналов в регистре и счетчике при прохождении по элементам сложения и вы читания и должна включать время распространения переноса единицы. При коррекции динамической погрешнос ти в младшем разряде, время распространения переноса при разрядности преобразователя VI составляет (-i ) С / где Т время распространения переноса на 1 разряд. Целью изобретения является повышение быстродействия при сохранении задан ной дина;мической погрешности. Цель достигается тем, что в преобразователь напряжения в код, содержащий блок сравнения, первьхй вход которого со динен с входной шиной источника измеряемого сигнала, второй вход блока срав нения соединен с выходом блока суммиро вания напряжений, входы которого соединены с выходами первого и второго пре образователей кода в напряжение, выход блока сравнения соединен с входами управления регистра и первыми входами двух элементов И, выходы которых соединены с входами сложения и вычитания счетчика, второй вход первого элемента И, входы установки регистра и счетчика соединены с выходами распределителя тактовых импульсов, выходы регистра и счетчика соединены с входами первого и второго преобразователей кода в напряжение соответственно, введен сумматор я элемент И ЛИ, через который выходы старших и младших разрядов распределителя тактовых импульсов соединены с вторым входом второго элемента И, а вы ходы регистра и счетчика соединены с входами сумматора. На чертеже приведена структурная электрическая схема устройства. Устройство содержит блок 1 сравнения, шину 2 источника измеряемого сигнала, блок 3 суммирования напряжений, преобразователи 4 и 5 кода в напряже - ние, регистр б, элементы И 7, счетчик 8, распределитель 9 тактовых импульсов, элемент ИЛИ 10 и сумматор. 11. Устройство работает следующим образом. При одинаковой допустимой скорости изменения сигнала во всех (кроме тактов определения младших разрядов кода) тактах уравновешивания гае IQ масштаб преобразования напряжения, веса разрядов и в тактах уравновешивания и i для учета возможного изменения сигнала должны удовлетворять соотношению a,, .Q Для равном 1, и разрядности устройства W1, равном 10, веса разрядов ; кода по тактам уравновешивания составляют 514, 258, 130, 66, 34, 18, 10, 6, 6, 4, 3, 2, 1. Веса разрядов (кроме двух младших) кода по сравнению с весами разрядов традиционных устройств преобразования поразрядного уравновешивания увеличены на величину 2 , Уравновешиваюшие напряжения формируются соответственно этим весам разрядов кода. Чтобы учесть возможное уменьшение сигнала, шкала уравновешивающих напряжений в каждом такте уравновешивания смещается на величину т квантов напряжения младшего разряда кода. В устройстве уравновешивающее напряжение 0)pi по тактам уравновешивания изменяется по выражению :,.w,k.S2X.i-)-wioS X, Первая сумма в этом выражении описывает работу традиционного преобразователя напряжения в код поразрядногх) ypai новешивания, вторая сумма учитывает необходимое увеличение веса разряда кода и смешение шкаль уравновешивающих налря)кений. Младшие разряды кода участвуют в работе устройства 2 раза в соста58ве весов разрядов кода 4 (2+2) и 3 (1+2) и с естественными весами 2 и 1. В устройстве блок 1 сравнения, блок 3 суммирования напряжений, преобразова тель 4 кода в напряжение, регистр 6 образуют преобразователь напряжения в код поразрядного, уравновешивания. Преоб разователь 5 кода в напряжение, счетчик 8, элементы И 7 и ИЛИ 10 используются для задания искусственного порядка весов разрядов кода. Вес уравновешивающего напряжения образуется весом раз - ряда регистра 6 и кодом в счетчика 8, состояние разрядов регистра 6 и счетчика 8 меняются одновременно по сигналам из блока 1 сравнения и распределителя 9 тактовых импульсов. Сумматор 11 форми рует результат по кодам в регистре 6 и счетчике 8. В первом такте уравновешивания в старший разряд регистра 6 заносится еди ница, в остальные разряды регистра 6 нули, в счетчике 8 устанавливается код 0001. На выходе блока 3 суммирования напряжений выдается напряжение Uyp равно 513 квантам напряжения. В блоке 1 сравнения сравниваются напряжения U и U |Pi/ Если Ox UypjB регистре 6 сохраьяется код данного такта уравновешивания, в начале следующего такта у равновещивания в счетчик 8 добавляется еди ница. В случае (Jj(l,pP начале следующего такта уравновешивания сбрасывается последняя единица кода в регистре 6, из кода в счетчике 8 вычитается единица. Изменением содержимого счетчика 8 отслеживаются изменения преобразуемого сигнала. В данном устройстве отслеживание по времени с тактами поразрядного уравновешивания напряжения. регистре 6 сохраняется единица в старшем разряде. В начале вто рого такта уравновешивания в счетчик 8 через элемент ИЛИ 1О и второй элемент И 7 добавляется единица. После занесе- ния единицы в следуклдем разряде регистра 6 аналоговь1й блок 3 суммирования на напряжений выдает напряжение 513+256+1 78О квантов напряжения. Уравновешивакяцее напряжение в этом случае увеличено на 2 кванта напряжения чтобы учесть возможное изменение сигнала за время первых двух тактов уравновешивания. Если (J)( vps. следуюшем такте уравновешивания устанавливается з, 513+128-«-1 64О квантов напряжения. Происходит новое сравнение напряжений (Jx формирование кодовв регистре 6 и счетчике 8. Ана64логично устройство работает во время .остальных тактов уравновешивания. В 11 такте уравновешивания при переходе от разряда уравновешивания с весом 3 к разряду уравновешивания с весом 2, одновременно работают оба элемента И 7. Уравновешивающее напряжение меняется на J: 1,5 квантов напряжения, в зависимости от рюзультата сравнения. Этим достигается уменьшение динамической погрешности на 0,5 кванта напряжения. Определение младшего разряда кода выполняется в 12 такте через пер.вый элемент И 7. Разрядность счетчика 8 N-Bogf/ Cn-l J-f - Увеличение разрядности на единицу учитывает необходимость иметь в счетчике 8 знаковый разряд для отображения напряжения изменения сигнала. Разрядность счетчика 8 не более 5 разрядов. Код результата преобразования снимается с выхода сумматора 11. По соотношению (1) можно определить веса разрядов кода для других допустимых скоростей изменения сигнала. Например, для KY - 2 по тактам уравновешивания веса разрядов коды должны быть следующими: 516. 260, 132, 68, 36, 20, : 12, 8, 6, 5, 4, 3, 2, 1. Необходимое увеличение веса разряда кода достигается в этом случае подключением второго элемента И 7 ко входам сложения и вычитания разряда счетчика с весом 2, другие элементы И 7 подключаются к соответствующим входам сложения и вычитания разрядов счетчика с меньшими весами. Для k 2 применение преобрюзовате- ля напряжения в код с последовательной коррекцией из-за резкого возрастания динамической погрешности нецелесообразно. Формула изобретения Преобразователь напряжения в кЬд, содержащий блок сравнения, первый вход которого соединен со входной шиной источника измеряемого сигнала, второй вход блока сравнешя соединен с выходом блока суммирования напряжений, входы котоого соединены с выходами первого и вто ого преобразователей кода в напряжение, ыход блока сравнения соединен; со ходами управления регистра и первыми ходами двух элементов И, выходы кото ых соединены с входами сложения и выитания счетчика, второй вход перього

элемента И, входы установки регистрза и счетчика соединены с выходами распределителя тактовых импульсов, выходы ре-гистра и счетчика соединены с входами первого и второго преобразователей кода в напряжение соответственно, о т личаюшийся тем, что, с целью повышения быстродействия при сохранении заданной динамической погрешности, .в него введен сумматор и элемент ИЛИ, через который выходы старших и младших

разрядов распределителя тактовых импул1 сов соединены с вторым входом второго элемента И, а выходы регистра и счетчика соединены с входами сумматора.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР

№ 293297, кл. Н 03К 13/17, 1971.

2.Островерхов В. В. Динамические погрешности аналого-цифровых преобразователей. 1975, с. 52 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1979 |

|

SU782147A2 |

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1976 |

|

SU660240A1 |

| Аналого-цифровой преобразователь с коррекцией динамической погрешности | 1987 |

|

SU1607076A1 |

| Г. Г. ЖИВИЛОБ; ::-.:;B::^ji03MAfl'1!^'а:гни кя,;^^'^?-кАЯ'Ч.'г. | 1972 |

|

SU324705A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU1018227A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU884127A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С КОРРЕКЦИЕЙ СЛУЧАЙНОЙ ПОГРЕШНОСТИ | 1991 |

|

RU2024193C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1972 |

|

SU330538A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

| Преобразователь напряжения в десятичный код | 1982 |

|

SU1072260A1 |

Авторы

Даты

1981-11-23—Публикация

1980-02-13—Подача