(54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU900438A2 |

| Следящий аналого-цифровой преобразо-ВАТЕль | 1979 |

|

SU805489A1 |

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU900437A2 |

| Следящий аналого-цифровой преобразова-ТЕль | 1979 |

|

SU828401A1 |

| Следящий аналого-цифровой преобразователь | 1984 |

|

SU1184090A1 |

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU892702A1 |

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU907795A1 |

| Следящий аналого-цифровой преобразователь | 1979 |

|

SU799129A1 |

| Следящий аналого-цифровой преобразователь | 1988 |

|

SU1580555A1 |

| Цифровой регистратор | 1984 |

|

SU1164549A1 |

Изобретение относится к аналогецифровьам преобразователям и может быть использовано в обл;асти связи, вычислительной и измерительной технике, а также в автоматизированных системах управления технологическими процессами и системах автоматизации научных исследований.

Известно устройство аналого-цифрового преобразования по принципу поразрядного уравновешивания, содержащее йифроаналоговый преобразователь, счетный триггер, схему сравнения, блок управления, реверсивный счетчик, схемы совпадения, инвертор и формирователь импульсов, обеспечивающее сравнение сигнала рассогласования со значением эталона разряда, следующего за опрашиваемым. Если сигнал рассогласования меньше ука;занного эталона, то осуществляется коррекция образцового сигнала шагом, соответствующим опрашиваемому разряду un.

Недостатком такого аналого-цифрового преобразователя является не-, возможность обработки сигнала рассогласования в случае, если приращение входного сигнала за такт больше.

чем значение эталона на данном такте.

Известен аналого-цифровой пре5 образователь, содержащий схему сравнения, цифроаналоговый преобразователь, реверсивный счетчик, распределитель импульсов, генератор импульсов, триггер управления и эле10 мент И Г2.

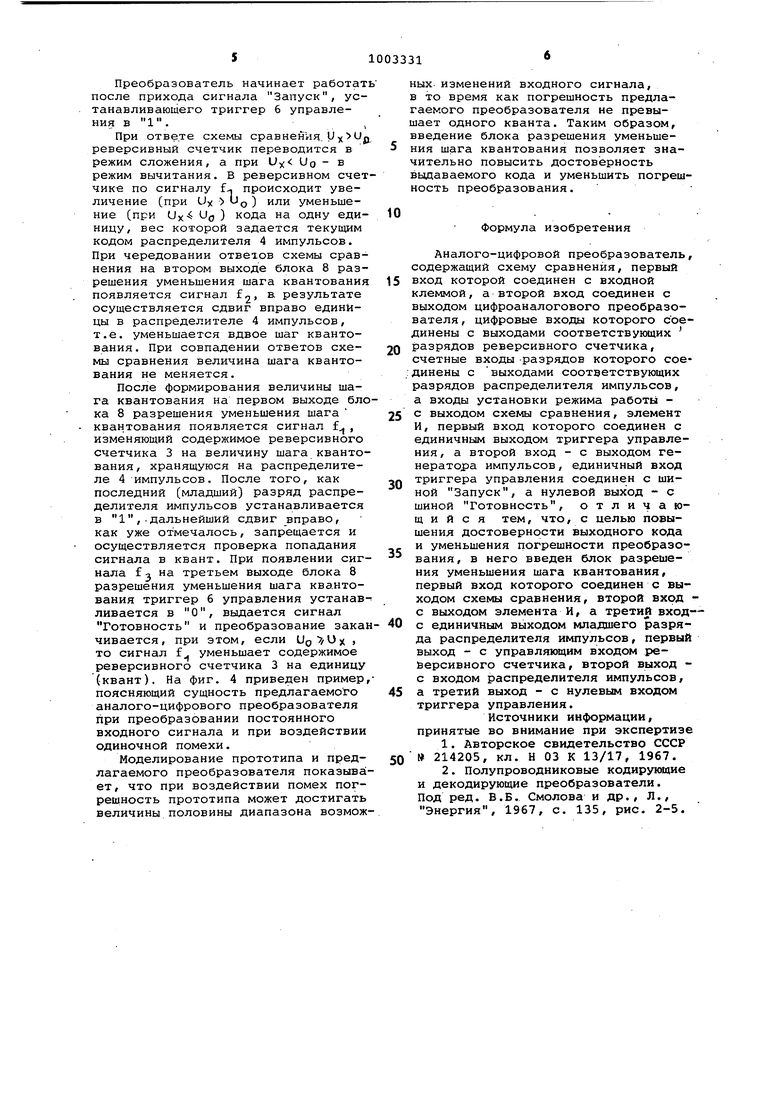

Недостатком устройства является, низкая достоверность выходных крдоб и большая погрешность преобразования, обусловленные тем, что величи15на шага квантования уменьшается вдвое на каждом такте независимо от ответов схе2иы сравнения, тем самым не учитывается.возможность изменения взаимного расположения входного

20 сигнала и ранее сформированных образцовых уровней. Однако часто изза различных сбоев, помех и утечек взаимное расположение образцового уровня и входного сигнала определя25ется неверно, что ведет к уменьшению достоверности и увеличению погрешности.

Цель изобретения - повышение достоверности выходного кода и умень шение погрешности преобразования.

Поставленная цель достигается тем, что в аналого-цифровой преобразователь, содержащий схему сравнения , первый вход которой соединен с клеммой, а второй вход со динен с выходом цифроаналогового, преобразователя, -цифровые входыкоторого соединены с выходами соответствующих разрядов реверсивного счетчика , счетные входы разрядов которого соединены с выходами соответствующих разрядов распределителя им пульсов, а входы, установки режима работы - с выходом схемы сравнения, элемент И, первый вход которого соединен с единичным вь ходом триггера управления, а второй вход - с выходом генератора импульсов, единичный вход триггера управления соединен с шиной Запуск -, а нулевой выход - с шиной Готовность, введен блок разрешения уменьшения шага квантования, первый вход которого соединен с выходом схемы сравнения, второй вход - с выходом элемента И, а третий вход - с единичньам выходом младшего разряда распределителя импульсов, первый выход - с управляющим входом реверсивного счетчика, второй выход с входом распределителя импульсов, а третий выход - с нулевым входом триггера управления.

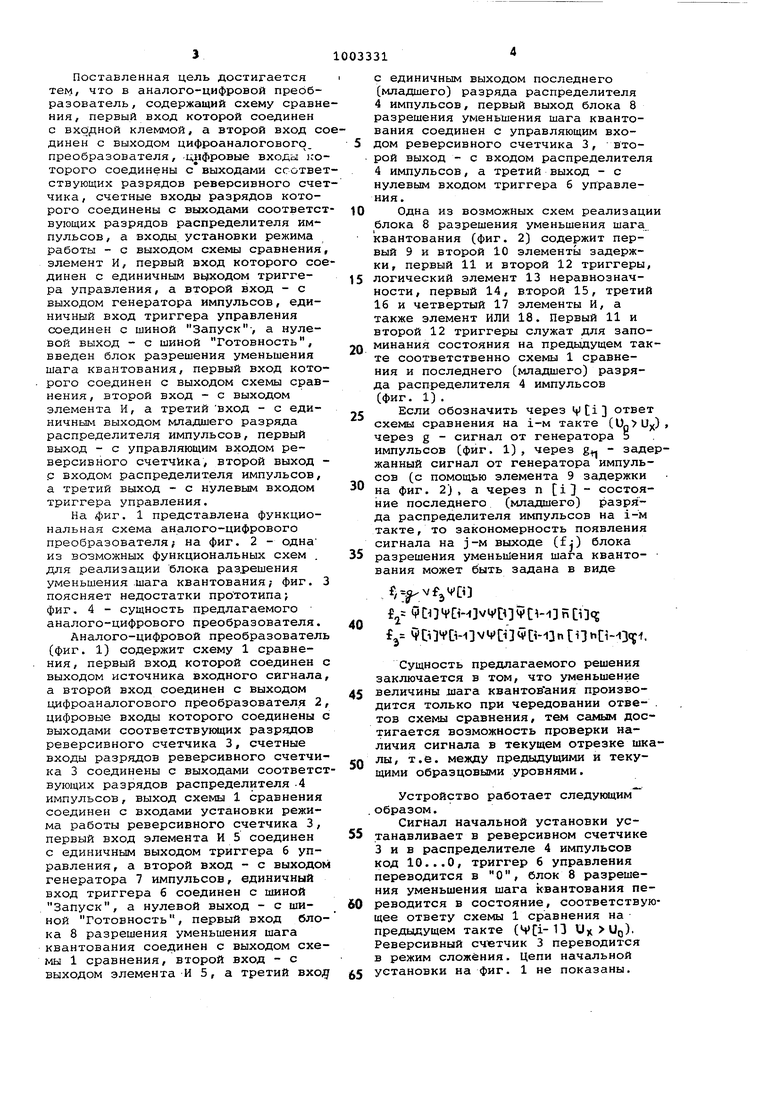

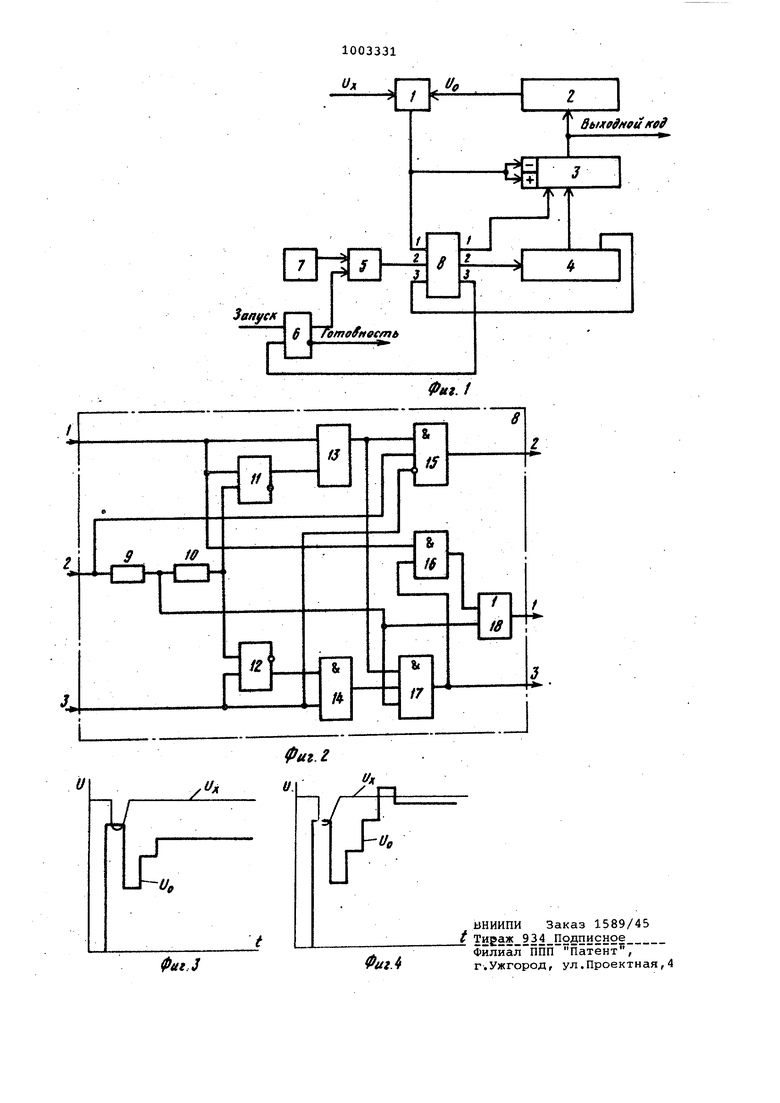

На фиг. 1 представлена функциональная схема аналого-цифрового преобразователя; на фиг. 2 - одна из возможных функциональных схем для реализации блока разрешения уменьшения шага квантования; фиг. 3 поясняет недостатки прототипа; фиг, 4 - сущность предлагаемого аналого-цифрового преобразователя.

Аналого-цифровой преобразователь (фиг. 1) содержит схему 1 сравнения, первый вход которой соединен с выходом источника входного сигнала, а второй вход соединен с выходом цифроаналогового преобразователя 2, цифровые входы которого соединены с выходами соответствующих разрядов реверсивного счетчика 3, счетные входы разрядов реверсивного счетчика 3 соединены с выходами соответствующих разрядов распределителя -4 импульсов, выход схемы 1 сравнения соединен с входами установки режима работы реверсивного счетчика 3, первый вход элемента И 5 соединен с единичным выходом триггера б управления, а второй вход - с выходом генератора 7 импульсов, единичный вход триггера б соединен с шиной Запуск, а нулевой выход - с шиной Готовность, первый вход блока 8 разрешения уменьшения шага квантования соединен с выходом схемы 1 сравнения, второй вход - с выходом элемента И 5, а третий вхо

с единичным выходом последнего (младшего) разряда распределителя 4 импульсов, первый выход блока 8 разрешения уменьшения шага квантования соединен с управляющим вхо5 дом реверсивного счетчика 3, вто рой выход - с входом распределителя 4 импульсов, а третий выход - с нулевым входом триггера б управления.

0 Одна из возможных схем реализации блока 8 разрешения уменьшения шага квантования (фиг. 2) содержит первый 9 и второй 10 элементы задержки, первый 11 и второй 12 триггеры,

5 логический элемент 13 неравнозначности, первый 14, второй 15, третий 16 и четвертый 17 элементы И, а также элемент ИЛИ 18. Первый 11 и второй 12 триггеры служат для запоQ минания состояния на предыдущем такте соответственно схемы 1 сравнения и последнего (младшего) разряда распределителя 4 импульсов (фиг. 1).

5 Если обозначить через ответ схемы сравнения на i-м такте (() через g - сигнал от генератора 5 импульсов (фиг. 1), через g - задержанный сигнал от генератора импуль сов (с помощью элемента 9 задержки

на фиг. 2), а через п i - состояние последнего (младшего) разряда распределителя и myльcoв на i-м такте, то закономерность появления сигнала на j-M выходе (j) блока

5 разрешения уменьшения шага кванто- вания может быть задана в виде

{, QCO4EiH vMp vC l nCi

3 4D HCi-i v4Ci3i i-i3n{:iihi:i-i3 f,

Сущность предлагаемого решения заключается в том, что уменьшение

величины лзага квантования производится только при чередовании ответов схемы сравнения, тем самым достигается возможность проверки наличия сигнала в текущем отрезке шкалы, т.е. между предыдущими и текущими образцовыми уровнями.

Устройство работает следуняцим образом.

Сигнал начальной установки устанавливает в реверсивном счетчике 3 и в распределителе 4 импульсов код 10...О, триггер 6 управления переводится в О, блок 8 разрешения уменьшения шага квантования переводится в состояние, соответствующее ответу схемы 1 сравнения на предыдущем такте ( х оРеверсивный счетчик 3 переводится в режим сложения. Цепи начальной установки на фиг. 1 не показаны.

Преобразователь начинает работат после прихода сигнала Запуск, устанавливающего триггер 6 управления в 1.

При ответе схемы сравнения/Уу U реверсивный счетчик переводится в режим сложения, а при U- UQ - в режим вычитания. В реверсивном счетчике по сигналу f происходит увеличение (при DX UQ) уменьшение при DX- Ufl ) кода на одну единицу, вес которой задается текущим кодом распределителя 4 импульсов. При чередовании ответов схемы сравнения на втором выходе блока 8 разрешения уменьшения шага квантования появляется сигнал f, в. результате осуществляется сдвиг вправо единицы в распределителе 4 импульсов, т.е. уменьшается вдвое шаг квантования. При совпадении ответов схемы сравнения величина шага квантования не меняется.

После формирования величины шага квантования на первом выходе блока 8 разрешения уменьшения шага квантования появляется сигнал , изменяющий содерлшмое реверсивного счетчика 3 на величину шага квантования , хранящуюся на распределителе 4 импульсов. После того, как последний (младший) разряд распределителя импульсов устанавливается в 1,.дальнейший сдвиг вправо, как уже отмечалось, запрещается и осуществляется проверка попадания сигнала в квант. При появлении сигнала 2 на третьем выходе блока 8 разрешения уменьшения шага квантования триггер 6 управления устанавливается в О, выдается сигнал Готовность и преобразование закачивается, при этом, если )( , то сигнал уменьшает содержимое реверсивного счетчика 3 на единицу (квант). На фиг. 4 приведен примерпоясняющий сущность предлагаемого аналого-цифрового преобразователя при преобразовании постоянного входного сигнала и при воздействии одиночной помехи.

Моделирование прототипа и предлагаемого преобразователя показыва ет, что при воздействии помех погрешность прототипа может достигать величины половины диапазона возможных изменений входного сигнала, в то время как погрешность предлагаемого преобразователя не превышает одного кванта. Таким образом, введение блока разрешения уменьшения шага квантования позволяет значительно повысить достоверность вьадаваемого кода и уменьшить погрешность преобразования.

Формула изобретения

Аналого-цифровой преобразователь, содержащий схему сравнения, первый 5 вход которой соединен с входной клеммой, а второй вход соединен с выходом цифроаналогового преобразователя , цифровые входы которого соединены с выходами соответствующих Q разрядов реверсивного счетчика,

счетные входы -разрядов которого сое;динены с выходами соответствующих разрядов распределителя импульсов, а входы установки режима работы 5 с выходом схемы сравнения, элемент И, первый вход которого соединен с единичным выходом триггера управления , а второй вход - с выходом генератора импульсов, единичный вход n триггера управления соединен с шиной Запуск, а нулевой выход - с шиной Готовность, отличающийся тем, что, с целью повышения достоверности выходного кода и уменьшения погрешности преобразования, в него введен блок разрешения уменьшения шага квантования, первый вход которого соединен с выходом схемы сравнения, второй вход с выходом элемента И, а третий вход- 0 с единичным выходом младшего разряда распределителя импульсов, первый выход - с управляющим входом рейерсивного счетчика, второй выход с входом распределителя импульсов, 5 а третий выход - с нулевым входом триггера управления.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1983-03-07—Публикация

1981-06-26—Подача