1

Изобретение может быть использовано, в частности, для сбора данных (временных и точностных характеристик) при работе диспетчер за пультами управления сложных технологических установок.

Известны устройства для регистрации временных процессов в системах централизованного контроля, содержащие счетчики, счетчик текущего времени, генератор эталонной частоты, подключенный к входам счетчиков, выводной согласующий блок и блок регистрации, причем входные старт-стопные шины счетчиков контактно подключаются к контролируемым точкам объекта через вводной коммутирующий блок, а выходы счетчиков подключены через выводной согласующий блок к блоку регистрации.

Такое устройство позволяет производить централизованный сбор данных (временных характеристик), например, при управлении диспетчером сложных технологических установок. Однако набор алгоритма рабочих программ .исследования (подключение соответствующих точек объекта к рабочим шинам устройства) производится вручную с помощью переключателей вводного коммутатора.

Кроме того, отсутствует контроль за ошибочными операциями диспетчера, а также контроль за невыполнением диспетчером необходимых операций за предельно установленное время.

Цель изобретения - расширение функциональных возможностей устройства и повышение его оперативности.

Цель достигается тем, что в предлагаемое устройство введены адресные регистры, схемы сравнения, дополнительная схема «ИЛИ, разделительные диоды, распределитель адресов, шифраторы ввода и вывода, входы которых связаны соответственно со старт- и стопсигнальными шинами контролируемых точек объекта, причем информационный выход шифратора ввода подключен к первым входам

адресных регистров, тактовый выход шифратора ввода подключен к одному из входов распределителя адресов, выходы ячеек которого подключены соответственно к вторым входам счетчиков и к шинам разрешения записи

адресных регистров, первые кодовые выходы которых подключены к второму выходу выводного согласующего блока, а вторые подключены соответственно к первым входам схем сравнения, выходами связанных с третьими

входами соответствующих счетчиков, через схему «ИЛИ с третьим входом выводного согласующего блока и через разделительные диоды с шинами списывания соответствующих адресных регистров и с входами ячеек распределителя адресов.

Выходы переполнения счетчиков подключены соответственно к шинам сброса счетчиков, через разделительные диоды - к шинам списываиия соответствующих адресных регистров, к входам ячеек распределителя адресов и через донолнительную схему «ИЛИ - к четвертому входу выводного согласующего блока, информационный выход шифратора вывода подключен к вторым входам схем сравнения и к пятому входу выводного coi aaсующего блока, а второй выход выводного согласующего блока соединен с вторым входом счетчика текущего времени.

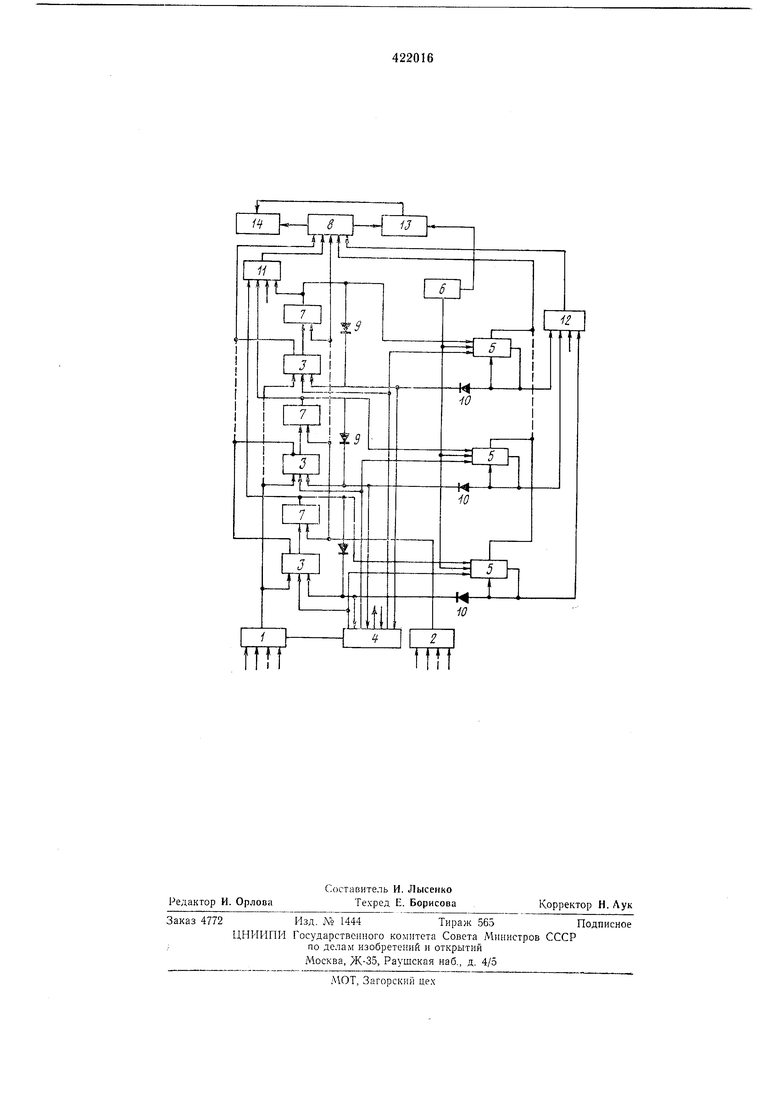

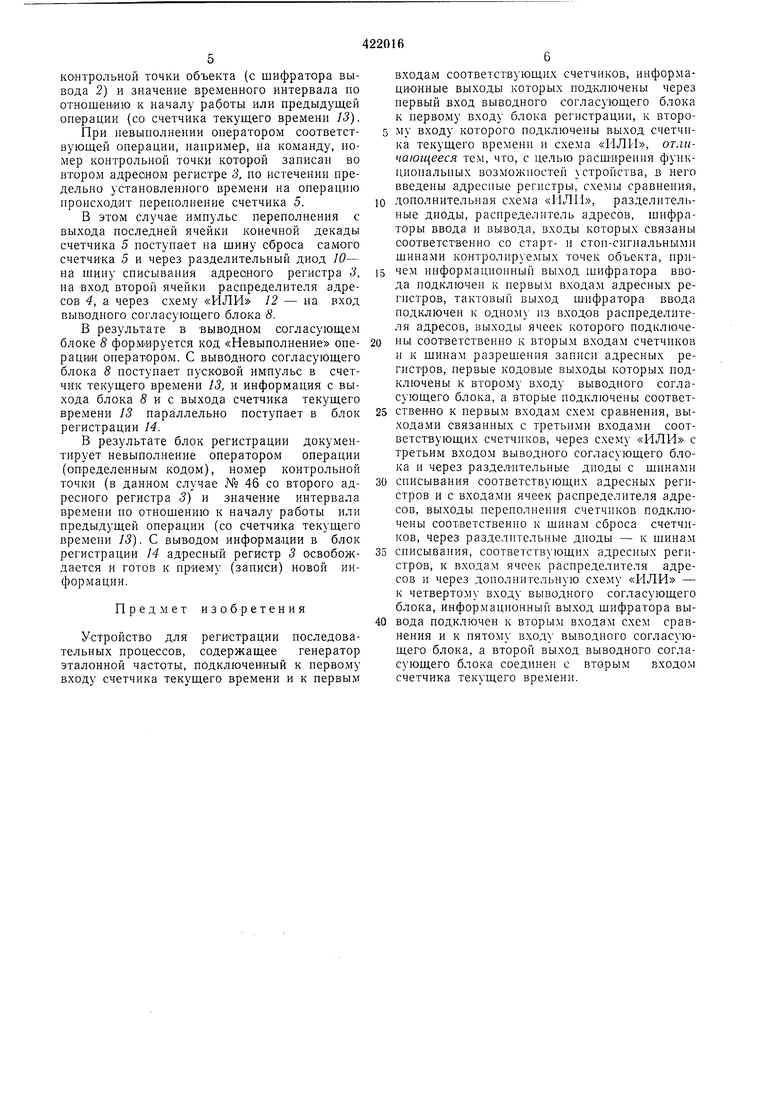

На чертеже изображена блок-схема устройства. Оно содержит шифратор ввода 1, шифратор вывода 2, адресные регистры 3, распределитель адресов 4, счетчики 5, генератор эталонной частоты 6, схемы сравнения 7, выводной согласующий блок 8, разделительные диоды 9 и 10, схемы «ИЛИ 11 12, счетчик текущего времени 13 и блок регистрации 14.

Устройство работает следующим образом. При поступлении старт-импульса с любой контролируемой точки объекта (например, с контролируемой точки, порядковый номер которой 25) на соответствующий вход шифратора/в последнем формируется соответствующий код и параллельно поступает на кодовые входы адресных регистров 3. Одновременно с тактового выхода щифратора / поступает пусковой импульс в распределитель адресов 4, с помощью которого срабатывает первая ячейка и посылает импульс на щину разрешения записи первого адресного регистра 5 и на соответст вующий вход счетчика 5, а сама нереходит в состояние «1 и подготавливает цепь связи второй ячейки распределителя адресов 4 с вторым адресным регистром 3. В результате номер контрольной точки объекта записывается в первом адресном регистре 3, запускается счетчик 5, на вход которого начинают поступать счетные импульсы от генератора эталонной частоты 6. В свою очередь адресный регистр 3 подготавливает (по первым кодовым входам) с ним связанную схему оравнепия 7.

При поступлении следующего старт-импульса с контролируемой точки, например, порядковый номер которой 46, на соответствующий вход шифратора 1 ввода аналогично номер этой контрольной точки записывается во втором адресном регистре 3 и включается с ним связанный счетчик 5.

При этом вторая ячейка в распределителе адресов 4 переходит в состояние «Ь и подготавливает цепь связи третьей ячейки с третьим адресным регистром 3 и т. д.

При поступлении стоп-импульса, напрпмер, с контрольной точки N° 25 на соответствующий вход шифратора вывода 2 в нем формируется соответствующий код и с выхода шифратора параллельно поступает на вторые кодовые входы схем сравнения 7 и на вход выводного согласующего блока 8.

В данном случае в схеме сравнения 7, связанной с первым адресным регистром 3, произойдет совпадение кодов. Импульс совпадения с выхода схемы сравнения 7 параллель5 но поступает на другой вход счетчика 5, через разделительный диод 9 на шину списывания адресного регистра 3, на вход первой ячейки раснределителя адресов 4 и через схему «ИЛИ 11 на вход выводного согласующего 10 блока 8.

При этом в выводном согласующем блоке формируется код «Положительно оценки операции; кроме того, счетчик 5 останавливается и информация (измеренный временной интер15 вал) с его выхода, а также информация (номер контрольной точки) с адресного регистра 3 н с Н1ифратора вывода 2 (номер той же коитролыной точки) поступают на соответствующие входы выводного согласующего блока 8. С тактового выхода выводного согласующего блока 8 пусковой импульс поступает в счетчик текущего времени 13. В результате информация (временной интервал по отношению к началу работы) со счетчика текущего, 5 времени 13 и с выводного согласующего блока 8 ноступает в блок регистрации 14, который документирует положительную оценку выполнения операции (определен:ным кодом), номер контрольной точки объекта (с первого 0 адресного регистра 3), значение .временного интервала операции (со счетчика 5) и значение временного интервала но отношению к началу работы или предыдущей операции (со счетчика текущего времени 13). В момент вы5 вода информации в блок регистрации М счетчик 5, первый адресный регистр 3 и первая ячейка в распределителе адресов 4 приводятся в состояние «О импульсом сброса. При этом первый адресный репистр 3 снова готов к при0 ему (записи) новой информации.

При выполнении оператором «ошибочной операции, т. е. когда стоп-импульс поступает на вход щифратора 2 вывода с контрольной точки объекта, номер которой не записан в 5 адресных регистрах 3, информация (номер этой контрольной точки объекта) с выхода шифратора вывода 2 аналогично предыдущему параллельно поступает на вторые входы схем сравнения 7 и на вход выводного согласующего блока 8. В этом случае в схемах сравнения 7 не происходит совпадения кодов, так как номер этой контрольной точки объекта не был записан в адресных регистрах. В результате не поступает импульс совпадения 5 в выводной согласующий блок 8, что вызывает в нем формирование кода «Отрицательно оценки операции оператора. При этом с выводного согласующего блока 8 поступает пусковой импульс в счетчик текущего времени /5, и информация с его выхода и со счетчика текущего времени 13 параллельно поступает в блок регистрации 14.

В результате чего блок регистрации 14 документирует отрицательную оценку операции оператора (определенным кодом), номер

контрольной точки объекта (с шифратора вывода 2) и значение временного интервала по отношению к началу работы или предыдущей операции (со счетчика текущего времени 13).

При невыполнении оператором соответствующей операции, например, на команду, помер контрольной точки которой записан во втором адресном регистре 3, по истечении предельно установленного времени на операцию происходит переполнение счетчика 5.

В этоМ случае импульс переполнения с выхода последней ячейки конечной декады счетчика 5 поступает на шину сброса самого счетчика 5 и через разделительный диод 70- на шину списывапия адресного регистра 3, на вход второй ячейки распределителя адресов 4, а через схему «ИЛИ 12 - на вход выводного согласующего блока 8.

В результате в выводном согласующем блоке 8 формируется код «Невыполнение операцюи оператором. С выводного согласующего блока 8 поступает пусковой импульс в счетчик текущего времени 13, и информация с выхода блока 8 и с выхода счетчика текущего времени 13 параллельно поступает в блок регистрации 14.

В результате блок регистрации документирует невыполнение оператором операции (определенным кодом), номер контрольной точки (в данном случае № 46 со второго адресного регистра 3) и значение интервала времени по отношению к началу работы или предыдущей операции (со счетчика текущего времени 13). С выводом информации в блок регистрации 14 адресный регистр 3 освобождается и готов к приему (записи) новой информации.

Предмет изобретения

Устройство для регистрации последовательных процессов, содержащее генератор эталонной частоты, подключенный к первому входу счетчика текущего времени и к первым

входам соответствующих счетчиков, информационные выходы которых подключены через первый вход выводного согласующего блока к первому входу блока регистрации, к второму входу которого подключены выход счетчика текущего времени и схема «ИЛР, отличающееся тем, что, с целью расширения функциопальпых возможностей устройства, в него введены адресные регистры, схе.мы сравнения,

дополнительная схема «ИЛИ, разделительные диоды, распределитель адресов, шифраторы ввода и вывода, входы которых связапы соответственно со старт- и стоп-сигнальными шинами контролирхемых точек объекта, прнчем ипформационный выход шифратора ввода подключен к первым входам адресных регистров, тактовый выход Шифратора ввода подключен к одно.му из входов распределителя адресов, выходы ячеек которого подключены соответственно к вторым в.ходам счетчиков и к шинам разрешения записи адресных регистров, первые кодовые выходы которых подключены к второму входу выводного согласующего блока, а вторые подключены соответствепйо к первым входам схем сравнения, выходами связанных с третьими в.ходами соответствующих счетч 1ков, через схему «ИЛИ с третьим входом выводного согласующего блока и через разделительные диоды с шинами

списывания соответствующих адресных регистров и с входами ячеек распределителя адресов, выходы переполнения счетчиков подключены соответственно к шинам сброса счетчиков, через разделительные диоды - к шинам

списывания, соответствующих адресных регистров, к входам ячеек распределителя адресов и через дополнительную схему «ИЛИ - к четвертому входу выводного согласующего блока, информационный выход шифратора вывода подключен к вторым входам схем сравнения и к пятому входу выводного согласующего блока, а второй выход выводного согласующего блока соединен с вторым входом счетчика текущего времени.

IT Г

тт

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для опроса абонентов | 1981 |

|

SU1013968A1 |

| Многоканальный анализатор электрофизиологических сигналов | 1991 |

|

SU1806603A1 |

| Многоканальная система для анализа формы и регистрации аналоговых процессов | 1983 |

|

SU1149242A1 |

| Устройство для сопряжения многоблочной памяти с процессором и вводно-выводными устройствами | 1984 |

|

SU1280645A1 |

| Устройство для обмена информацией между цифровой вычислительной машиной и внешними устройствами | 1982 |

|

SU1062681A2 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для решения задачи поиска длиннейшего пути | 1983 |

|

SU1206791A1 |

| Устройство для отладки программ | 1980 |

|

SU960828A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Устройство для обработки и регистрации сигналов | 1987 |

|

SU1458845A1 |

Даты

1974-03-30—Публикация

1972-10-30—Подача