1

Изобретение относится к вычислительной технике, в частности к вычислительным машинам, которые работают с оиеранда1ми переменной длины, запоминают результат операции на месте операнда и обладают способностью повторно выполнять команду, во время выполнения которой была обнаружена ошибка.

Известны устройства для управления повторением команд фор.мата типа «Память-память, не требующие буфера для операндов и обеспечивающие возврат в начало команды с соответствующей коррекцией ее исходных параметров. Основная система, для которой предназначено подобное устройство, имеет блок управления, арифметико-логическое обрабатывающее устройство для обработки операндов (АЛУ) и счетчик байтов операнда. Кроме этого, для обеспечения повтора имеются счетчик для подсчета числа байтов, накопленных без ошибок; схема, подсоединенная к устройству обнаружения ощибок, для запрещения работы счетчика байтов; схема, соединенная с устройством обнаружения ошибки, заставляющая блок управления работать в режиме повтора при сигнале ощибки; устройство индикации изменения начальных данных, позволяющее блоку унравления перейти на последовательность новторного вынолнения, при котором выполнение текущей команды начинается с номера байта, следующего за номером байта в счетчике правильно обработанных байтов.

Таким образом, в известном устройстве параллельно с рабочим счетчиком байтов работает специальный счетчик. В момент ошибки содержимое этого счетчика фиксируется и указывает, какое количество байтов было обработано правильпо. По ощибке блок управления начинает повтор возвратом в начало команды. При этом, если устройство индикации изменения начальных данных до момента ошибки зафиксировало факт заииси на место операнда хотя бы одпого байта результата,

то начальные параметры команды корректируются на величину содерл-симого счетчика правильно обработанных байтов. Для этого после повторного извлечения команды из основной памяти на входные шины АЛУ принимается содержимое счетчика правильно обработанных байтов, зафиксированное в момент ошибки. Затем это содержимое добавляется к иcпOv ннтeльным адресам обоих операндов. Оно же вычитается из числа байтов

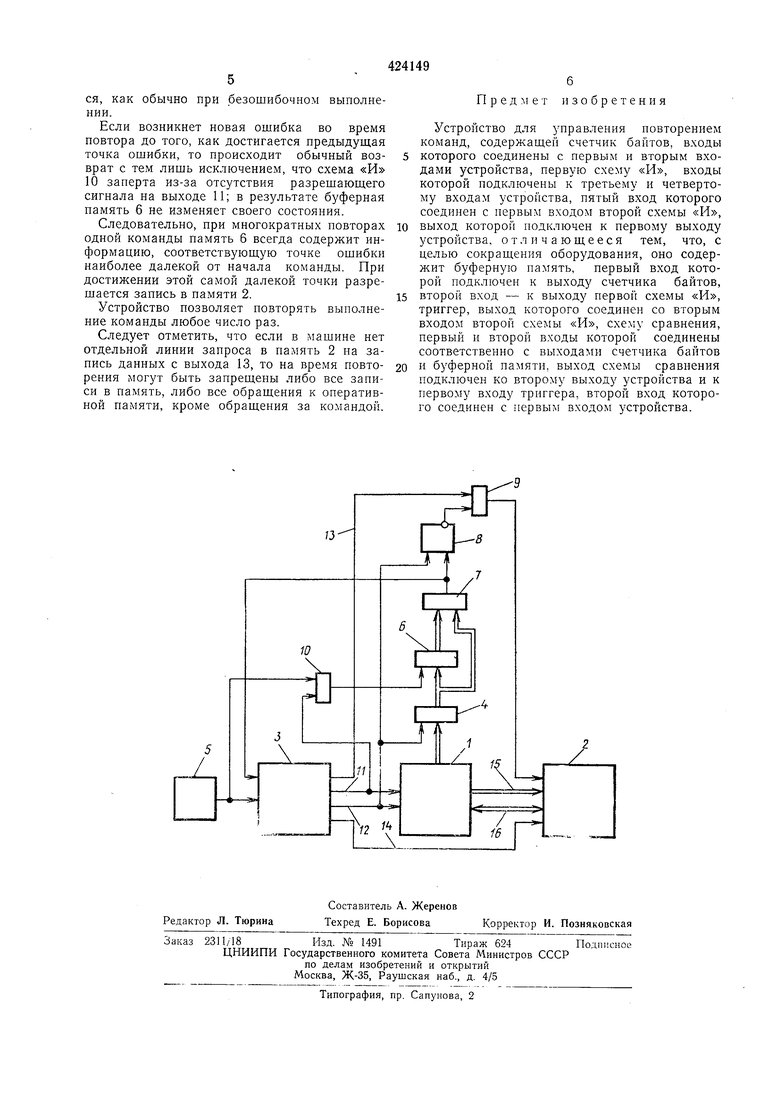

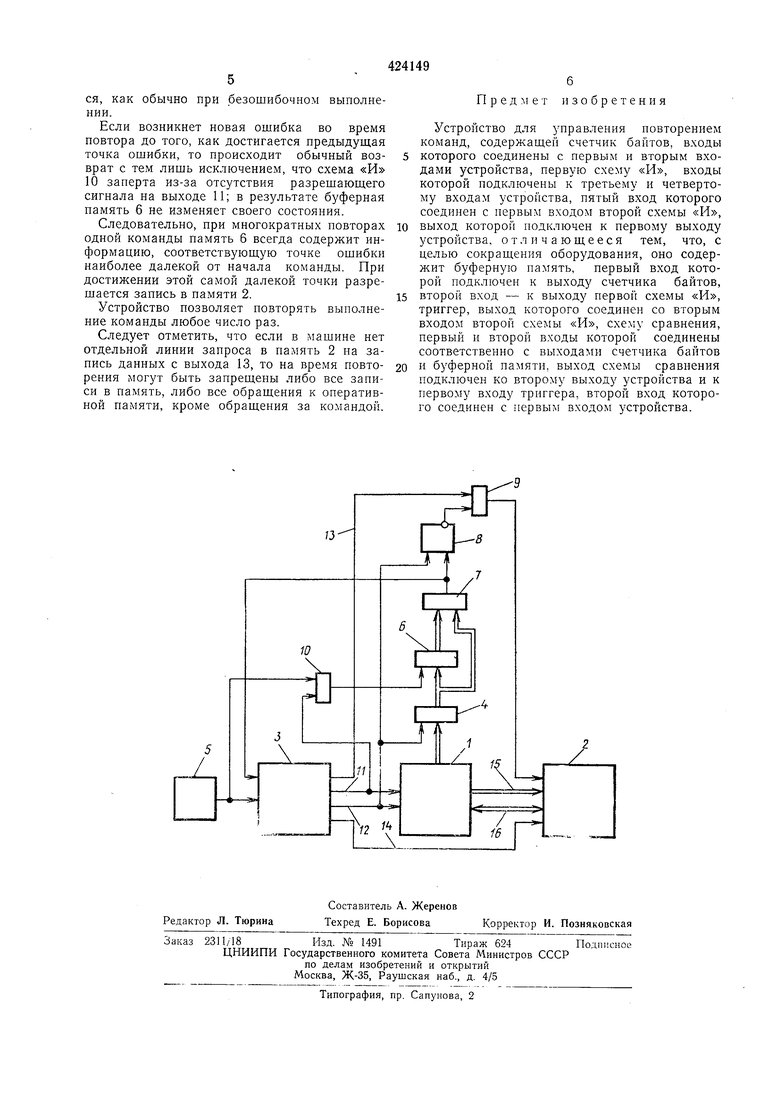

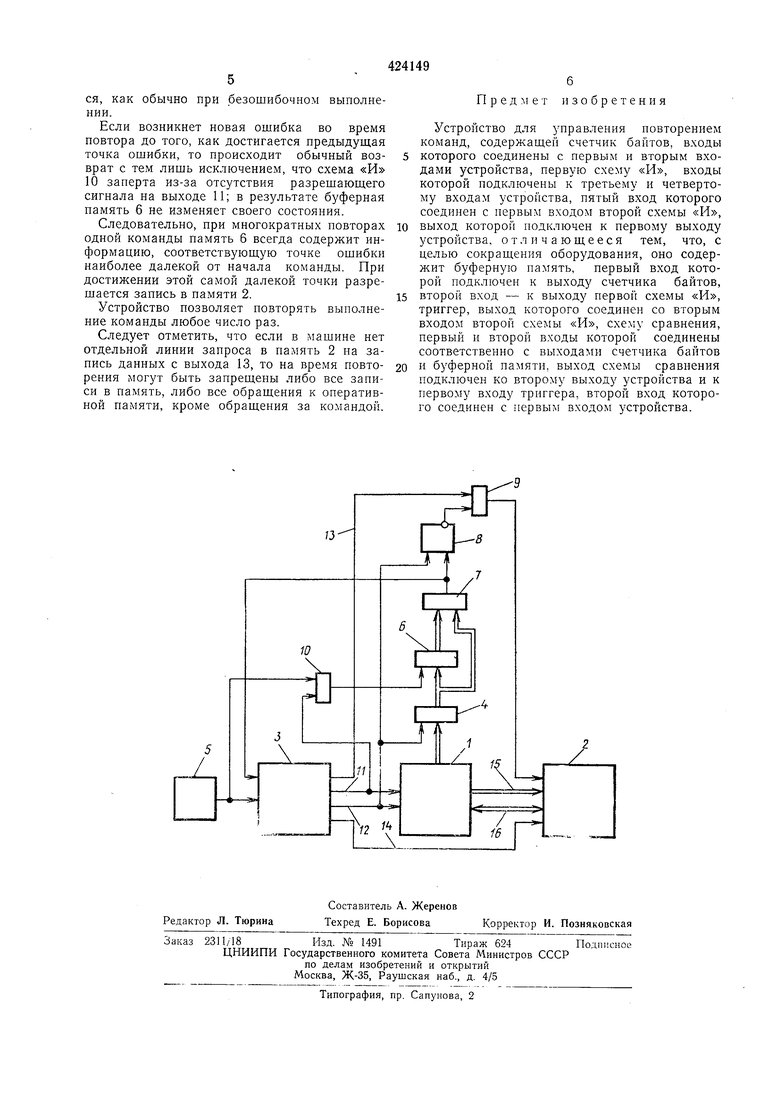

операнда, первоначально указанного в команде. Таким образом, новые исполнительные адреса операндов указывают теперь на первый необработанный из-за возникшей ошибки байт, а новая длина операнда соответствует длине необработанных из-за ошибки частен операндов. Этнм обеспечнвается повтор непосредственно с точки ошибки. Повторение команды требует коррекции исходных нарамегров команды. Для обеснечения этой нроцедуры необходима уномянутая аппаратура и некоторые возможности блока управления, которые используются только в момент обнаружения ошибки. Следовательно, известные устройства характеризуются, во-первых, наличием большого количества редко функциоП11рую1цего оборудования (счетчик баГггов, работающий параллельно с основным, устройство индикации измсиения начальных данных, аннаратура блока управления, обеспечивающая коррекцию начальных параметров команды для повтора); во-вторых, наличием связей для приема содержимого счетчика правильно обработанных байтов в АЛУ, где нроисходит коррекция команды для цовтора; в-третьих, нестереотинностью процедуры возврата но ошибке, что требует от устройства управления нри возврате анализа формата новторяемой команды и состояния устройства изменения начальных данных. Целью изобретения является сокращение оборудования устройства, обеспечивающего повторное выполнение команд обработки операндов неременной длины. Описываемое устройство отличается тем, что оно содержит буферную память, первый вход которой подключен к выходу счетчика байтов, второй вход - к выходу нервой схемы «И, триггер, выход которого соединен со вторым входом второй схемы «И, схему сравнения, нервый и второй входы которой соединены соответственно с выходами счетчика байтов и буферной памяти, выход схемы сравнения подключен ко второму выходу устройства и к первому входу триггера, второй вход которого соедипен с нервым входом устройства. При повторении команды обработка операнда начинается с первого байта, но запись в память результата обработки запрещается триггером запрета до того момента, пока схе ма сравнения не обнаружит совпадения номера обрабатываемого байта в рабочем счетчике байтов операнда с сохраненным в буфере номером байта, нри обработке которого произошла ошибка. Па чертеже представлена схема устройства и основные функциональные блоки вычислительной машины, с которыми взаимодействует устройство и приняты следующие обозначения: 1-центральный блок обработки; 2 - оперативная память; 3 - блок управления; 4 - счетчик байтов; 5 - блок обнаружения ошибок; 6 - буферная память; 7 - схема сравнения; 8 - триггер; 9 и 10 - схемы 11 -14 - выходы блока управления; 15 - адресные шины оперативной памяти; 16 - шипы данных оперативной памяти. Выполняемая программа и ее исходные данные находятся в оперативной памяти 2. По сигпалам блока управлепия 3 команды извлекаются из памяти 2 и обрабатываются в центральном блоке 1 обработки. Для этого блок 1 выдает на адресные шины 15 оперативной памяти адрес очередной команды, и в ответ на запрос чтения с выхода 14 оперативная память выдает команду из шины 16 данных оперативной памяти. Команда принимается блоком 1 и начинает выполняться. Информация обрабатывается байт за байтом. При этом блок 1 выдает на шины 15 адреса операндов и получает по шипам 16 очередпые байты операпдов. Результат обработки выдается на шины 16 и по запросу на запись данных с выхода 13 занисывается в память 2 па место одного из операпдов. Если блок 5 обнаруживает ошибку, то на его выходе появляется сигнал, под воздействием которого срабатывает схема «И 10. Сигнал па выходе этой схемы заставляет принять содержимое рабочего счетчика байтов 4 в буферную память 6, в результате запоминается число безошибочно обработанных байтов. Затем блок 3 управления снимает с выхода 11 блока управления сигнал, разрешающий повтор, схема «И 10 запирается, не разрешая тем самым изменения содержимого буферной памяти. Сигнал на выходе 12 блока управления устанавливает счетчик байтов 4 в ноль, а триггер 8 - в единицу. При этом запрещается прохождение через схему «И 9 запроса в намять 2 на запись даппых, так как снимается сигнал с нулевого выхода триггера 8. Процедура возврата блока обработки в нача.ю выполнения команды может быть реализована любым известным способом, например так же, как и при обработке операндов других форматов. Блок 3 начинает повторное выполиепие комапды, в которой произошла ошибка, как обычную очередную команду с самого начала, обрабатывая операпды с первого байта. По в качестве одного из операндов берется правильпо записанный результат предыдущей попытки выполнить команду. Этот результат занимает теперь место одного из онерандов. Очевидно, что получающийся прп этом в блоке 1 результат будет неверным. По поскольку все обращения к памяти 2 на запись результата запрещены триггером этот неверный результат в память записан не будет. Таким образом, во время повтора правильно обработанные байты вновь обрабатываются «вхолостую, и это продолжается до тех пор, пока в процессе повтора пе будет достигнута точка ошибки. В этот момент содержимое счетчика байтов 4 совпадает с содержимым буферной памяти 6. Схема сравнения 7 обнаруживает этот момент и выдает сигнал, который устапавлнвает в ноль триггер 8 и разрешает блоку 3 восстановить сигнал на выходе 11. Вновь появляется разрешающий сигнал на нулевом выходе триггера 8, и схема «И 9 нропускает очередной запрос па запись в память 2 результатов операции. С этого момента операция выполняет

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦЕНТРАЛЬНЫЙ ПРОЦЕССОР МУЛЬТИПРОГРАММНОЙ МУЛЬТИПРОЦЕССОРНОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1971 |

|

SU309363A1 |

| Процессор с микропрограммным управлением | 1975 |

|

SU525956A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Процессор | 1984 |

|

SU1246108A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Селекторный канал | 1988 |

|

SU1534465A2 |

| Устройство для обмена информацией | 1983 |

|

SU1149239A1 |

| Мультиплексный канал | 1980 |

|

SU964620A1 |

| Селекторный канал | 1983 |

|

SU1103218A1 |

Даты

1974-04-15—Публикация

1972-06-12—Подача