Изобретение относится к средствам вычисл1 тельной техники и предназначено для проверки и исследования характеристик аналогоцифровых преобразователей.

Известна система аналого-цифрового преобразования, содержанлая генератор серий, подключенныГ к регистру, управляющему цифро-аналоговыми преобразователями, соединенными с входами соответствуЕОЩих аналогоцифровых преобразователей, схему управления.

Однако в известной системе код, снимаемый с аналого-цифрового преобразователя, оценивается но одному значению аналоговой величины, которая подается с цифро-аналогового преобразователя, в связи с чем невозможно установить границы устойчивости кода. Необходимость организации поиска в двух нанравлениях в каждом коде требует много времени прн проверке многоразрядных преобразователей. Кроме того, получается неопределенная ситуация, когда ошибка кода превышает установленный предел, а в случае увеличения пределов увеличивается время проверки преобразователей.

С целью расширения функциональных возможностей системы в нее введены регистратор, коммутатор кодов, датчик признака устойчивости кода, выполненный в виде двух счетчиков с триггером и схемами совпадения «ИЛИ,

занрета, причем выходы младшнх разрядов аналого-цифровых преобразователей соединены с входом первого счетчика непосредственно и через схему запрета - с входом второго счетчика датчика признака устойчивости кода, один выход первого счетчика последнего подключен к первым входам схемы совпадения и схемы «ИЛИ, вторые входы которых соединены с выходами второго счетчика, а выходы схемы совпадения и схемы «ИЛИ датчика признака устойчивости кода через триггер связаны с одним из входов схемы управления, управляющего работой регистратора, подключенного к выходу коммутатора кодов, один

вход которого соединен с выходом регистра, другой - с выходами аналого-цифровых преобразователей.

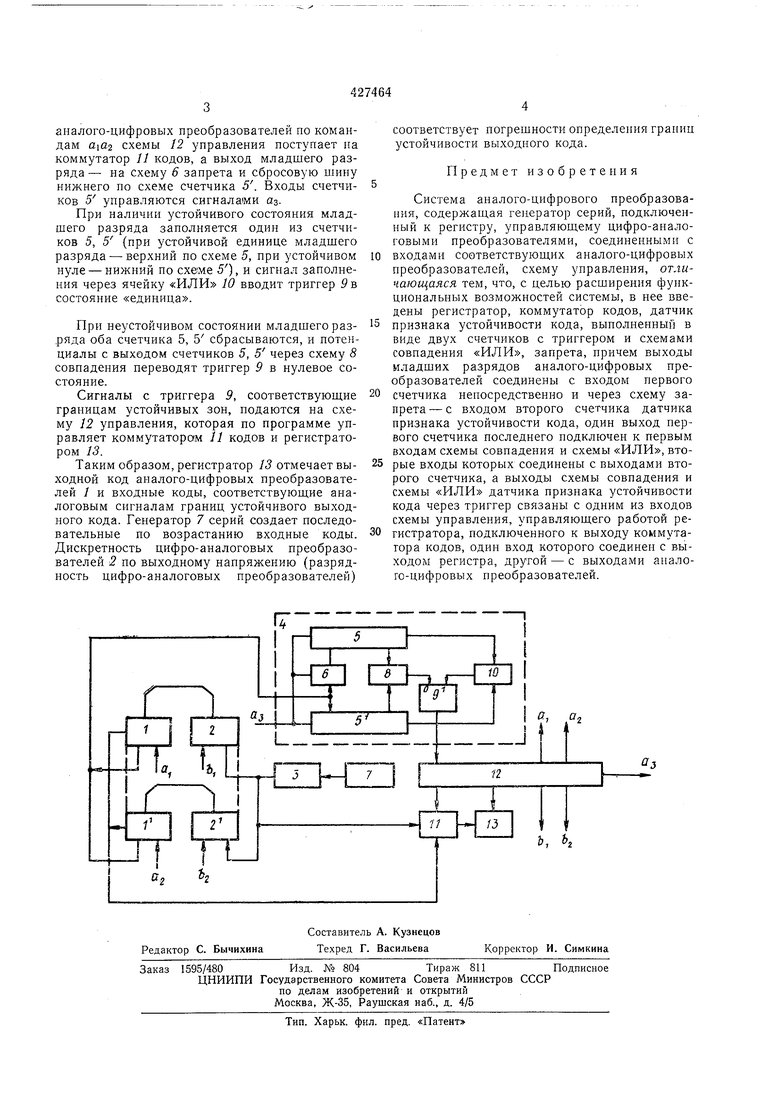

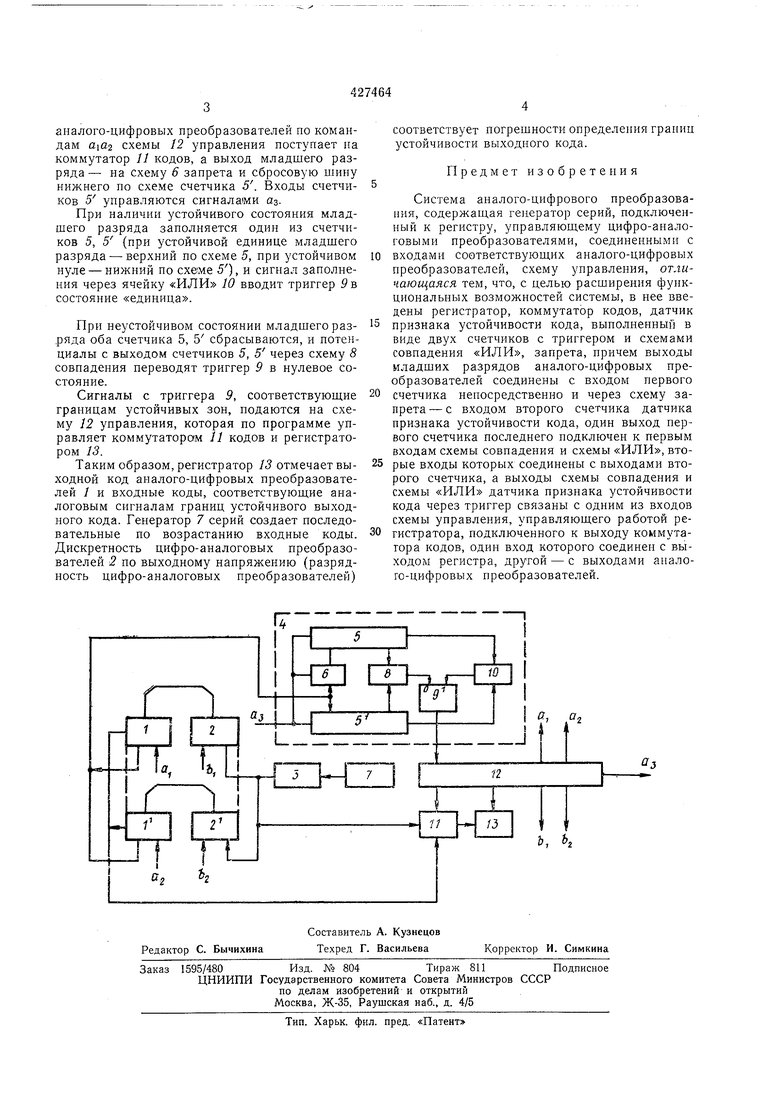

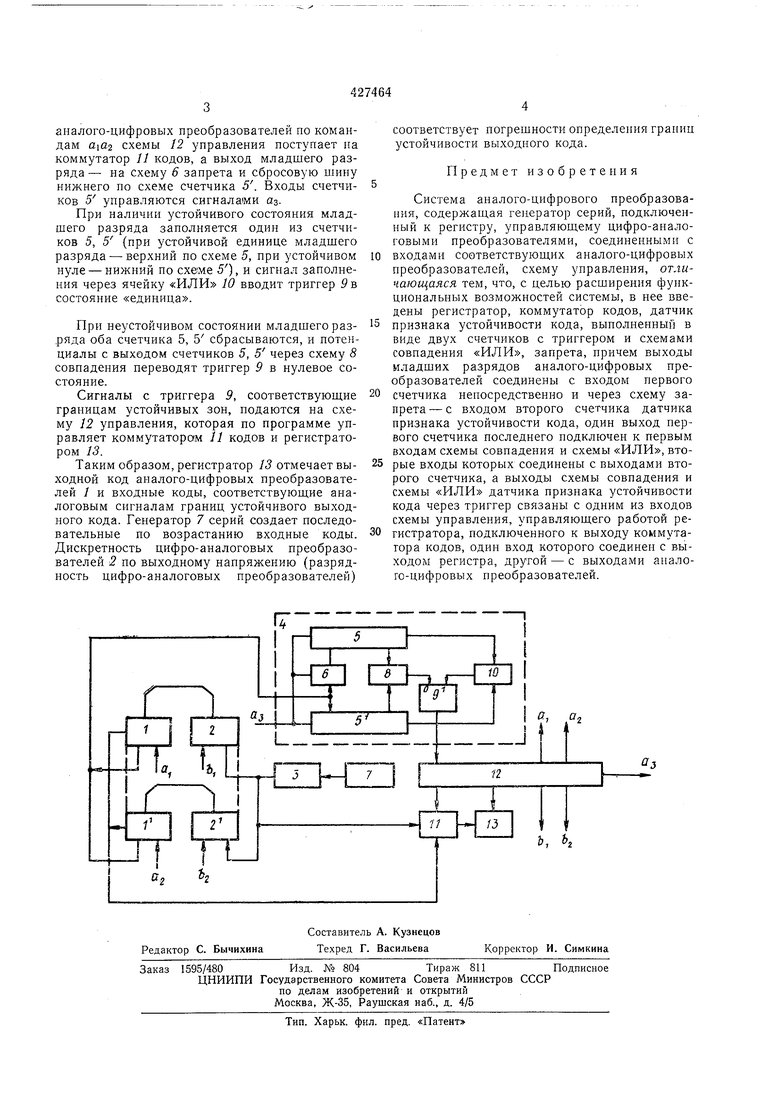

На чертеже представлена блок-схема предлагаемой системы аналого-цифрового преобразования.

Система содержит аналого-цифровые преобразователи /, цифро-аналоговые преобразователи 2, регистр 3, датчик 4 признака устойчивости кода, счетчики 5, схему 5запрета,

генератор 7 серий, схему 8 совпадения, триггер 9, схему «ИЛИ 10, коммутатор // кодов, схему 12 управления и регистратор 13.

Код из регистра 3 по сипталам Ь Ь схемы 12 управления записывается в цифроаналоговые преобразователи 2. Код с выхода

аналого-цифровых преобразователей по командам uiuz схемы 12 управления поступает на коммутатор 11 кодов, а выход младшего разряда - на схему 6 запрета и сбросовую шину нижнего по схеме счетчика 5. Входы счетчиков 5 управляются сигналами аз.

При наличии устойчивого состояния младшего разряда заполняется один из счетчиков 5, 5 (при устойчивой единице младшего разряда - верхний по схеме 5, при устойчивом нуле - нижний по схеме 5), и сигнал заполнения через ячейку «ИЛИ 10 вводит триггер 9ъ состояние «единица.

При неустойчивом состоянии младшего разряда оба счетчика 5, 5 сбрасываются, и потенциалы с выходом счетчиков 5, 5 через схему 8 совпадения переводят триггер 9 в нулевое состояние.

Сигналы с триггера 9, соответствующие границам устойчивых зон, подаются на схему 12 управления, которая по программе управляет коммутаторам 11 кодов и регистратором 13.

Таким образом, регистратор 13 отмечает выходной код аналого-цифровых преобразователей / и входные коды, соответствуюш,ие аналоговым сигналам границ устойчивого выходного кода. Генератор 7 серий создает последовательные по возрастанию входные коды. Дискретность цифро-аналоговых преобразователей 2 по выходному напряжению (разрядность цифро-аналоговых преобразователей)

соответствует погрешности определения границ устойчивости выходного кода.

Предмет изобретения

Система аналого-цифрового преобразования, содержаш,ая генератор серий, подключенный к регистру, управляющему цифро-аналоговыми преобразователями, соединенными с входами соответствующих аналого-цифровых преобразователей, схему управления, отличающаяся тем, что, с целью расширения функциональных возможностей системы, в нее введены регистратор, коммутатор кодов, датчик

признака устойчивости кода, выполненный в виде двух счетчиков с триггером и схемами совпадения «ИЛИ, запрета, причем выходы младших разрядов аналого-цифровых преобразователей соединены с входом первого счетчика непосредственно и через схему запрета - с входом второго счетчика датчика признака устойчивости кода, один выход первого счетчика последнего подключен к первым входам схемы совпадения и схемы «ИЛИ, вторые входы которых соединены с выходами второго счетчика, а выходы схемы совпадения и схемы «ИЛИ датчика признака устойчивости кода через триггер связаны с одним из входов схемы управления, управляющего работой регистратора, подключенного к выходу коммутатора кодов, одни вход которого соединен с выходом регистра, другой - с выходами аналого-цифровых преобразователей.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРО-АНАЛОГОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УПРАВЛЯЮЩЕЕ | 1973 |

|

SU386409A1 |

| Устройство для контроля температуры | 1986 |

|

SU1410059A1 |

| СИСТЕМА АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1970 |

|

SU275547A1 |

| РЕГИСТРАТОР ПАРАМЕТРОВ АВАРИЙНЫХ СИТУАЦИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ ПОВЫШЕННОЙ ТОЧНОСТИ (ВАРИАНТЫ) | 2008 |

|

RU2376625C1 |

| Регистратор сигналов с усреднением | 1982 |

|

SU1112230A1 |

| Многоканальный цифро-аналоговый преобразователь | 1974 |

|

SU636794A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

| Устройство для кодирования электрических сигналов | 1990 |

|

SU1737733A2 |

| Устройство для измерения фазового сдвига | 1984 |

|

SU1190294A1 |

Даты

1974-05-05—Публикация

1972-07-21—Подача