Изобретение относится к области радиосвязи и может быть использовано в качестве .ирователя опорного нап1рял ения для приема фазоманипулнрованных сигналов с нестабильной несущей частотой.

Известно цифровое устройст1во частотной автоподстройки, содержащее сместитель обратной связи, выход которого подключен через ограничитель ко входу цифрового частотного дискриминатора, выходы наконителя частотных ощибок через формирователь нмнудьсов добавления и исключения подсоединены ,ко входу зиравления делителя частоты, к счетному в.ходу которого подключен выход хронизатора, а выход делителя частоты подключен через перемножитель напряжений и умножитель частоты к гетеродинному входу смесителя обратной связи.

Недостатком известного устройства является щирокая полоса захвата кольца частотной автоиодстройки и соответственно пониженная помехоустойчивость автонодстройки из-за возникновения астатической расстройки частоты.

С целью повыщения помехоустойчивосги автоподСтройки частоты в предлагаемом устройстве выход цифрового частотного дискриминатора подсоединен ко входу накопителя частотных ошибок через дополнительно введенный узел объединения, ко .второму входу которого подсоединен выход старшего разряда накопителя частотных ошнбок через дополнительно введенный узел комненсации астатической расстройки частоты, вход опроса которого связан с выходом хронизатора.

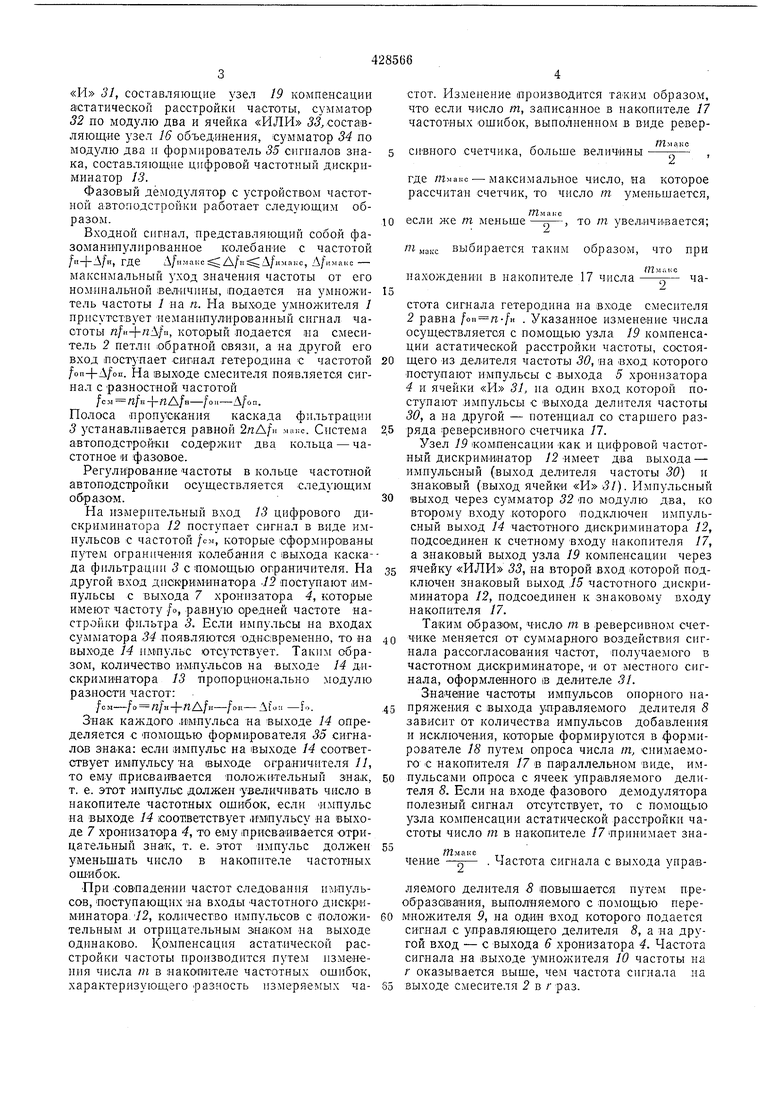

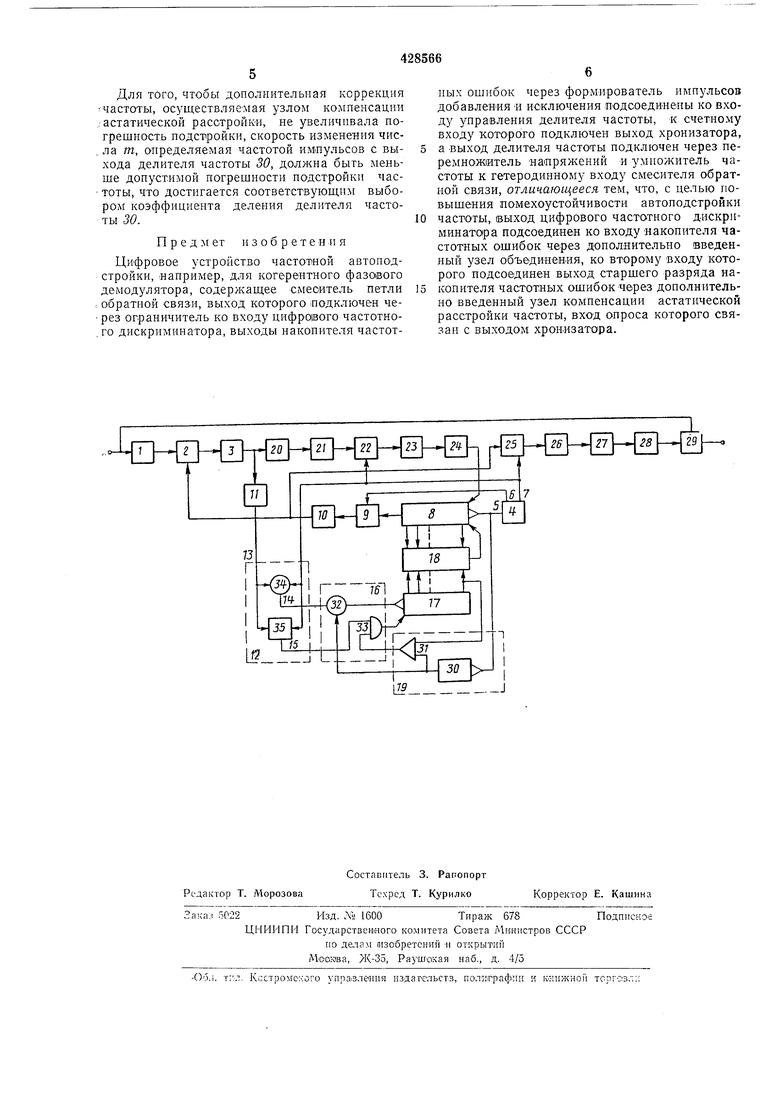

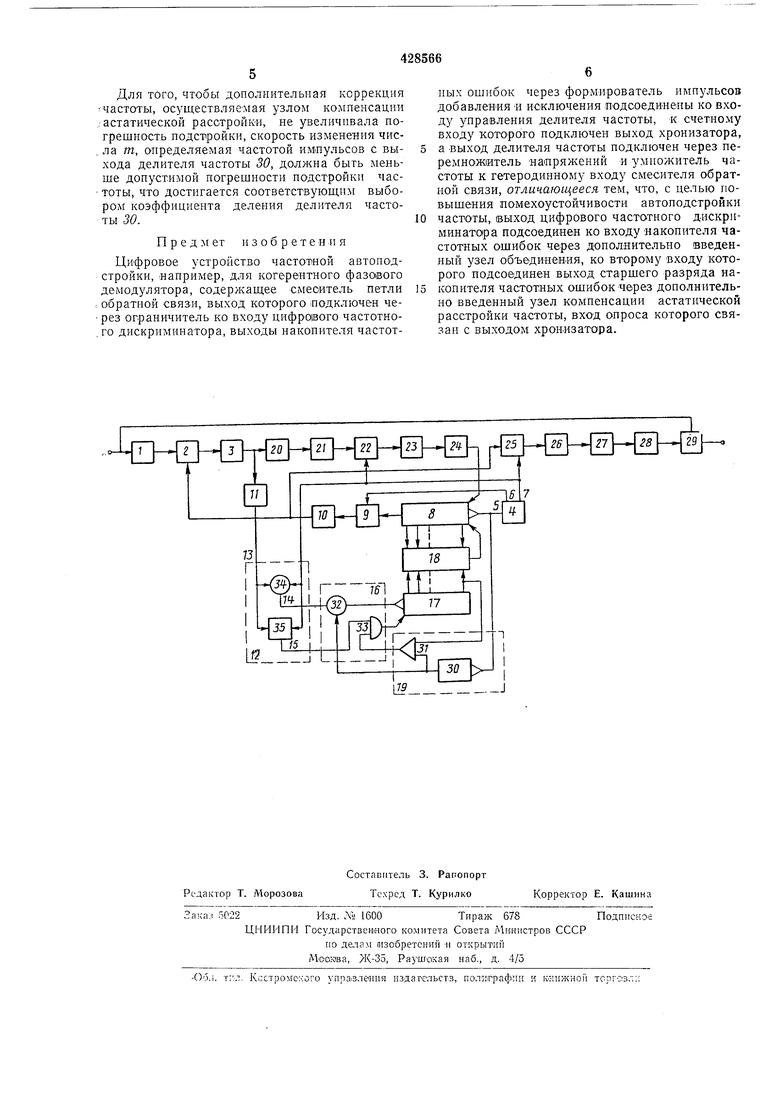

На чертеже приведена функциональная схема предлагаемого цифрового устройства частотной автоподстройки для когерентного фазового демодулятора.

Устройство содержит умножитель частоты 1 на л, где п - кратность фазоманипулированного сигнала, смеситель 2 петли обратной связи с каскадом фильтрации 3, хропизатор 4 с выходами 5-7, управляемый делитель 8, перемножитель папрял ений 9, умножнтель 10 частоты на г, ограничитель 11 кольца частотной автоподстройки, цифровой частотный дискриминатор 12 с измерительным входом 13, с выходом 14 импульсов ц с ВЫХОДОМ 15 знака, узел объединения 16, накопитель 17 частотных ooJибoк с формирователем /5 импульсов добавления н исключения, узел 19 комненсации астатической расстройки частоты, узкополосиый фильтр 20 кольца фазовой автоподстройки с ограничителем 21, цифровой фазовый дискриминатор 22, накопитель 23 фазовых ошибок с формирователем 24 импульсов добавления и -исключения, |Перемнон Итель напряжений 25 с ПОЛОСОВЫЛ1 фильтром 26 и огра нчителем 27, делитель частоты 28 на п, цифровой фазовый детектор 29, делитель частоты 30 и ячейка

«И 31, составляющие узел 19 компенсации астатической расстройки частоты, сумматор 32 по модулю два и ячейка «ИЛИ 5,cocTaiBляюЩИе узел 16 объедияения, сумматор 34 по модулю два и формирователь 35 сигналов знака, составляющие цифровой частотный дискриминатор 13.

Фазовый демодулятор с устройством частотной автоподстройки работает следующим образом.

Входной сигнал, представляющий собой фазомантшулирпванное колебание с частотой

, гдеД/нмапс Д/п , Д/кмакс -

максимальный уход значен-ия частоты от его номинальной ;велИчины, подается на умножитель частоты 1 на п. На выходе умножителя / присутствует немани-пулированный сигнал частоты п/н4-яА/н, который подается на смеситель 2 петли обратной связи, а на другой его вход поступает ситнал гетеродина с частотой /оп-|-А/оп. На выходе смесителя появляется сигпал с разностной частотой

/см П/н-|-ЛЛ/н/онД/оп.

Полоса пропускания каскада фильтрации 3 устанавливается равной 2яЛ/н Mai;c. Система автоподстройки содержит два кольца - частотное и фазовое.

Регулирование частоты в кольце частотной автоподстройки осуществляется следующим образом.

На измерительный вход 13 цифрового дискриминатора 12 поступает сигнал в В:иде импульсов с частотой /см, которые сформированы путем ограничения колебания с выхода каскада фильтрации 3 с помощью ограничителя. На другой вход дискри1мянагора J2 поступают импульсы с выхода 7 хронизатора 4, которые имеют частоту /о, равную средней частоте настройки фильтра 3. Если импульсы на входах сумматора 34 появляются однс.временно, то еа выходе 14 импульс отсутствует. Таким образом, количество импульсов на выходе 14 дискриминатора 13 проиорционально модулю разности частот:

/см/0 /г/Н-|-ПА/ 1/0« fo.

Знак каждого .шмпульса на выходе 14 определяется с ПОМОЩЬЮ формирователя 35 сигналов знака: если ;импульс на выходе 14 соответствует импульсу на выходе ограничителя 11, то ему присваивается пол1ожительный знак, т. е. этот Импульс должен увеличивать число в накопителе частотных ошибок, если «мпульс на выходе 14 (соот1ветствует .импульсу на выходе 7 хронизатара 4, то ему присваивается отрицательный знак, т. е. этот импульс должен уменьшать число в накопителе частотных ошибок.

При -совпадении частот следования импульсов, поступающих на входы частотного дискрммпнатора., количество импульсов с положительным и отрицательным 31наком на выходе одинаково. Компенсация астатической расстройки частоты производится путем изменения числа tn в накопителе частотных ошибок, характеризующего разность измеряемых частот. Изменение производится таким образом, что если число т, записанное в накопителе 17 частотных ощибок, выиолнениом в виде ревертмакс

сивного счетчика, оольше величины

2

где /Пмакс - максимальное число, на которое рассчитан счетчик, то число т уменьшается,

/7 мал с

то т увел.ичи.вается;

если же т меньше

выбирается таким образом, что при

т

тмаис

нахождении в накопителе 17 числа - частота сигнала гетеродина на входе смесителя 2 равна . Указанное измепение числа осуществляется с помощью узла 19 компенсации астатической расстройки частоты, состоящего из делителя частоты 30, па вход которого поступают импульсы с выхода 5 хронизатора 4 и ячейки «И 31, на один вход которой поступают импульсы с выхода делителя частоты 30, а на другой - потенциал со старшего разряда реверсивного счетчика П.

Узел 19 компенсации как и цифровой частотный дискриминатор 12 имеет два выхода - импульсный (выход делителя частоты 30) и знаковый (выход ячейки ). Имиульсный 1ВЫХОД через сумматор 32 ио модулю два, ко второму входу которого подключен импульсный выход 14 частотного дискриминатора 12, подсоединен к счетному входу накопителя 17, а знаковый выход узла 19 компенсации через ячейку «ИЛИ 33, на второй вход которой подключен знаковый выход 15 частотного дискриминатора 12, подсоединен к знаковому входу наконителя 17.

Таким образом, число т в реверсивном счетчике меняется от суммарного воздействия сигнала рассогласования частот, получаемого в частотном дискриминаторе, и от местиого сигнала, оформленного IB дел-ителе 31.

Зна1чение частоты импульсов опорного наирял :ения с выхода управляемого делителя 5 зависит от количества импульсов добавления и исключения, которые формируются в формирователе 18 путем опроса числа т, снимаемого с накопителя 17 в параллельном виде, импульсами опроса с ячеек управляемого делителя 8. Если на входе фазового демодулятора полезный сигнал отсутствует, то с помощью узла компенсации астатической расстройки частоты число т в накопителе /7 принимает знаЯгмакс „

чение . Частота сигнала с выхода управляемого делителя 8 повыщается путем преобразования, выполняемого с помощью перемножителя 9, на один вход которого подается ситнал с управляющего делителя 8, а на другой вход - с выхода 6 хронизатора 4. Частота сигнала на выходе умножителя 10 частоты на / оказывается выше, чем частота сигнала на

выходе смесителя 2 в г раз.

Для того, чтобы дополнительная коррекция -частоты, осуществлябмая узлом компенсации ;астатической расстройки, не увеличивала погрешность подстройки, скорость изменения чис. ла т, определяемая частотой импульсов с выхода делителя частоты 30, должна быть меньше допустимой погрешности подстройки частоты, что достигается соответствующим выбором коэффициента деления делителя частоты 30.

Предмет изобретения

Цифровое устройство частотной автоподстройки, иапример, для когерентного фазового демодулятора, содержащее смеситель петли : обратной связи, выход которого подключен че рез ограничитель ко входу цифрового частотно.го дискриминатора, выходы накопителя частотных ошибок через формирователь импульсов добавления я исключения подсоединены ко входу управления делителя частоты, к счетному входу которого подключен выход хронизатора, а выход делителя частоты подключен через перемножитель -напряжений и умножитель частоты к гетеродинному входу смесителя обратной связи, отличающееся тем, что, с целью повышения помехоустойчивости автоподстройки частоты, выход цифрового частотного д.искрим,инато ра подсоединен ко входу накопителя частотных ошибок через дополнительно введенный узел объединения, ко второму входу которого подсоединен выход старщего разряда накопителя частотных ошибокЧерез дополнительно введенный узел компенсации астатической расстройки частоты, вход опроса которого связаи с выходом хрон.изатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЕ УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ | 1973 |

|

SU375772A1 |

| УСТРОЙСТВО ЧАСТОТНОЙ АВТОПОДСТРОЙКИ | 1972 |

|

SU342275A1 |

| ПАССИВНЫЙ КВАНТОВЫЙ СТАНДАРТ ЧАСТОТЫ | 1984 |

|

SU1241959A1 |

| СПОСОБ УВЕЛИЧЕНИЯ ПОЛОСЫ ЗАХВАТА СИСТЕМЫ ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ С ЗНАКОВЫМ ЛОГИЧЕСКИМ ФАЗОВЫМ ДИСКРИМИНАТОРОМ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2015 |

|

RU2582878C1 |

| АСТАТИЧЕСКОЕ ЗВЕНО УСТРОЙСТВА АВТОМАТИЧЕСКОЙ ПОДСТРОЙКИ ЧАСТОТЫ | 1972 |

|

SU333670A1 |

| ЦЕЗИЕВЫЙ СТАНДАРТ ЧАСТОТЫ | 1994 |

|

RU2076411C1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Устройство фазовой синхронизации | 1982 |

|

SU1116545A1 |

| Устройство фазовой автоподстройки тактовой частоты | 1989 |

|

SU1721834A1 |

| Устройство компенсации сдвига частот | 1985 |

|

SU1316097A2 |

L

Т9J ±±|-t: J

Авторы

Даты

1974-05-15—Публикация

1972-02-10—Подача