Изобретение относится к вычислительной технике и предназначено, например, для электронной цифровой вычислительной системы, выполненной на функциональных узлах, с большой степенью интеграции.

Известно устройство для кодирования и декодирования, содержащее регистр кодирования - декодирования, соединенный через выходной коммутатор с блоком сумматоров по модулю 2, дешифратор ошибки, входы которого соединены с блоком сумматоров по модулю 2, а выходы которого и выходы блока сумматоров по модулю 2 - через входной коммутатор с регистром кодирования-декодирования, блок управления, соединенный с запоминающим регистром, с регистром кодирования - декодирования и с регистром мощности корректирующего кода, дешифратор, соединенный с индикатором режима, с регистром мощности корректирующего кода и с входным и выходным коммутаторами.

Однако при использовании в схеме корректирующего кода, исправляющего минимальное число ошибок, затраты оборудования наименьшие, но при увеличении числа отказов его мощности будет недостаточно чтобы исправить все ошибки. С другой стороны, применяя в схеме коррекции ошибок при небольшом числе отказов кода,, исправляющие большое количество ошибок, часть мощности кода не будет использована.

Цель изобретения - повыщение надежности работы устройства.

Поставленная цель достигается тем, что в устройство введены схема преобразования, схема сравнения кодов и схема округления, причем выходы дешифратора ошибки соединены с входами схемы преобразования, выход

которой соединен с входом запоминающего регистра, входы схемы сравнения кодов соединены с выходами запоминающего регистра и регистра мощности корректирующего кода, а выход - с входом регистра мощности корректирующего кода, выход дешифратора соединен с регистром кодирования-декодирования через схему округления.

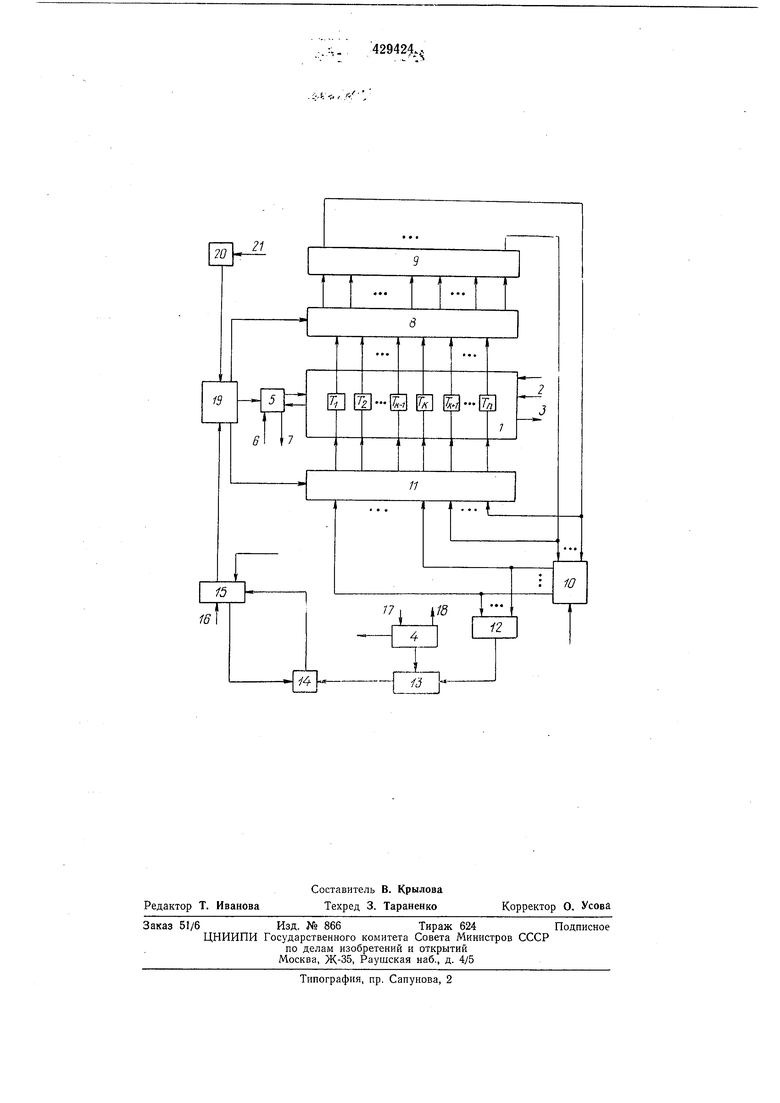

На чертеже изображена блок-схема предлагаемого устройства для кодирования и декодирования.

Устройство содержит регистр 1 кодирования - декодирования (РКД), который имеет вход 2 и выход 3. Регистр соединен с блоком 4 местного управления (БМУ) и содержит п

триггеров Тг-Т.

Из п разрядов РКД 1 к информационных разрядов соединены со схемой 5 округления (СО), имеющей информационный вход 6 и выход 7. Содержимое всех триггеров РКД 1

подается через выходной коммутатор 8 на блок 9 (п-s) сумматоров по модулю 2, где п - общее количество разрядов РКД, as - минимальное количество информационных разрядов в РКД 1 при максимальной мощности корректирующего кода (МКК), т. е. при максимальной МКК. Все (я-s) выходов соединены с входами дешифратора 10 ошибки (ДО) и с входами входного коммутатора 11, который связан с разрядами РКД 1. Все k выходов ДО 10 соединены с входным коммутатором 11, где k - максимальное количество информационных разрядов в регистре 1 при минимальной МКК и я const. Выходы ДО 10 соединены также через схему 12 преобразования числа возбужденных шин в код (СП) и запоминающий регистр 13 со схемой сравнения кодов 14, другой вход которой связан с регистром 15 мощности корректирующего кода (РМКК). Регистр 15 имеет вход 16 и соединен с выходом схемы 14 сравнения кодов (ССК) и с БМУ 4, который связан с регистром 13. Блок 4 имеет вход 17 и выход 18. РМКК 15 через дешифратор 19 соединен с коммутаторами 8 и 11 и схемой округления 5. Другой вход дешифратора 19 подключен к выходу индикатора режима 20, который имеет вход 21. Выход РМКК 15 соединен с дещифратором ошибок 10. Устройство работает следующим образом. При кодировании информационное слово поступает по входу 6 через схему округления 5 в / информационных разрядов РКД 1, где . Количество разрядов /, отводимое для представления информации (т. е. точность), зависит от применяемой мощности корректирующего кода (т. е. от количесгва ошибок, которые необходимо исправить). Чем больше кратность ошибок, тем меньще /, т. е. точность представления информации по мере увеличения ошибок уменьшается. Рассмотрим процесс кодирования на примере использоваа7 ао ; 8 2 i 9 83 . а ®

Видно, что при неизменной общей длине кодового слова (,12 const) по мере увеличения мощности корректирующего кода (с 1 до 3) количество информационных разрядов падает (с 8 до 2). При отсутствии ошибок устройство настраивается таким образом, чтобы исправлять только одну ошибку (гарантированно). Для этого МКК-1 подается по входу 16 в РМКК 15. В индикатор режима (ИР) 20 по входу 21 поступает код операции (кодирование). При поступлении k информационных разрядов (в данном примере 8) они записывают в РКД 1 в первые k триггеров (т. е. Гь 2, - ,7, Гв). Коммутатор 8, управляемый дешифратором 19 в соответствии с содержимым РМКК 15, обеспечивает подключение к первому сумматору из блока 9 выходов Гь Та, Тг, Ть, Т, Тъ Та; ко второму - выходов TI, TZ, TS, Т,, Те и т. д., т. е. в соответствии с выражениями (1). Выходы первого, второго, третьего и четвертого сумматоров из блока 9 поступают на ДО 10 и на коммутатор 11. Последний также управляется

через дешифратор 19 содержимым РМКК 15 и ИР 20. Выходы сумматоров через коммутатор 11 поступают на триггеры Та, ю, Гц, Тк (для рассматриваемого примера). При поступлении на ДО 10 содержимого

избыточных разрядов на выходе дешифратора 10 нулевой код, так как поступившая на ия групповых (п, /е) кодов, оптимальных для случая независимых ошибок. Пусть для представления информации треуется 8 разрядов, т. е. . Тогда код, исравляющий одну ошибку, т. е. , бует иметь вид (12, 8), причем аь az, as, а, а&, б, aj, us - это информационные разряды; д, аю, ац, aiz - избыточные разряды, котоые определяются выражениями .Ф a eaeoa eag , а . © -, ,« 1Цадс15® 7 i а. а|2 а1®аз©а4ба5Фа.8 , г да знак © сзиа.ает с:/мм/ по ,-:заулю 2 Для код имеет вид (12, 4), где «ь 2, из, Й4 - информационные разряды, остальные - избыточные, определяемые выражениямиas а Ф а 2.; аб а1Фаз, &7 2 ® 3 i ag а2® е а4 г ЗоФ а4 1 ® а2® а. а, L15® а а 12 а Для код имеет вид (12, 2), где «i и аз - информационные разряды. Остальные разряды являются избыточными. 11 а © а2 i aj2 a-j ® а 2(.т)

зыход дешифратора комбинация является разрешенной. Предположим, информация имеет вид 10100110.

Тогда в соответствии с выражениями (1) ей будет соответствовать кодовое слово 101001100100, где четыре последние цифры являются избыточными. Кодовое слово считывается с выхода 3 РКД 1.

а, © аз® адэаб® ag© ад о J а, © а2 ® а;, ® а4 е ае ® ащ О ;

aj©a2©a @a5®aY®a o,(4)

а © ад© Эд® ag© 3.

При выполнении равенств на входе ДО 10 нулевой код, т. е. ошибки нет. Содержимое первых k разрядов поступает па схему округления 5 и, так как , практически без округления поступает на выход 7.

Предположим, что в кодовом слове есть ошибки, например, в пятом разряде. Принятое на РКД 1 ошибочное кодовое слово имеет вид 101011100100. Тогда при проверке выражений согласно (4) на выходе блока 9 появляется вектор ошибки 1011, который после дешифрирования в ДО 10 исправляет содержимое Га на обратное, т. е. в О, что будет соответствовать коррекции данной ошибки. Одновременно установочный сигнал с выхода дешифратора 10 через схему СП 12 и регистр 13 сравнивается на ССК 14 с содержимым РМКК. При равенстве содержимого РМКК и регистра 13 ССК выдает сигнал «+ з регистр 15. Таким образом, при i ошибках применяется MKK(t4-l)- Это позволяет автоматически исправлять ошибки по мере их появления. В рассматриваемом примере для одной ошибки теперь применяется М1(. Этому соответствует групповой код (12, 4), где под информационные разряды отводится четыре разряда. Остальные разряды определяются согласно выражениям (2). Теперь информационное слово 10100110, сосчитанное из РКД 1, в схеме СО 5 округляется до 10110000 и вновь записывается в регистр 1. Кодовое слово, образованное согласно выражениям (2), имеет вид 101110100100. При декодировании на выходе 7 СО 5 получают четыре разряда, а остальпые заполняют нулями, т. е. декодированное информационное слово будет иметь вид 10110000.

Если произойдет еще одна ошибка, то в регистре 13 будет также, как и в РМКК записана 2, и ССК выдает «+ в регистр 15, т. е. . Тогда схема СО 5 округляет 10110000 до 11000000 и записывает в РКД 1.

При декодировании кодовое слово поступает па вход 2 РКД 1. По входу 16 на РМКК 15 поступает величина МКК (в рассматриваемом примере МКК-1). В индикатор режима 20 по входу 21 поступает код операции (декодирование). Выходной коммутатор 8 обеспечивает проверку информационных и контрольных разрядов согласно (1), т. е.

Закодированное в соответствии с выражениями (3) кодовое слово будет иметь вид 111111111000.

Таким образом, предлагаемое устройство адаптируется к имеющей место ситуации и позволяет не терять информацию по мере увеличения числа ошибок, хотя бы за счет снижения ее точности.

Предмет изобретения

20

Устройство для кодирования и декодирования, содержащее регистр кодирования - деодирования, соединенный через выходной

коммутатор с блоком сумматоров по модулю 2, дещифратор ошибки, входы которого соединены с блоком сумматоров по модулю 2, а выходы которого и выходы блока сумматоров по модулю 2 - через входной коммутатор с регистром кодирования - декодирования, блок управления, соединенный с запоминающим регистром, с регистром кодирования - декодирования и с регистром мощности корректирующего кода, дешифратор, соединенный с

индикатором режима, регистром мощности корректирующего кода и входным и выходным коммутаторами, отличающееся тем, что, с целью повышения надежности работы устройства, в него введены схема преобразования, схема сравнения кодов и схема округления, причем выходы дешифратора ошибки соединены с входами схемы преобразования, выход которой соединен со входом запоминающего регистра, входы схемы сравнения кодов соединены с выходами запоминающего регистра и регистра мощности корректирующего кода, а выход - с входом регистра мощности корректирующего кода, выход дещифратора соединен с регистром кодирования -

декодирования через схему округления.

.4.S:4...i

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО„. -..,-•. ."р л С^аог^'-.---'^--:: '•^k^Vfi''-'- | 1973 |

|

SU375675A1 |

| Устройство для декодирования с коррекцией ошибок | 1985 |

|

SU1292189A1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2008 |

|

RU2383104C2 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2302701C1 |

| СПОСОБ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2011 |

|

RU2450436C1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1048520A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU926726A1 |

| Запоминающее устройство с исправлением дефектов и ошибок | 1987 |

|

SU1536445A1 |

| Логическое запоминающее устройство | 1977 |

|

SU733024A1 |

| КОДЕК ПОМЕХОУСТОЙЧИВОГО ЦИКЛИЧЕСКОГО КОДА | 2003 |

|

RU2254676C2 |

Даты

1974-05-25—Публикация

1971-11-29—Подача