(54) УСТРОЙСТВО ДЛЯ ПЕРЕМНОЖЕНИЯ ДВУХ ЧАСТОТНО-ИМПУЛЬСНЫХ СИГНАЛОВ

1

Изобретение относится к автома тике и вычислительной технике и может быть использовано при построении быстродействующих частотно-импульсных вычислительных устройств, обладающих высокой точностью в статическом и динамическом режимах работы.

Известно устройство для перемножения двух частотно-импульсных сигналов, содержащее счетчики, регистры блоки управления, делитель частоты и генератор опорной частоты til.

Недостатками устройства являются наличие ослабления выходного oiгнала, пониженное быстродействие и недостаточная равномерность следования выходных импульсов.

Наиболее близким к предлагаемому является устройство для перемножения двух частотно-импульсных сигналов, содержащее реверсивный счетчик, подключенный суммирующим и вычитающим входами ссютветственно к выходам двух множительно-делительных

блоков, первый из которых соединен первым входом с шиной ввода первого сомножителя, а вторым и третьим входами - с шина№1 ввода первого и второго частотно-импульсных масштабных сигналов, причем второй множительно-делительный блок подключен первым входом к выходной шине устройства, вторым входом - кмиине ввода второго сомножителя, а треtoтьим входом - к шине ввода третьего частотно-импульсного масштабного сигнала, причем кодовый выход реверсивного счетчика с первым входом двоичного умножителя, подцключенного вторым входом к шине опорной частоты, а выходом - к вы/ходной шине устройства .

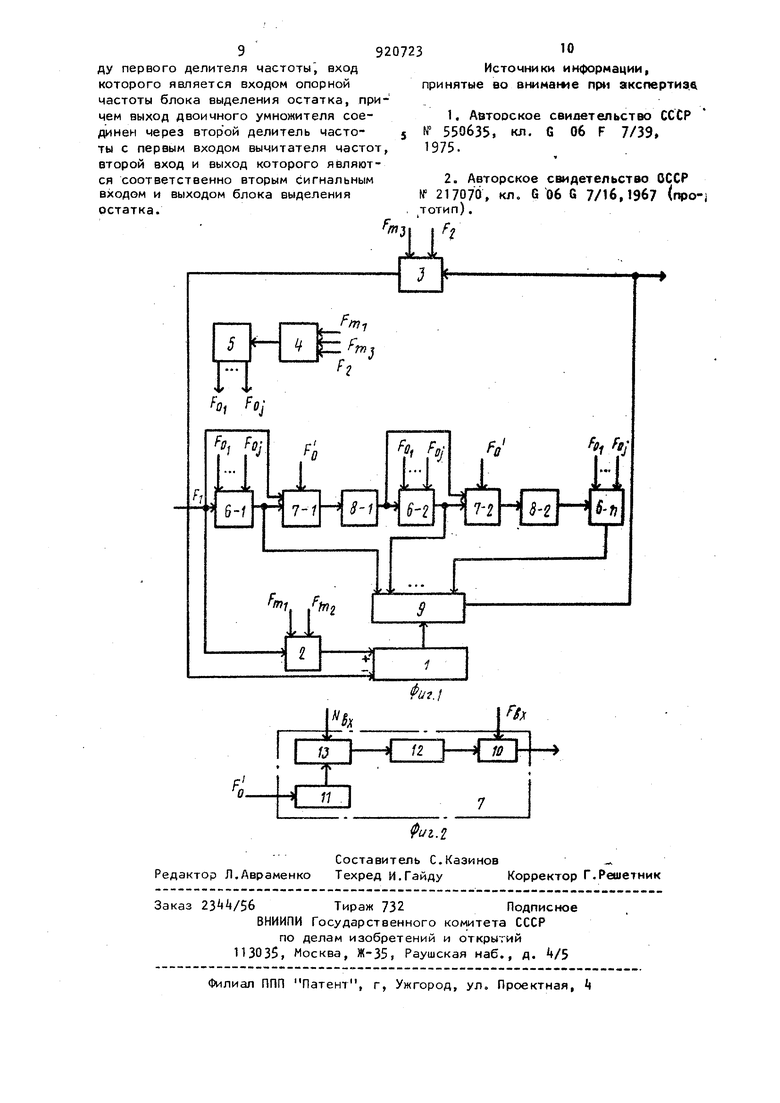

Недостатю1 устройства - низкое быстродеистоке при предъявлении вы20соких требований к томности перемножения и неравномерный характер выходной импульсной последовательности . Цель изобретения - повышение быстродействия и точности в динамическом режиме при сохранении точности в статическом режиме С этой целью в устройство для перемножения двух частотно-импульсных сигналов, содержащее реверсивный счетчик, подключенный суммирующим и вычитающим входами соответственно к выходам двух множительноделительных блоков, первый из которь1х соединен первым входом с шиной ввода первого сомножителя ,а вторым и третьим входами - к шинам ввода первого и второго частотно-импульсных масштабных сигналов, причем второй множительно-делительный блок подклю чен первым входом к выходной шине устройства, вторым входом - к шине ввода второго сомножителя, а третьим входом - к шине ввода третьего частотно-импульсного масштабного сигнала, введены преобразователь код - напряжение - частота, группа преобразователей частота - код поразрядного взвешивания, группа из (п-1) блоков выделения остатка (где п - количество преобразователей час тота - код поразрядного взвешивания группа из (п-1) умножителей частоты, делитель частоты и третий множительно-делительный блок, соединен ный входами с шиной ввода второго сомножителя и с шинами ввода первого и третьего частотно-импульсных масштабных сигналов, а выходом - с входом делителя частоты, выходы раз рядов которого подключены к входам опорных частот преобразователей частота - код поразрядного взвешивания, примем каждый i-ый (1 i : п-1) блок выделения остатка соединен первым и вторым сигнальными входами соответственно с кодовым выходом и с сигнальным входом i-ro преобразователя частота - код поразрядного взвешивания, входом опорной частоты - с шиной ввода постоянной опорной частоты, а выходом - с входом |-го умножителя частоты, причем каж дый i-ый умножитель частоты соединен выходом с сигнальным входом (i + 1)-го преобразователя частота код поразрядного взвешивания, сигнальный вход первого преобразовател частота - код поразрядного взвешивания подключен к шине ввода первог сомножителя, а преобразователь код напряжение - частота соединен входа 4 ки старших разрядов с кодовыми выходами преобразователей частота - код поразрядного взвешивания, входами младших разрядов - с выходами разрядов реверсивного счетчика, а выходом - с выходной шиной устройства, Кроме того каждый блок выделения остатка содержит вычитатель частот, делители частоты и двоичный умножитель, первый вход которого является первым сигнальным входом блока выделения остатка, а второй вход подключен к кодовому выходу первого делителя частоты, вход которого является входом опорной частоты блока выделения остатка, причем выход двоичного умножителя соединен через второй делитель частоты с первым входом вычитателя частот, второй вход и выход которого являются соответственно вторым сигнальным-входом и выходом блока выделения остатка. На фиг.1 изображена блок-схе( устройства; на фиг.2 - структурная схема блока выделения остатка Устройство ДЛЯ перемножения двух частотно-импульсных сигналов содержит (фиг.1) реверсивный счетчик 1, подключенный суммир 4)ощим и вычитающим входами соответственно к выходам двух множительно-делительных блоков 2 и 3. Первый блок 2 соединен первым входом с шиной ввода первого сомножителя F-,, а вторым и третьим входами - с шиной ввода первого и второго частотно-импульсных масштабных сигналов F гп и Второй блок 3 подключен первым входом к выходной шине устройства, вторым вхохом - к шине ввода в-,-орого сомножителя Fij, а третьим входом - к шине ввода третьего частотно-масштабного сигнала РГО. Третий множительно-делительный блок k соединен входами с шиной ввода второго сомножителя с шинами ввода первого и третьего частотно-импульсных масштабных сигналов гг,- подключен выходом к входу делителя 5 частоты, Выходы разрядов делителя 5 частоты соединены входами опорных частот f01 F 00. преобразователей 6-1, 6-2,..„, 6-п частота - код поразрядного взвешивания. Каждый i-ый (1 f i п-1) блок 7-i выделения остатка соединен первым и вторым сигнальными входами соответственно с кодовым выходом и с сигиальным входом i-ro преобразователя 6-i, входом опорной частоты - с шиной постоянной опорной частоты Рд, а. выходом - с 1-го умножителя 8-1 частоты Каждый 1-ый умножитель 8-i соединен выходом с сигналь ным входом (i + 1)-го преобразователя 6-1 сигнальный вход первого преобразователя 6-1 подключен к шине ввода первого сомножителя F-j, Преобразователь 9 код - напряжение частота соединен входами старших разрядов с кодовыми выходами преобразователей 6-1, бтЯ,,..., 6-п, входами младших разрядов - с выходами разрядов счетчика 1, а выходом - с выходной шиной устройства. Каждый из блоков , ,..о, 7-(п-1) выделения остатка может быт выполнен (фиГо2), содержащим вычитатель 10 кодов, делители 11 и 12 частоты и двоичный умножитель 13, первый вход которого является первым сигнальным входом Ng блока 7, а второй вход подключен к кодовому выходу первого делителя 11 частоты, вход которого является входом опорной частоты FQ блока 7 Выход умножителя 13 соединен через второй делитель 12 частоты с первым входом вычитателя 10 частот, второй вход и выход которого являются соответственно вторым сигнальным входом и выходом блока 7 Преобразователи 6-1, 6-2,,.., 6-п, блоки 7-1,.,., 7-(п-1) выделения остатка и умножители 8-1,..., 8-(п-1) образуют преобразователь частота - код, использующий принцип поразрядно-группового взвеимвания. При работе устройства множительно-делительные блоки 2 и 3, реверсивный счетчик 1 и преобразователь 9 код - напряжение - частота образуют устройство, основанное на компенсационном методе работы и моделирующе зависимость F m-1 FZ 1 fflQ. ПМ 5 Преобразователи 6-1,..., 6-п, блоки 7-1,0.., 7(п-1), умножители 8-1,.„., 8-2 совместно с множительно-делительным блоком k, делителем 5 частоты и преобразователем 9 код - напряжение - частота образуют устройство, в основу которого положен метод преобразования, т.е. работа этих узлов заключается в пер воначапьном преобразовании первого сомножителя F в код, затем в частоту. При этом вторая операция совмещена с операцией умножения кода на второй сомножитель Ffj. Условием совместимости, работы этих двух устройств является необходимость обеспечения идентичности их моделирующих зависимостей. (.. Принимая во внимание принцип работы преобразователя 6 запишем выражение для его кода где п - число выходных разрядов преобразователя;РОД- опорная частота; откуда соотношение для результирующей частоты равно: 2П-1 - .(3) Fon где. с коэффициент передачи преобразователя 9 код -напряжение частота. Приравнивая выражения (1) и (З) и ешая относительно ,получим и -Я .. . Таким образом, если опорная частота преобразователя частота -i код поразрядно - группового взвешивания подчиняется выражению (), то моделирующие зависимости двух устройств (каналов) идентичны. Функцией блока является моделирование зависимости (6). В таблице приводятся технические характеристики устройства для перемножения двух частотно-импульсных сигналов, в предположении, что один из сомножителей изменяется скачком от нуля до принятого значения, второй - постоянен и равен 10 Гц, число умножителей частоты равно 7, частота переключения элементов устройства 10 Гц, R,(()f10 Гц, В таблице использованы обозначения с - заданная относительная точ™ ность; - относительная динамическая погрешность; Тц - вели1 1на времени переходного процесса.

Таким образом рассмотренное устройство по сравнению с известным позволяет повысить быстродействие и точность в динa 1чecкoм примерно на три порядка, устранить ослабление в результирующем сигнале и обеспечить.сочетание высокой статической точности с динамической при высоком быстродействии операции перемножения

Формула изобретения

1. Устройство для перемножения двух частотно-импульсных сигналов, содержащее реверсивный счетчик, подключенный суммирующим и вычитающим входами соответственно к выходам двух множительно-делительных блоков, первый из которых соединен первым входом с шиной ввода первого сомножителя, а вторым и третьим входами - с шинами ввода первого и второго частотно-импульсных масштабных сигналов, причем второй множительно-делительный блок подключен первым входом к выходной шине устройства, вторым входом - к шине ввода второго сомножителя, а третьим входом - к шине ввода третьего частотно-импульсного масштабного сигнала, отличающееся тем, что, с целью повышения быстродействия. ;И точности в динамическом режиме при сохранении точности в статическом режиме, в устройство введены преобразователь код - напряжение - частота, группа преобразователей частота - код поразрядного взвешивания, группа из Сп-1 блоков выделения остатка (где л количество преобразователей частота - код поразрядного взвешивания},, группа из

(n -1J умножителей частоты, делитель :частоты и третий множительно-делительный блок, соединенный входами с шиной ввода второго сомножителя и с шинами ввода первого и третьего частотно-импульсных масштабных .сигналов, а выходом - с входом делителя частоты, выходы разрядов которого подключены к входам опорных частот преобразователей частота код поразрядного взвешивания, причем каждый i-ый (1 4 1 п-1) блок выделения остатка соединен первым и вторым сигнальными входами соответственно с кодовым выходом и с сигнальным входом i-ro преобразователя код - частота поразрядного взвешивания, входом опорной частоты - с шиной ввода постоянной опорной частоты, а выходом - с входом i-ro умножителя частоты, каждый i-ый умножитель частоты соединен выходом с сигнальным входом (5 4- 1) го преобразователя частота - код поразрядного взвешивания, сигнальный вход первого преобразователя частота - код поразрядного взвииивания подключен к шине ваода первого сомножителя, а преобразователь код напряжение - частота соединен входами старших разрядов с кодовы№1 выходами преобразователей частота - код поразрядного взвешивания, входа 1 младших разрядов - с выходами разрядов реверсивносо счетчика, а выходом - с выходной шиной устройства.

2, Устройство по п 1, о т л и ч а-ю щ е е с я тем, что каждый блок выделения остатка содержит БЫ мтатель частот, делитель частоты 1/ двоичный умножитель, первый вход которого является первым сигнальным 8ХОДОМ блока выделения остатка, второй вход подключен к кодовому выхо9920723

ду первого делителя частоты , вход которого является входом опорной частоты блока выделения остатка, причем выход двоичного умножителя соединен через второй делитель частоты с первым входом вычитателя частот, второй вход и выход которого являются соответственно вторым сигнальным входом и выходом блока выделения остатка.

Источники информации, принятые во внинаже npti зкспертиэд

1. А&тооское свиоетельство СССР 5 N° 550635, кл. G 06 F 7/39,

2. Авторское свидетельство ОССР

№ 217070, кл. 6 06 G 7/16,1967 (про-; , дотип).

Ff

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-делительное устройство | 1977 |

|

SU788128A1 |

| Частотно-импульсное вычислительное устройство | 1980 |

|

SU881744A1 |

| Способ преобразования частотно- импульсного сигнала в код и устройство для его осуществления | 1979 |

|

SU773927A1 |

| Множительно-делительное устройство | 1978 |

|

SU813419A1 |

| Множительно-делительное устройство | 1981 |

|

SU1015373A1 |

| Частотно-импульсная следящаяСиСТЕМА | 1978 |

|

SU798696A1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1995 |

|

RU2097829C1 |

| Устройство для дифференцирования частоты повторения импульсов | 1974 |

|

SU525117A1 |

| Частотно-импульсное делительное устройство | 1978 |

|

SU763914A1 |

| Множительно-делительное устройство | 1979 |

|

SU840942A1 |

Авторы

Даты

1982-04-15—Публикация

1979-08-30—Подача