1

Устройство относится к автоматике н вычислительной технике и иредназначено для испытания преобразователей угла в код.

Иэ-вест7но устройство, позволяющее определять правильность чередования кода испытуемого иреобразователя и величину ошибю в выходном коде и содержащее преобразователь импульсного кОлТ.а в потенциальный мультивибратор, счетчики, триггеры, дешифратор, дифференцирующие схемы, логические схемы, блок индикации. Оно характеризуется неполной достоверностью результата проверки правильности функционирования преобразователя. Это объясняется тем, что правильность очередности смены выходного кода преобразователя не является основанием для вывода о правильном его функционировании ДругИМ условием должно являться обязательное соответствие выходного кода заданному угловому положению вала иреобразователя.

Целью изобретения является повышение достоверности результатов проверки преобразователей угол-код.

Предлагаемое устройство позволяет осуществлять проверку выходного кода в условиях его строгой при вязки к углу поворота вала преобразователя, а также в случае неправильного выходного кода определять величину и знак его ошибки. Устройство предназначено д;ля ис ытан1п преоСфазоватслси угла в код при их производстве (прпемо-сдаточных, типовых и т. д.), а также, учитывая возможность задания разной величины - времениого сдвига эталонными и реальными сигналами, может найти применение при различных исследованиях преобразователей.

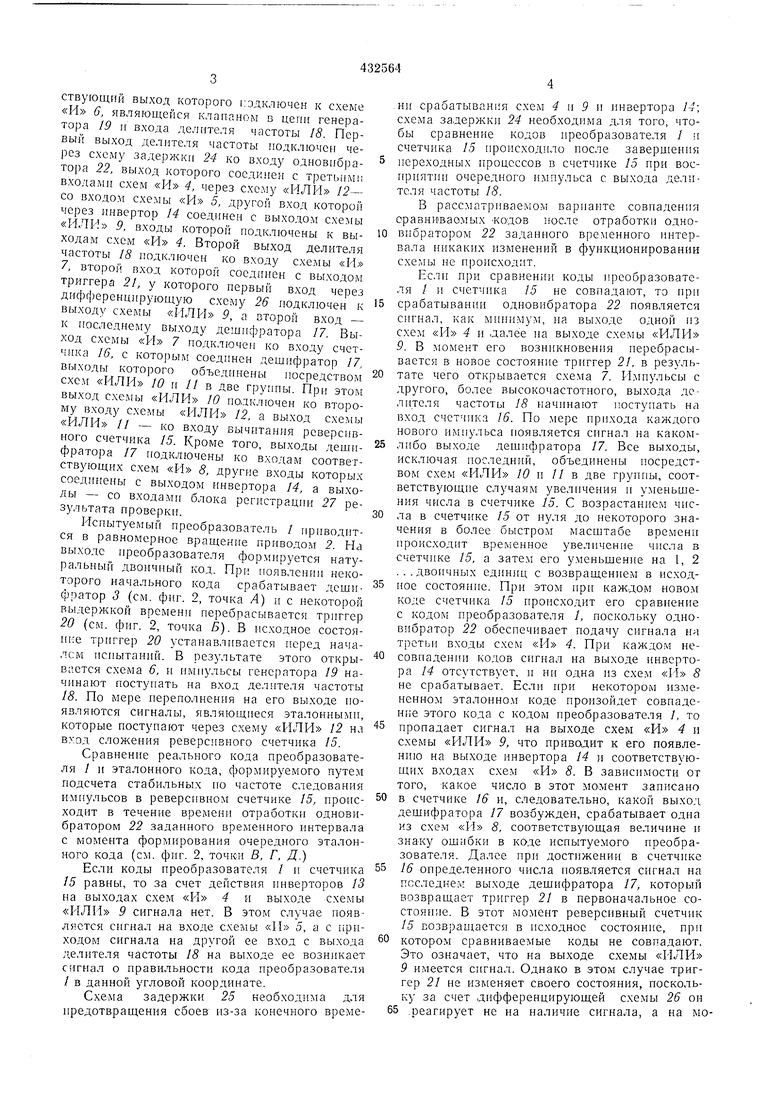

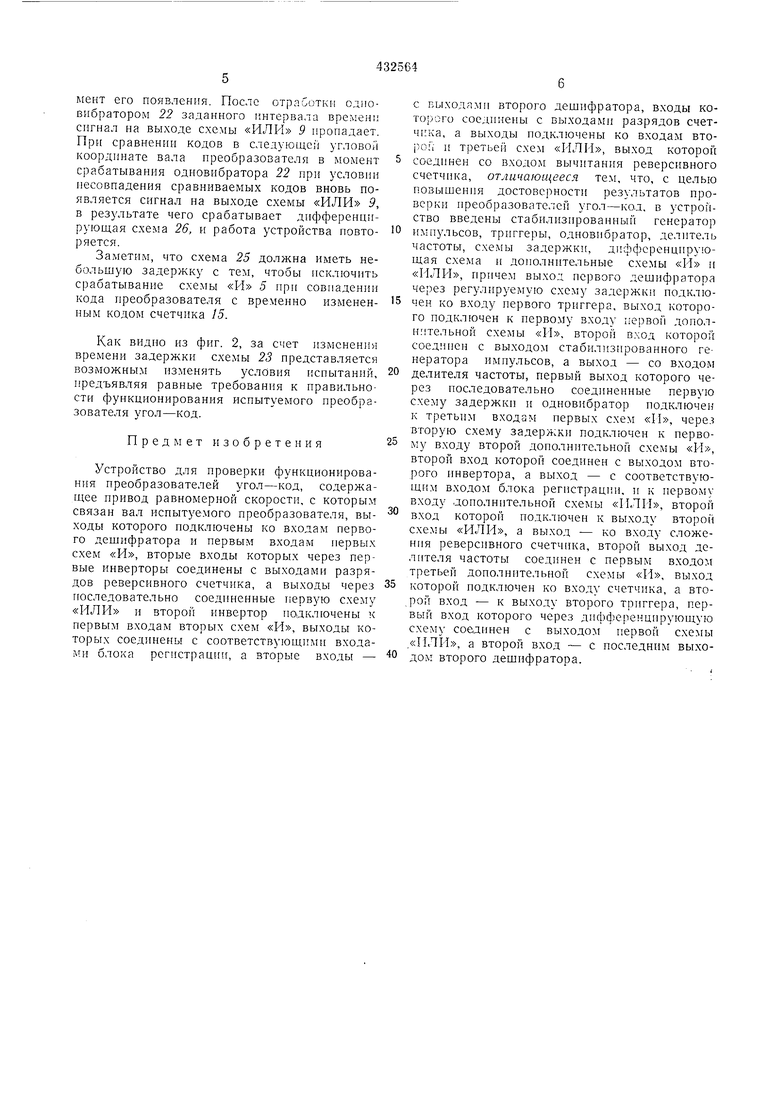

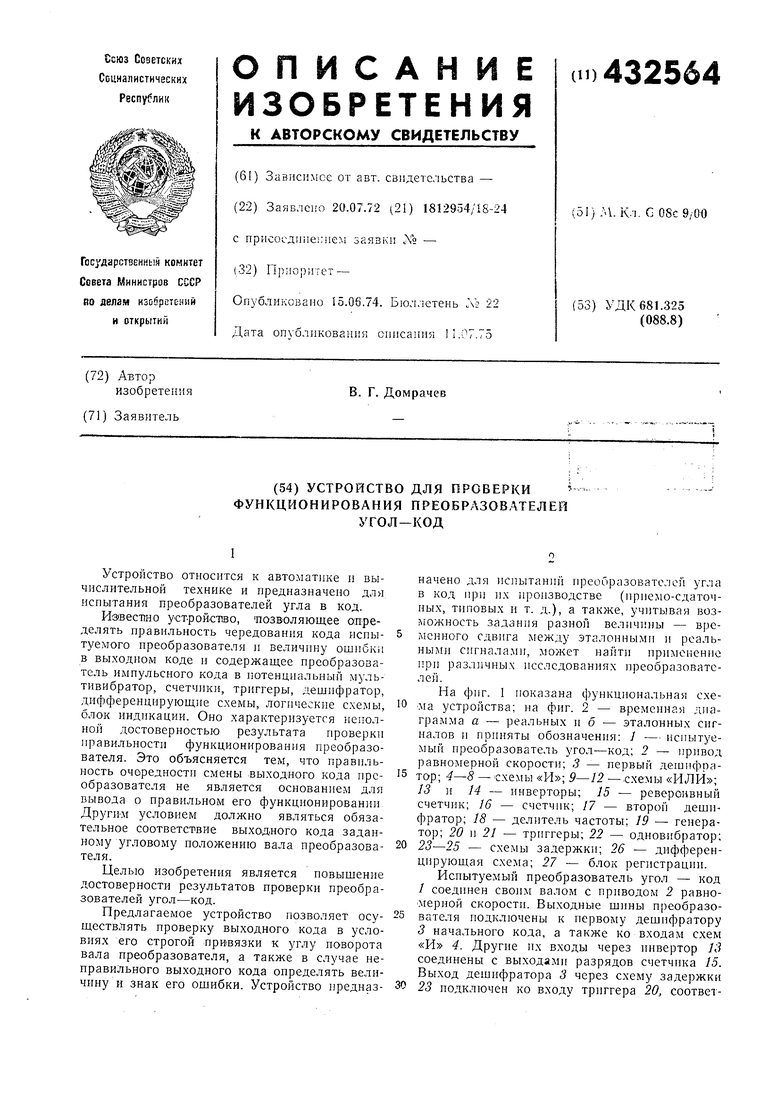

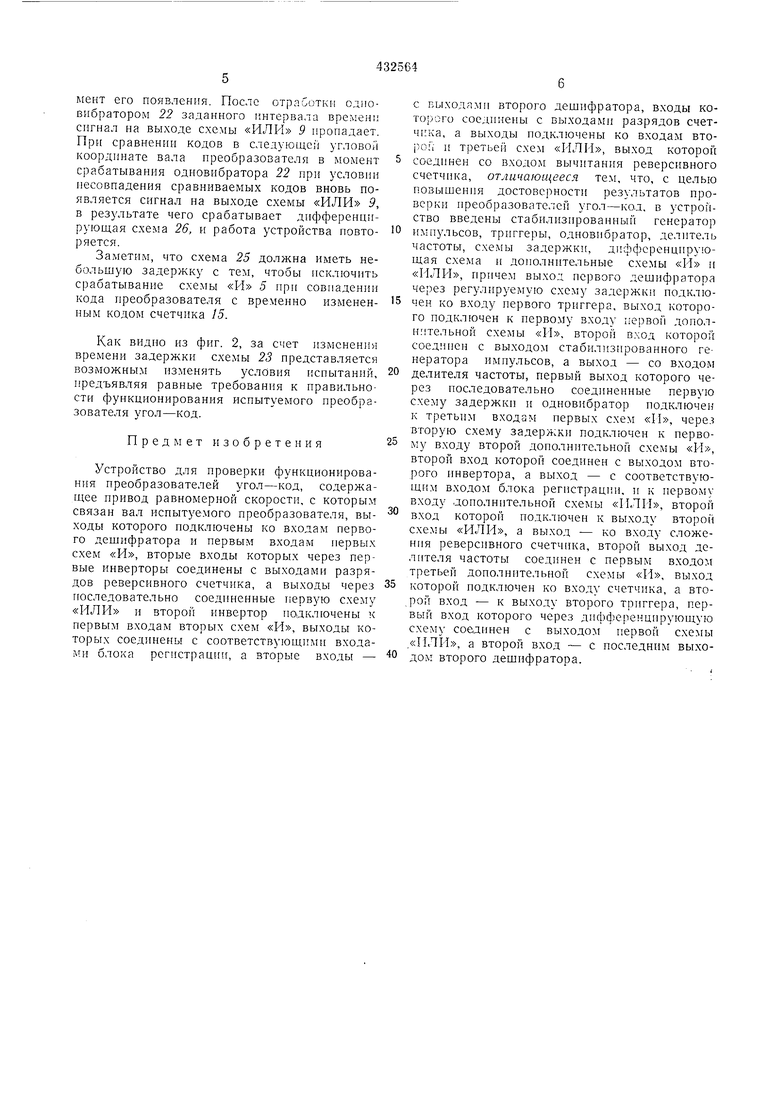

На фиг. 1 показана функциональная схеМа устройства; на фиг. 2 - временная диаграмма а - реальных п б - эталонных сигналов и приняты обозначения: / - испытуемый преобразователь угол-код; 2 - равномерной скорости; 3 - первый дешифратор; 4-8 - схемы 9-12 -схемы 13 и 14 - инверторы; 15 - реверсивный счетчик; 16 - счетчик; 17 - второй дешифратор; 18 - делитель частоты; 19 - генератор; 20 п 21 - триггеры; 22 - одновибратор;

23-25 - схемы задержки; 26 - дифференцирующая схема; 27 - блок регистрации.

Исиытуемый преобразователь угол - код / соединен своим валом с приводом 2 равноМерной скорости. Выходные шины преобразователя подключены к первому дешифратору 3 начального кода, а также ко входам схем «И 4. Другие их входы через инвертор 13 соединены с выходами разрядов счетчика 15. Выход дешифратора 3 через схему задержки

23 подключен ко входу триггера 20, соотве ствующии выход которого сэдключен к схеме «И 6, являющейся клапаном в цепи генератора 19 и входа делителя частоты 18 Первый выход делителя частоты подключен через схему задержки 24 ко входу одиовнбратора //, выход которого соедкиен с трет1 им| входами схем «И 4, через схему «ИЛИ 12 со входом схемы «И 5, другой вхот которой через инвертор М соедпнеи с выходом схемы тлк J, входы которой подключены к выходам схем «И 4. Второй выход делителя частоты 18 подключен ко входу схемы «И /, второй вход которой соединен с выходом триггера 21, у которого первый вхо через дифференцирующую схему 26 подключен к выходу схемы «ИЛИ 9, а второй вход к последнему выходу дещпфратора 17 Выход схемы «И 7 подключен ко входусчетНка /6, с которым соедпнен дещифратор /7 выходы которого объединены гюсредством схем «ИЛИ W и // в две группы. При это выход схемы «ИЛИ W подключен ко второ шшТп , // - ко входу вычитания реверсив1Тто я ;Г - Р° дешпФратора /7 подключены ко входам соответствующих схем «И 8, другие входы которых соединены с выходом инвертора М, а выходы - со входами блока регистрации 27 результата проверки. Испытуемый преобразователь / ирпводптся в равномерное вращение приводом 2 На выходе иреобразователя формируется натуральный двоичный код. При появлении некоторого начального кода срабатывает дещифратор 3 (см. фиг. 2, точка Л) и с некоторой выдержкой времени перебрасывается триггер 20 (см. фиг. 2, точка Б). В исходное состояние триггер 20 устанавливается иеред началом испытаний. В результате этого открывается схема 6, и импульсы генератора 19 начинают поступать на вход делителя частоты 18. По мере переполнения на его выходе появляются сигналы, являющиеся эталонными, которые поступают через схему «ИЛИ 12 на вход сложения реверсивного счетчика 15. Сравнение реального кода преобразователя / и эталонного кода, формируемого путем подсчета стабильных по частоте следования импульсов в реверсивном счетчике 15, происходит в течение времени отработки одновибратором 22 заданного временного интервала с момента формирования очередного эталонного кода (см. фиг. 2, точки В, Г, Д.) Если коды преобразователя / п счетчика 15 равны, то за счет действия инверторов 13 на выходах схем «И 4 и выходе схемы «ИЛИ 9 сигнала нет. В этом случае появляется сигнал на входе схемы «И 5, а с приходом сигнала на другой ее вход с выхода делителя частоты /5 на выходе ее возникает сигнал о правильности кода преобразователя / в данной угловой координате. Схема задержки 25 необходима для предотвращения сбоев из-за конечного времени срабатыван1 я схем и 5 и инвертора 14; схема задержки 24 необходима для того, чтобы сравнение кодов иреобразователя / и счетчика 15 происходило после заверщенпя переходных процессов в счетчике /5 при восириятип очередного импульса с выхода делителя частоты 18. В рассматриваемом вариапте совпадения сравниваемых кодов после отработки одновибратором 22 заданного временного интервала никаких изменений в функционировании схемы не происходпт. Еслп при сравнении коды преобразователя / и счетчпка 15 не совпадают, то при срабатывании одновибратора 22 появляется сигнал, как минимум, иа выходе одной из схем «И 4 и далее на выходе схемы «ИЛИ 9. В момент его возникновения иеребрасывается в новое состояние триггер 21, в результате чего открывается схема 7. Импульсы с другого, более высокочастотного, выхода делителя частоты 18 начинают поступать на вход счет-1ика 16. По мере прпхода каждого нового им 1ульса гюявляется сигнал на какомлибо выходе дешифратора 17. Все выходы, исключая последний, объединены посредством схем «ИЛИ 10 п // в две группы, соответствующпе случаям увелпчения и уменьщения числа в счетчике 15. С возрастанием числа в счетчике 15 от нуля до некоторого значения в более быстром масштабе времени происходит временное увеличение числа в счетчике 15, а затем его уменьшение на 1, 2 ...двоичных едпнщ, с возвращением в исходное состояние. При этом при каждом новом коде счетчпка 15 пропсходит его сравнение с кодом преобразователя /, поскольку одновибратор 22 обеспечивает подачу сигнала на третьи входы схем «И 4. При каждом несовпадении кодов сигнал на выходе инвертора 14 отсутствует, п ни одна из схем «И 5 не срабатывает. Если при некотором измененном эталонном коде произойдет совиадение этого кода с кодом преобразователя /, то пропадает сигнал на выходе схем «И 4 и схемы «ИЛИ 9, что приводит к его появлению на выходе инвертора 14 и соответствующих входах схем «И 8. В зависимости от того, какое число в этот момент записано в счетчике 16 и, следовательно, какой выход дешифратора 17 возбужден, срабатывает одна из схем «И 8, соответствующая величине п знаку ошибки в KO.ie испытуемого преобразователя. Далее при достижении в счетчике 16 определенного числа появляется сигнал на последнем выходе дещифратора 17, который возвращает триггер 21 в первоначальное состояние. В этот мо.мент реверсивный счетчик /5 возвращается в исходное состояние, при котором сравниваемые коды не совпадают. Это означает, что на выходе схемы «ИЛР1 9 имеется сигнал. Однако в этом случае триггер 21 не изменяет своего состояния, поскольку за счет дифференцирующей схемы 26 он .реагирует не на наличие сигнала, а на момент его появления. После отработки одновибратором 22 заданного интервала времени сигнал на выходе схемы «ИЛИ 9 проиадает. При сравнении кодов в следующей угловой координате вала иреобразователя в момент срабатывания одиовибратора 22 при условии несовпадения сравниваемых кодов вновь появляется сигнал на выходе схемы «ИЛИ Р, в результате чего срабатывает днфференцирующая схема 26, и работа устройства повторяется.

Заметим, что схема 25 должна иметь небольшую задержку с тем, чтобы исключить срабатывание схемы «И 5 при совпадении кода преобразователя с временно измененным кодом счетчика 15.

Как видно из фиг. 2, за счет изменения времени задержки схемы 23 представляется возможным изменять условия испытаний, предъявляя равные требованпя к правильности функционирования испытуемого преобразователя угол-код.

Предмет изобретения

Устройство для проверки функционирования преобразователей угол-код, содержащее привод равномерной скорости, с которым связан вал испытуемого преобразователя, выходы которого подключены ко входам первого дешифратора и первым входам первых схем «И, вторые входы которых через первые инверторы соединены с выходами разрядов реверсивного счетчика, а выходы через последовательно соединенные первую схему «ИЛИ и второй инвертор иадключены к первым входам вторых схем «И, выходы которых соединены с соответствующими входами блока регистрации, а вторые входы -

с выходами второго дешифратора, входы коToj)CTo соединены с выходами разрядов счетчика, а выходы подключены ко входам втоi)o:i и третьей схем «ИЛИ, выход которой

соединен со входом вычитания реверсивного счетчика, отличающееся тем, что, с целью повышеиия достоверности результатов проверки преобразователей угол-код, в устройство введены стабилизированный генератор

импульсов, триггеры, одновибратор, делитель частоты, схемы задержки, дифференцирующая схема и дополннтельные схемы «Pi и «ИЛИ, причем выход первого дешифратора через регулируемую схему задержки подключей ко входу первого триггера, выход ivOTOpoго подключен к перво.му входу ьервой дополнительной схемы «И, второй вход которой соединен с выходом стабилизированного генератора импульсов, а выход - со входом

делителя частоты, первый выход которого через последовательно соединенные первую схему задержкп и одновибратор подключен к третьим входам первых схем «И, через вторую схему задержки подключен к первому входу второй дополнительной схемы «И, второй вход которой соединен с выходом второго инвертора, а выход - с соответствующим входом блока регистрации, и к первому входу дополнительной схемы «ИЛИ, второй

ч..

вход которой подключен к выходу второй схемы «ИЛИ, а выход - ко входу сложения реверсивного счетчщ-са, второй выход делителя частоты соединен с первым входом третьей дополнительной схемы «И, выход

которой подключен ко входу счетчика, а второй вход - к выходу второго триггера, первый вход которого через дпфференцгфуюилю схему соединен с выходом первой схемы .«ИЛИ, а второй вход - с последним выходом второго дешифратора.

13

°4

27

Фиг. 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор частоты повторения работы инвертора и несущей частоты модуляции | 1977 |

|

SU692023A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЗАКОНА РАСПРЕДЕЛЕНИЯ ОШИБОК ПРЕОБРАЗОВАТЕЛЕЙУГОЛ-КОД | 1972 |

|

SU419938A1 |

| УСТРОЙСТВО для АВТОМАТИЧЕСКОЙ ПРОВЕРКИ ПРЕОБРАЗОВАТЕЛЕН УГОЛ — КОД | 1971 |

|

SU312285A1 |

| УСТРОЙСТВО ДЛЯ ПРОВЕРКИ ПРЕОБРАЗОВАТЕЛЕЙ УГОЛ-КОД | 1971 |

|

SU424205A1 |

| Устройство для контроля состояния информационно-измерительной системы | 1986 |

|

SU1314342A1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Устройство для контроля преобразователя угол-код | 1974 |

|

SU477445A1 |

| Электропривод стенда для испытания механических передач | 1985 |

|

SU1429267A1 |

| Аналого-цифровой преобразователь с промежуточным преобразованием в частоту | 1987 |

|

SU1441479A1 |

| ЭЛЕКТРОННОЕ КОДОВОЕ УСТРОЙСТВО | 2000 |

|

RU2179223C2 |

Даты

1974-06-15—Публикация

1972-07-20—Подача