Изобретение относится к области автоматики и вычислительной техники для проверки преобразователей угол - код.

Известны устройства для автоматической проверки преобразователей угол - код, содержащие приводной механизм, генератор стабильной частоты, блок дешифрации уровней квантования, блок формирования эталонных сигналов времени и блок регистрации результатов проверки. Недостатком известных устройств является невысокая надежность проверки.

С целью повышения надежности проверки преобразователей угол -г код в предложенном устройстве установлены блок контроля синхронизма, блок фор1у1ирования временных интервалов и блок контроля отсутствия сбоев, вход которого соединен с одним выходом блока формирования временных интервалов, другой выход которого подключен к входу блока регистрации результатов проверки, а один из входов соединен с выходом блока формирования эталонных сигналов времени, другой вход подключен к выходу блока дешифрации уровней квантования, второй выход которого соединен с входом блока контроля синхронизма. Другой вход этого блока подключен к выходу блока формирования эталонных сигналов времени.

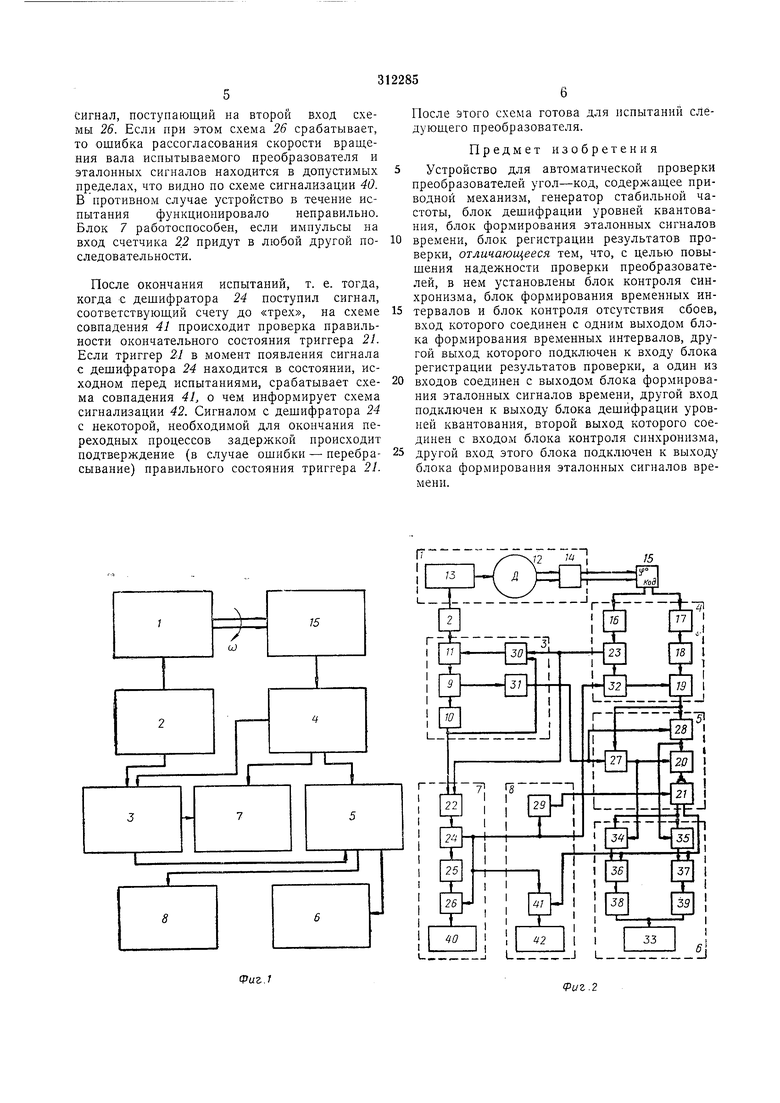

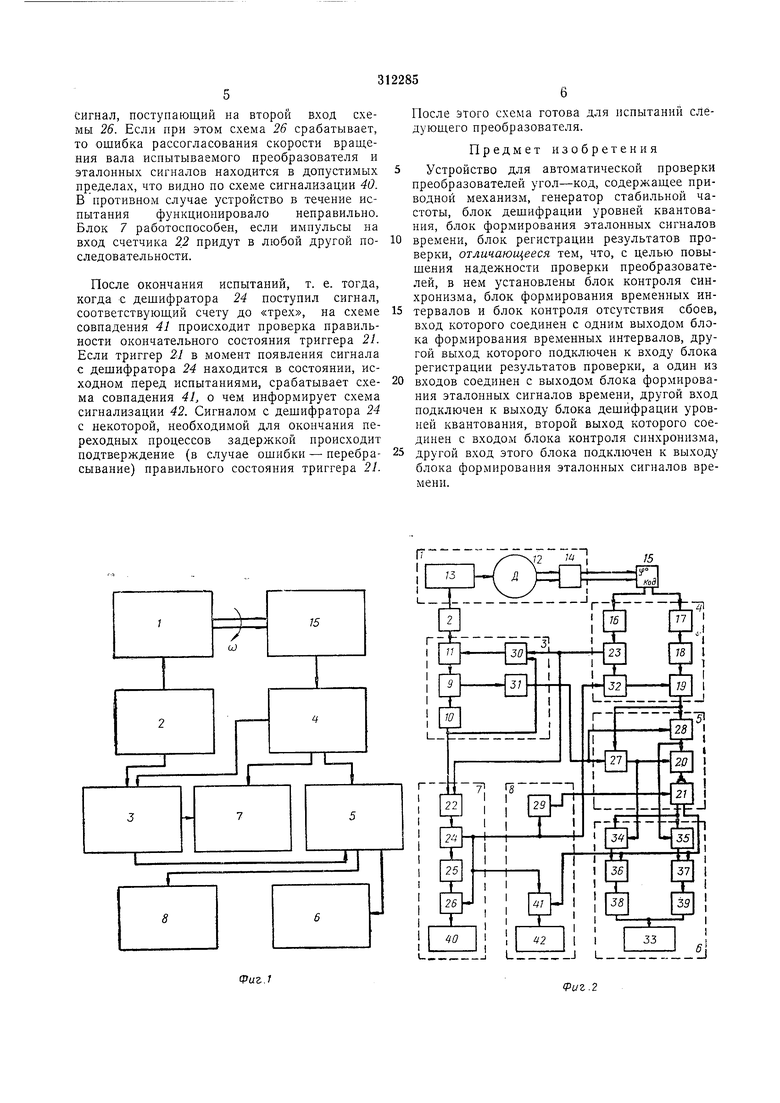

Устройство состоит из приводного механизма /, генератора стабильной частоты 2, блока 3 формирования эталонных сигналов времени, блока 4 дешифрации уровней квантования преобразователя, блока 5 формирования временных интервалов, соответствующих ошибке преобразователя; блока 6 регистрации результатов проверки, блока 7 контроля синхронизма угла поворота и эталонных сигналов времени; блока 8 контроля отсутствия сбоев в блоке 5.

Блок 3 включет в себя счетчики импульсов 9 и 10, соединенные последовательно через клапан //с генератором 2. Разрядность счетчиков 9 и W регулируется, например, посредством переключения тумблеров в зависимости от разрядности испытуемого преобразователя. Приводной механизм состоит из двигателя 12, источника 13 питания двигателя и понижающего редуктора 14, передаточное число которого выбрано таким, чтобы выходной вал редуктора совершил один оборот (несколько оборотов для многоотсчетного преобразователя) за время, необходимое для испытания

преобразователя 15.

Передаточное число редуктора, режим работы двигателя и пересчетная схема счетчика 9 выбраны такими, чтобы за время поворота вала преобразователя на один оборот (невано число импульсов, равное числу дискретов испытуемого преобразователя, например, для двоичной системы счисления 2, где п - число разрядов преобразователя. Блок 4 включает в себя дешифратор 16 нулевого положения первого кванта преобразователя, дающий разрешение на поступление в блок 5, во-первых, эталонных сигналов времени с блока 3, во-вторых, через логическую схему 17, дифференцируюшую цепь 18 и клапан 19 сигналов смены кода преобразователя. Блок 5 посредством логической схемы 20 и счетного триггера 21 осуществляет формирование временных интервалов, соответствующих ошибке воспроизведения квантованных уровней преобразователя. Блок 6 состоит из двух групп идентичных схем. Такое построение блока необходимо для распознавания знака ошибки квантования преобразователя. Блок 7 включает в себя счетчик 22, соединенный со счетчиком 10 и через дифференцирующую цепь 23 с дешифратором 16, дешифратор 24, схему задержки (одновибратор) 25 и логическую схему 26. Для контроля правильной работы блока 5 формирования временных интервалов, соответствуюших измеряемой ошибке преобразователя, в устройство введен блок 8 контроля отсутствия сбоев в блоке 5, сигнализируюший о правильном положении счетного триггера 21 по окончании испытаний. Б случае наличия сбоя на схемах 27, 28, 20, 21 вероятность возникновения которого весьма мала, импульс с дешифратора 24 через линию задержки 29 осуществляет в конце испытаний сброс триггера 21 в исходное положение, соответствующее началу испытаний. Устройство работает следующим образом. Бал преобразователя приводится во вращение с постоянной скоростью через редуктор 14 электродвигателем 12, необходимая стабилизация скорости вращения которого может достигаться различными путями. Б частности, для синхронного двигателя необходимо иметь высокую стабильность частоты питающего напряжения, что легко реализовать с помощью кварцеванного источника питания. С генератора стабильной частоты 2 через клапан 11, который открывается сигналом с триггера 30, в момент формирования преобразователем первого кванта начинают поступать импульсы на счетчик 9. Схема счетчика устроена так, что в зависимости от числа разрядов испытываемого преобразователя, тумблерами набирается такая комбинация, при которой с выхода счетчика 9 через дифференцирующую цепь 31, логическую схему 27 на схему 20 подаются импульсы со скважностью, соответствующей расчетным значениям времени смены кода преобразователя известной разрядности. который, во-первых, возвращает триггер 30 в начальное положение, и, во-вторых, фиксируется счетчиком 22. Число разрядов в счегчике 10 с помощью тумблеров выбирается равным числу разрядов преобразователя. Б тот момент, когда преобразователь при вращении вала займет положение, соответствующее первому кванту, сигнал с дешифратора 16 через дифференцирующую цепь 23 опрокидывает триггер 32, в результате чего огкрывается клапан 19, обеспечивающий прохождение сигналов с логической схемы П в схему 20, Таким образом, на схему 20 подаются импульсы, во-первых, от блока формирования эталонных сигналов времени, во-вторых, с испытуемого преобразователя в момент смены кода. Независимо от того, какой импульс пришел первым на схему 20, опрокидывается триггер 21 и находится в этом положении до тех пор, пока второй импульс не вернет его в исходное положение. Бремя между приходом эталонного и фактического импульсов и определяет ошибку воспроизведения квантованпых уровней преобразователя, которая отмечается регистрирующим прибором 33. Если эталонный и фактический сигналы совпадают по времени, схемы 27 и 28, не дадут пройти сигналам на схему 20 и триггер 21. Б противном случае произошло бы ложное опрокидывание триггера 21 до прихода следующей пары сигналов, так как схемой 20 и триггером 21 два совпавших по времени сигнала были бы приняты как один. Схемы совпадения 34 и 35 служат для того, чтобы определить какой знак должен иметь сигнал на регистрирующем приборе 33 в зависимости от того, какой на каждой паре сигналов, приходящих па входы схемы 20, пришел раньше - эталонный или фактический. Б течение времени, соответствующего ошибке воспроизведения очередного уровня преобразователя, триггер 21 находится в состоянии, противоположном исходному. Бследствие этого перебрасывается в противоположное исходное положение триггер 36 (или 37), и в течение этого времени работает интегрирующая цепь 38 (или 39), формируя сигнал на регистрирующем приборе, соответствующий измеряемой ошибке, Блок 7 работает следующим образом. Б начале измерений при вращении преобразователя первый сигнал с дешифратора 16 поступает на счетчик 22. Когда преобразователь в конце испытаний вновь займет то же положение с дешифратора 16 вновь поступает сигнал на счетчик 22. При заполнении счетчика 22 до «двух с дешифратора 24 снимается сигнал, который через схему задержки 25 в течение времени задержки воздействует на один из двух входов схемы 26. При формировании выходного сигнала па счетчик 10 счетчик 22 заполняег

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1984 |

|

SU1234841A1 |

| Устройство для контроля и диагностики цифровых блоков | 1983 |

|

SU1167610A1 |

| Устройство для контроля электрического монтажа | 1985 |

|

SU1345212A1 |

| Адаптивное устройство для обучения языкам | 1987 |

|

SU1441445A1 |

| Индикатор синхронизма | 1985 |

|

SU1429062A1 |

| Устройство для автоматического контроля кодовой шкалы преобразователя угол-код | 1972 |

|

SU447743A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| УСТРОЙСТВО ДЛЯ ПРОВЕРКИ*ФУНКЦИОНИРОВАНИЯ ПРЕОБРАЗОВАТЕЛЕЙ УГОЛ—КОД | 1972 |

|

SU432564A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЗАКОНА РАСПРЕДЕЛЕНИЯ ОШИБОК ПРЕОБРАЗОВАТЕЛЕЙУГОЛ-КОД | 1972 |

|

SU419938A1 |

| Многоканальное регистрирующее устройство | 1988 |

|

SU1698899A1 |

Даты

1971-01-01—Публикация