1

Изобретение относится к вычнслителышй технике и может быть использовано для построения временных разделенных коммутационных систем щгфровых интегрирующих струк-тур.

Известны коммутационные . яченкн универ-, сальной вычнслнтельной системы. Устройство содержит регистр и схему сравнения. Подсоединение каждого канала к электронной машнне производится последовательно. Причем в каждый момент времени может быть подклю- ю чено не более одного входного канала.

Однако известные ячейки имеют недостаточное быстродействие, так как время коммутации irpH последовательной передаче днскретной информацин большого числа каналов может быть значительным.

Целью изобретения является повышение быстродействия коммутационной ячейки.

Эта цель достигается тем.что в коммута- ционную ячейку введены триггер,линия задержки и группа изЬ1+1 ключей .объединенные 20 входы которых соединены со входом сигнала коммутации.а входы и ключей - с выходами образования двоичного кода адреса ячейки, причем выход первого ключа соединен через пинию задержки с нулевымвходом триг 25 ггера связанного едини.чнь1м входом с вдсформационным входом ячейки,единичным вы

ходом - с управляющими в.чодами m ключей н нулевым выходом - с управляющим входом {ш + 1)-го ключа, информационный выход которого соединен с выходом сигнала коммутации ячейки.

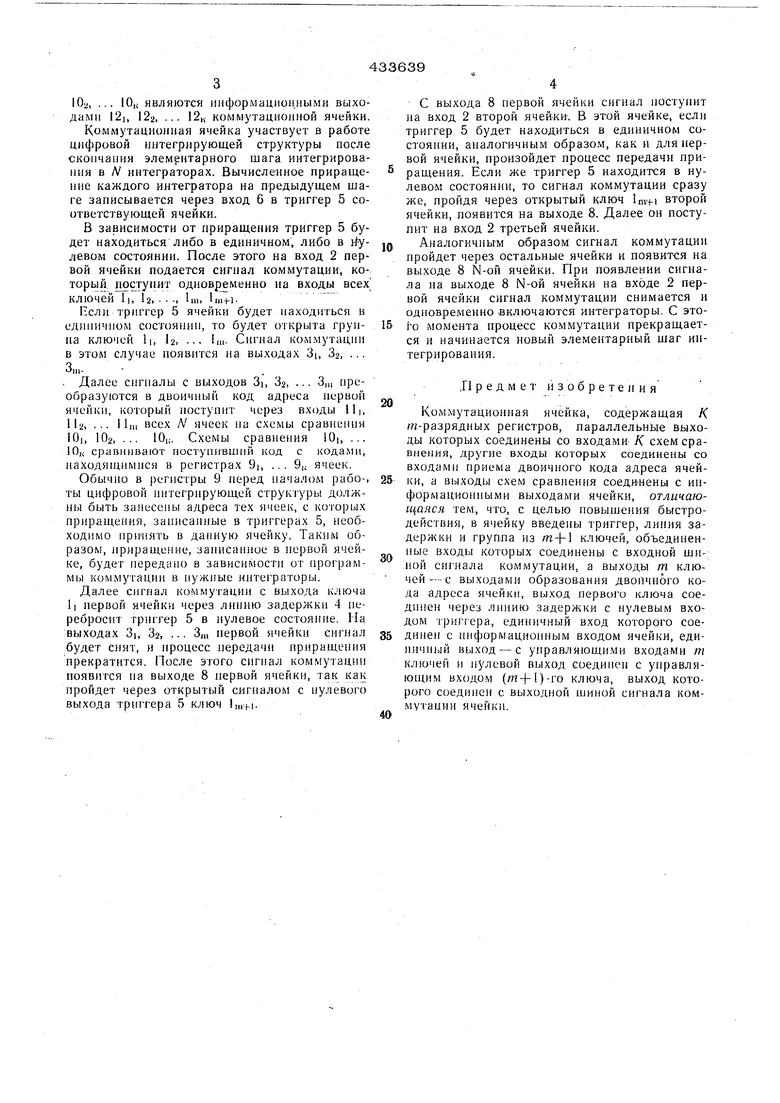

На чертеже приведена функциональная блок-схема ячейки.

Коммутационная ячейка содержит группу ключей li, 12, ... Im, Im-hi, объединенныб входы которых соединены со входом 2 сигнала коммутации, а выходы--с вы.ходами 3i, 82, ... 3,1, для образования двоичного кода.адреса ячейки. Выход первого ключа h соединен через линию задержки 4 с нулевым входом триггера 5. Триггер 5 связан единичным входом со входом 6 ячейки, единичным выходом - с управляющим входом 7i, Тг, ... 7,п ключей Ь, Ь, ... 1т и нулевым выходом-с управляющим входо.м 7,1,4-1 ключа Im+i- Выход ключа lia+i соединен с выходом 8 сигнала коммутации ячейки. Коммутационная ячейка содержит К т-разрядных регистров 9ь 92, . - , 9,;, в которых хранится программа коммутации в виде .адресов ячеек. Каждый регистр 9 связан параллельными выходами со схемой сравнения Ш, на которую поступают также входы llblb, ... lira для приема двоичного кода адреса ячейки. Выходы К схем сравнений lOi,

10:;, ... I0,i являются илформационными выходами 12, 122, ..- 2к коммутационной ячейки. Коммутационная ячейка участвует е работе цифровой интегрирующей структуры после скончания элементарного шага интегрирования в N интеграторах. Вычисленное приращение каждого интегратора на предыдущем щаге записывается через вход 6 в триггер 5 соответствующей ячейки.

В зависимости от приращения триггер 5 будет находиться либо в единичном, либо в riyлевом состоянии. После этого на вход 2 первой ячейки подается сигнал коммутации, который поступит одновременно на входы всех ключей 1ь Ь. .-., Uib 1ш-ц.

Если триггер 5 ячейки будет находиться в единичном состоянии, то будет открыта грунна ключей 1|, la, ... Im- Сигнал коммутации в этом случае появится на выходах 3i, За, ...

Зщ.

. Далее сигналы с выходов Зь 32, ... Зщ преобразуются в двоичный код адреса первой ячейки, который поступит через входы lli. Па, ... lljM всех Л ячеек на схемы сравнения Юь 102, ... lOj;. Схемы сравнения Юь ... 10,; сравнивают гюстушгвшмй код с кодами, находян-1им11ся в регистрах 9j, ... 9,; ячеек.

Обычно в регистры 9 перед началом рабо-, ты цифровой интегрирующей структуры должны быть занесены адреса тех ячеек, с которых приращения, записанные в триггерах 5, необходимо принять в данную ячейку. Таким образом, приращение, записанное в первой ячейке, будет передано в зависимости от программы ком.мутации в нужные интеграторы.

Далее сигнал коммутации с выхода ключа li первой ячейки через линию задержки 4 перебросит триггер 5 в нулевое состояние. На выходах 3), Зг, ... 3,,, первой ячейки сигнал будет снят, и процесс передачи приращения прекратится. После этого сигнал коммутации появится на выходе 8 первой ячейки, так как пройдет через открытый сигналом с нулевого выхода триггера 5 ключ ,,,f-i.

С выхода 8 первой ячейки сигнал поступит на вход 2 второй ячей.ки. В этой ячейке, если триггер 5 будет находиться в единичном состояпии, аналогичны.м образо.м, как и для первой ячейки, произойдет процесс передачи приращения. Если же триггер 5 находится в нулевом состоянии, то сигнал коммутации сразу же, пройдя через открытый ключ Inv-n второй ячейки, появится на выходе 8. Далее он поступит на вход 2 третьей ячейки.

Аналогичным образом сигнал коммутации пройдет через остальные ячейки и появится на выходе 8 N-ой ячейки. При появлении сигнала на выходе 8 N-ой ячейки на входе 2 первой ячейки сигнал коммутации снимается и одновре.менно включаются интеграторы. С этого момента процесс коммутации прекращается и начинается новый элементарный щаг интегрирования.

Предмет изобретения

Коммутационная ячейка, содержащая /С т-разрядных регистров, параллельные выходы которых соединены со входами К схем сравнения, другие входы которых соединены со входами приема двоичного кода адреса ячейки, а выходы схем сравнения соединены с информационными выходами ячейки, отличающаяся тем, что, с целью повышения быстродействия, в ячейку введены триггер, линия задержки и групла из ключей, объединенные входы которых соединены с входной щиной сигнала коммутации, а выходы т ключей- с выходами образования двоичного кода адреса ячейки, выход первого ключа соединен через линию задержки с нулевым входом триггера, единичный вход которого соединен с информационным входом ячейки, единичный выход - с управляющими входами т ключей и нулевой выход соедииен с уиравляющи.м входом (m-f 1)-го ключа, выход которого соединен с выходной шиной сигнала ком.мутации ячейки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Коммутационная ячейка | 1972 |

|

SU447839A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Коммутатор | 1977 |

|

SU738162A1 |

| УСТРОЙСТВО АДАПТИВНОЙ КОММУТАЦИИ СООБЩЕНИЙ | 2009 |

|

RU2416121C2 |

| Интегро-вычислительная структура | 1979 |

|

SU857987A1 |

| Устройство оперативной громкоговорящей связи | 1984 |

|

SU1170628A1 |

| Многоканальный резервированный коммутатор | 1989 |

|

SU1737723A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU900300A1 |

| ТРЕХКАСКАДНАЯ КОММУТАЦИОННАЯ СИСТЕМА | 2007 |

|

RU2359313C2 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

Авторы

Даты

1974-06-25—Публикация

1972-09-04—Подача