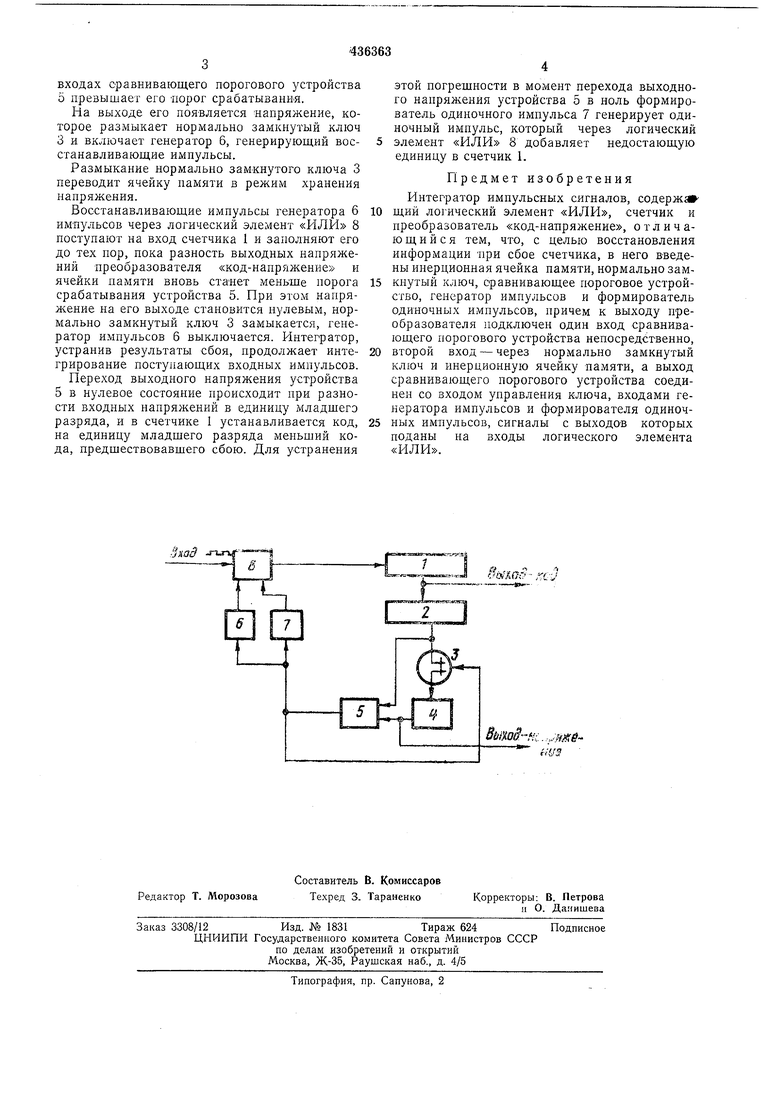

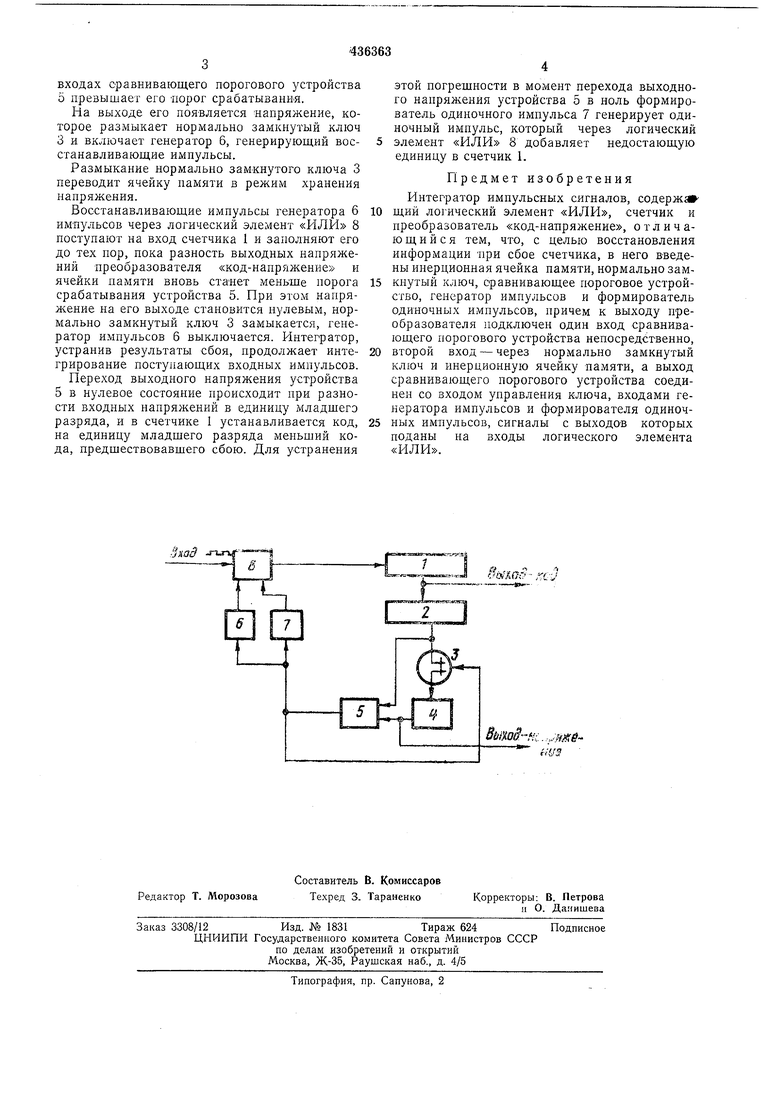

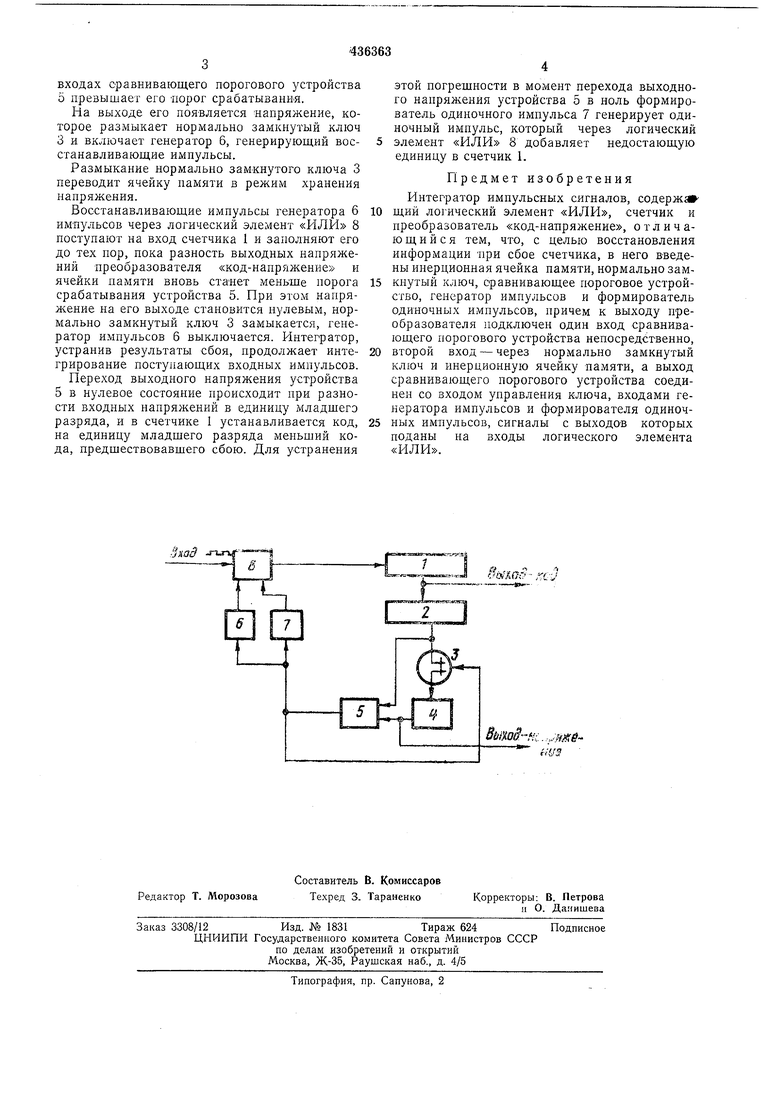

Изобретение относится к импульсной технике. Известен интегратор импульсных сигналов, содержащий логическую схему «ИЛИ, счетчик и преобразователь «код-напряжение.5 С целью восстановления информации при сбое счетчика в предлагаемый интегратор введены инерционная ячейка памяти, нормально замкнутый ключ, сравнивающее пороговое устройство, генератор импульсов и формирова- 10 тель одиночных импульсов, причем к выходу преобразователя подключен один вход сравнивающего порогового устройства непосредственно, второй вход - через нормально замкнутый ключ и инерционную ячейку памяти, а 15 выход сравнивающего порогового устройства соединен со входом управления ключа, входами генератора импульсов и формирователя одиночных импульсов, сигналы с выходов которых поданы па вход логического элемента 20 «ИЛИ. На чертеже дана блок-схема предлагаемого интегратора. Предлагаемый интегратор содержит счетчик 1, -преобразователь 2 «код-напряжение, нор- 25 мально замкнутый ключ 3, инерционную ячейку памяти 4, сравнивающее пороговое устройство 5, генератор 6 импульсов, формирователь 7 одиночного импульса, логический элемент «ИЛИ 8.30 Интегратор работает следующим образом. Импульсы, подлежащие интегрированию, через логический элемент «ИЛИ поступают на вход счетчика 1, в нем они накапливаются в виде кода. Код преобразуется в преобразователе 2 в сигнал постоянного тока, который при замкнутом ключе 3 прикладывается ко входу инерционной ячейки 4 и запоминается ею при размыкании нормально замкнутого ключа 3. Папряжения с выходов преобразователя 2 и ячейки 4 прикладываются ко входам сравнивающего порогового устройства 5. Если разность напряжений не превышает по абсолютной величине порога срабатывания, то напря жение -на выходе сравнивающего порогового устройства 5 нулевое. Величина порога соответствует значению, большему единицы и меньшему двух единиц младшего разряда счетчика 1. Инерционность ячейки памяти такова, что при поступлении на вход счетчика 1 интегрируемых импульсов максимально возможной частоты напряжения на ее входе и выходе отличаются меньше, чем на величину порога срабатывания сравнивающего порогового устройства 5. При сбое в любом из разрядов счетчика, кроме первого, что может произойти изза появления помехи или кратковременного перерыва питания, разность напряжений на

входах сравнивающего порогового устройства 5 превышает его тюрог срабатывания.

На выходе его появляется напряжение, которое размыкает нормально замкнутый ключ 3 и включает генератор 6, генерирующий воестанавливающие импульсы.

Размыкание нормально замкнутого ключа 3 переводит ячейку памяти в режим хранения напряжения.

Восстанавливающие импульсы генератора 6 импульсов через логический элемент «ИЛИ 8 поступают на вход счетчика 1 и заполняют его до тех пор, пока разность выходных напряжений преобразователя «код-напряжение и ячейки памяти вновь станет меньше порога срабатывания устройства 5. При этом напрял ение па его выходе становится нулевым, нормально замкнутый ключ 3 замыкается, генератор импульсов 6 выключается. Интегратор, устранив результаты сбоя, продолжает интегрирование поступающих входных импульсов.

Переход выходного напряжения устройства 5 в нулевое состояние происходит при разности входных напряжений в единицу младшего разряда, и в счетчике 1 устанавливается код, на единицу младшего разряда меньший кода, предшествовавшего сбою. Для устранения

этой погрешности в момент перехода выходного напрял ;ения устройства 5 в ноль формирователь одиночного импульса 7 генерирует одиночный импульс, который через логический элемент «ИЛИ 8 добавляет недостающую единицу в счетчик 1.

Предмет изобретения

Интегратор импульсных сигналов, содержав щнй логический элемент «ИЛИ, счетчик и преобразователь «код-папряженне, отличающийся тем, что, с целью восстановления информации при сбое счетчика, в него введены инерционная ячейка памяти, нормально замкнутый ключ, сравнивающее пороговое устройство, генератор импульсов и формирователь одиночных импульсов, причем к выходу преобразователя подключен один вход сравнивающего порогового устройства непосредственно, второй вход - через нормально замкнутый ключ и инерционную ячейку памяти, а выход сравнивающего порогового устройства соединен со входом управления ключа, входами генератора импульсов и формирователя одиночных импульсов, сигналы с выходов которых поданы на входы логического элемента «ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегратор импульсов | 1978 |

|

SU750508A1 |

| АНАЛИЗАТОР ДЛЯ КОНТРОЛЯ ХАРАКТЕРИСТИК ДИНАМИЧЕСКИХ СИСТЕМ | 1971 |

|

SU300875A1 |

| Интегратор | 1982 |

|

SU1062726A1 |

| Устройство восстановления информации | 1978 |

|

SU792249A1 |

| Режекторный фильтр | 1986 |

|

SU1417180A2 |

| РЕГИСТРИРУЮЩИЙ ПРИБОР | 1973 |

|

SU369499A1 |

| Режекторный фильтр | 1987 |

|

SU1429293A2 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО КОНТРОЛЯ ГЕОМЕТРИЧЕСКИХ НЕРОВНОСТЕЙ КОЛЕСНЫХ ПАР ПОДВИЖНОГО СОСТАВА12 | 1973 |

|

SU384711A1 |

| ПРИБОР ДЛЯ ИЗМЕРЕНИЯ ПАРАМЕТРОВ ПАРАЗИТНЫХ ИМПУЛЬСНЫХ ВОЗМУЩЕНИЙ В СЕТЯХ ЭЛЕКТРОПИТАНИЯ С ПЕРЕМЕННЫМ НАПРЯЖЕНИЕМ | 2002 |

|

RU2239201C2 |

| Устройство для контроля знаний обучаемых | 1990 |

|

SU1758658A1 |

и сгУД - ,ГС у

Bsiimd-fK.,,.;metiilS

Даты

1974-07-15—Публикация

1972-10-06—Подача