1

Изобретение относится к автоматике и вычислительной технике.

Известны распределители импульсов, состоящие из п идентичных каналов, каждый из которых содержит интегрирующие счетчики импульсов с тактовым и установочным входами, и генератора тактовых импульсов. Часто известные распределители используются для управления такими инерционными объектами, например электродвигателями, шаговыми моторами, поточно-производственными линиями, в которых допустим кратковременный сбой в работе распределителя с последующим восстановлением его функционирования. Однако известные распределители не позволяют просто и экономично реализовать такую возможность. Распределители либо прекращают функционировать, либо начинают неправильно работать, например распределять импульсы одновременно по нескольким каналам.

Целью изобретения является обеспечение самовосстановления работоспособности распределителя при воздействии дестабилизирующих факторов.

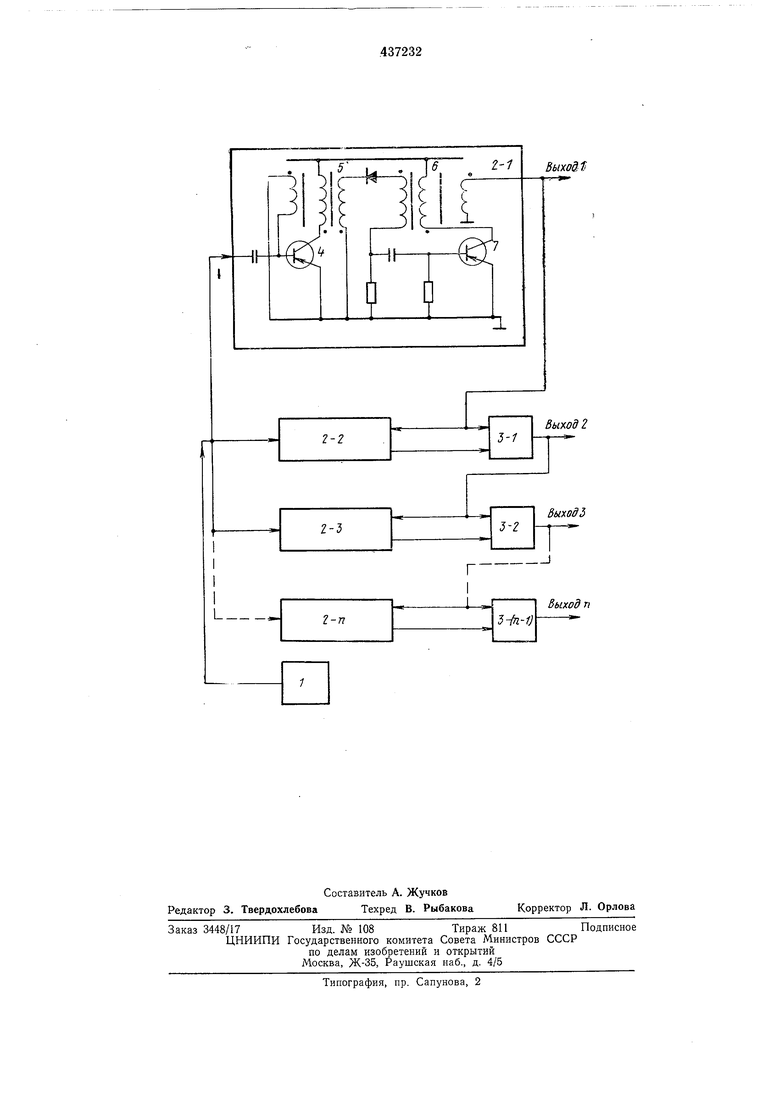

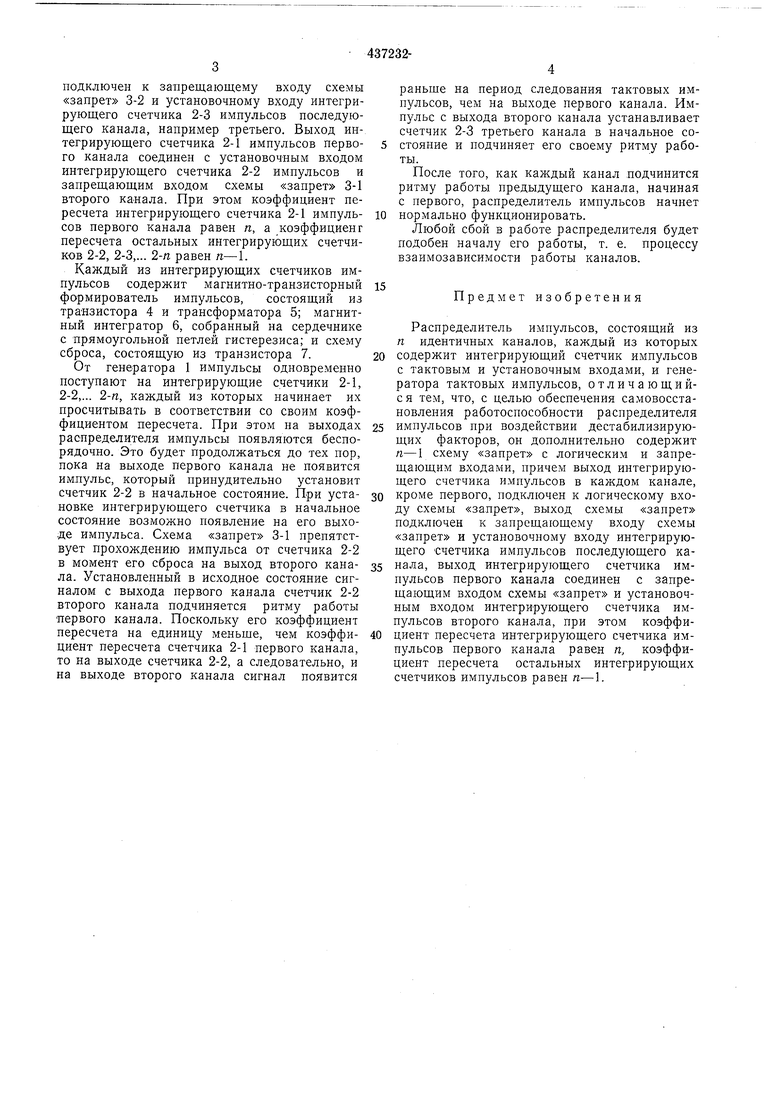

Для этого он дополнительно содержит п - 1 схему «запрет с логическим и запрещающим входами, причем выход интегрирующего счетчика импульсов в каждом канале, кроме первого, подключен к логическому входу схемы «запрет, выход схемы «запрет подключен к запрещающему входу схемы «запрет и установочному входу интегрирующего счетчика импульсов последующего канала, выход интегрирующего счетчика импульсов первого канала соединен с запрещающим входом схемы «запрет и установочным входом интегрирующего счетчика импульсов второго канала. При этом коэффициент пересчета интегрирующего счетчика импульсов первого канала равен п, коэффициент пересчета остальных интегрирующих счетчиков импульсов равен п-1. На чертеже изображена схема предлагаемого распределителя импульсов.

Распределитель содержит генератор 1 тактовых импульсов и п идентичных каналов, каждый из которых содержит один из интегрирующих счетчиков 2-1, 2-2, 2-3,... 2-п импульсов с тактовым и установочным входами и схему «запрет 3-1, 3-2,... 3-(п-1) (кром первого канала) с логическим и запрещаю щими входами. Генератор 1 тактовых импульсов подключен к тактовым входам интегрирующих счетчиков 2-1, 2-2, 2-3,... 2-п импульсов.

В каждом канале, кроме первого, например во втором, выход интегрирующего счетчика 2-2 импульсов подключены к логическому

входу схемы «запрет 3-1, выход которой

подключен к запрещающему входу схемы «запрет 3-2 и установочному входу интегрирующего счетчика 2-3 импульсов последующего канала, например третьего. Выход интегрирующего счетчика 2-1 импульсов первого канала соединен с установочным входом интегрирующего счетчика 2-2 импульсов и запрещающим входом схемы «запрет 3-1 второго канала. При этом коэффициент пересчета интегрирующего счетчика 2-1 импульсов первого канала равен п, а коэффициент пересчета остальных интегрирующих счетчиков 2-2, 2-3,... 2-п равен я-1.

Каждый из интегрирующих счетчиков импульсов содержит магнитно-транзисторный формирователь импульсов, состоящий из транзистора 4 и трансформатора 5; магнитный интегратор 6, собранный на сердечнике с прямоугольной петлей гистерезиса; и схему сброса, состоящую из транзистора 7.

От генератора 1 импульсы одновременно поступают на интегрирующие счетчики 2-1, 2-2,... 2-п, каждый из которых начинает их просчитывать в соответствии со своим коэффициентом пересчета. При этом на выходах распределителя импульсы появляются беспорядочно. Это будет продолжаться до тех пор, пока на выходе первого канала не появится имлульс, который принудительно установит счетчик 2-2 в начальное состояние. При установке интегрирующего счетчика в начальное состояние возможно появление на его выходе импульса. Схема «запрет 3-1 препятствует прохождению импульса от счетчика 2-2 в момент его сброса на выход второго канала. Установленный в исходное состояние сигналом с выхода первого канала счетчик 2-2 второго канала подчиняется ритму работы Первого канала. Поскольку его коэффициент пересчета на единицу меньше, чем коэффициент пересчета счетчика 2-1 первого канала, то на выходе счетчика 2-2, а следовательно, и на выходе второго канала сигнал появится

раньще на период следования тактовых импульсов, чем на выходе первого канала. Импульс с выхода второго канала устанавливает счетчик 2-3 третьего канала в начальное состояние и подчиняет его своему ритму работы.

После того, как каждый канал подчинится ритму работы предыдущего канала, начиная с первого, распределитель импульсов начнет нормально функционировать.

Любой сбой в работе распределителя будет подобен началу его работы, т. е. процессу взаимозависимости работы каналов.

Предмет изобретения

Распределитель импульсов, состоящий из п идентичных каналов, каждый из которых

содержит интегрирующий счетчик импульсов с тактовым и установочным входами, и генератора тактовых импульсов, отличающийс я тем, что, с целью обеспечения са.мовосстановления работоспособности распределителя

импульсов при воздействии дестабилизирующих факторов, он дополнительно содержит п-1 схему «запрет с логическим и запрещающим входами, причем выход интегрирующего счетчика импульсов в каждом канале,

кроме первого, подключен к логическому входу схемы «запрет, выход схемы «запрет подключен к запрещающему входу схемы «запрет и установочному входу интегрирующего счетчика импульсов последующего канала, выход интегрирующего счетчика импульсов первого канала соединен с запрещающим входом схемы «запрет и установочным входом интегрирующего счетчика импульсов второго канала, при этом коэффициент пересчета интегрирующего счетчика импульсов первого канала равен п, коэффициент пересчета остальных интегрирующих счетчиков импульсов равен п-1.

(-N-:

1-1

Выход, f в

Г

i

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Коммутирующее устройство | 1986 |

|

SU1510075A1 |

| Устройство синхронизации М-последовательности по задержке | 1986 |

|

SU1398106A1 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587641A1 |

| Многоканальный генератор импульсов | 1977 |

|

SU670067A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ДОСТОВ^ЕЦ.ОСТИ ПЕРЕДАЧИ ДВОИЧНОЙ ИНФОРМАЦИИ | 1970 |

|

SU274152A1 |

| Цифровое устройство для управления машиной непрерывного литья заготовок | 1989 |

|

SU1632621A1 |

| Устройство для измерения средней мощности сигналов в каналах и трактах систем связи | 1983 |

|

SU1095083A1 |

| Устройство для контроля и диагностики цифровых блоков | 1983 |

|

SU1167610A1 |

| Устройство для счета изделий | 1983 |

|

SU1152007A1 |

| Цифровой преобразователь координат | 1977 |

|

SU742944A1 |

2-2

г-ъ

.

Вымд 2

ВыходЗ

Выход Ti

Авторы

Даты

1974-07-25—Публикация

1972-01-03—Подача