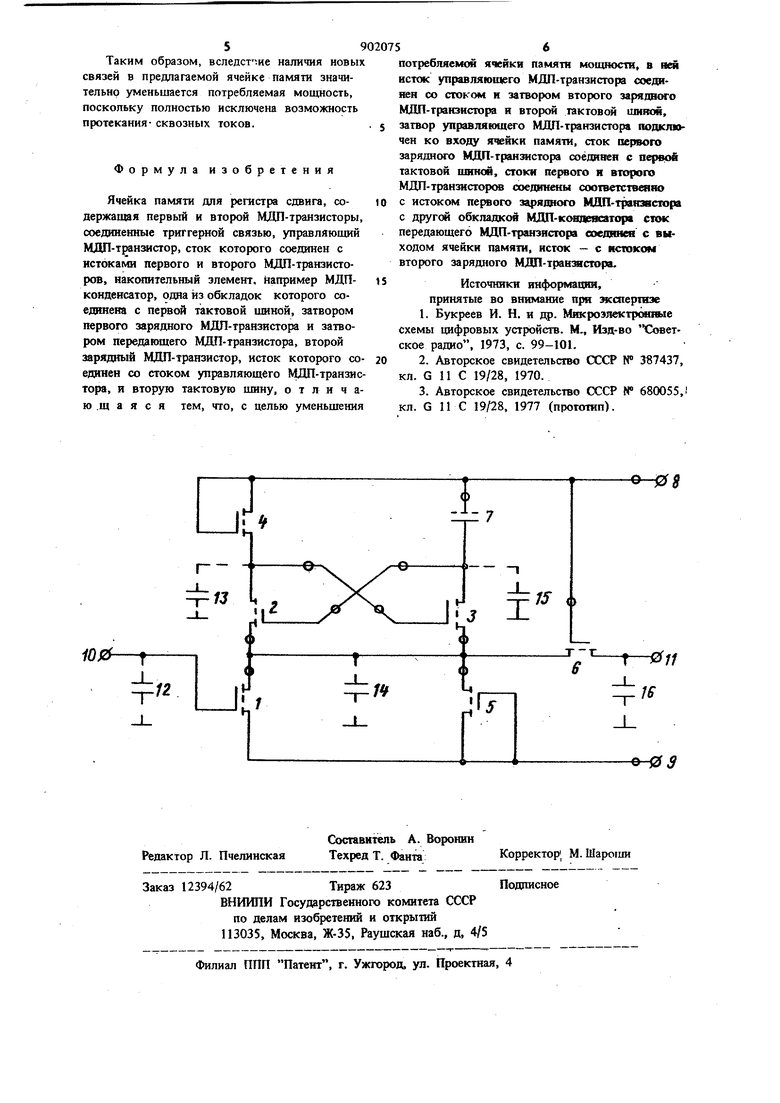

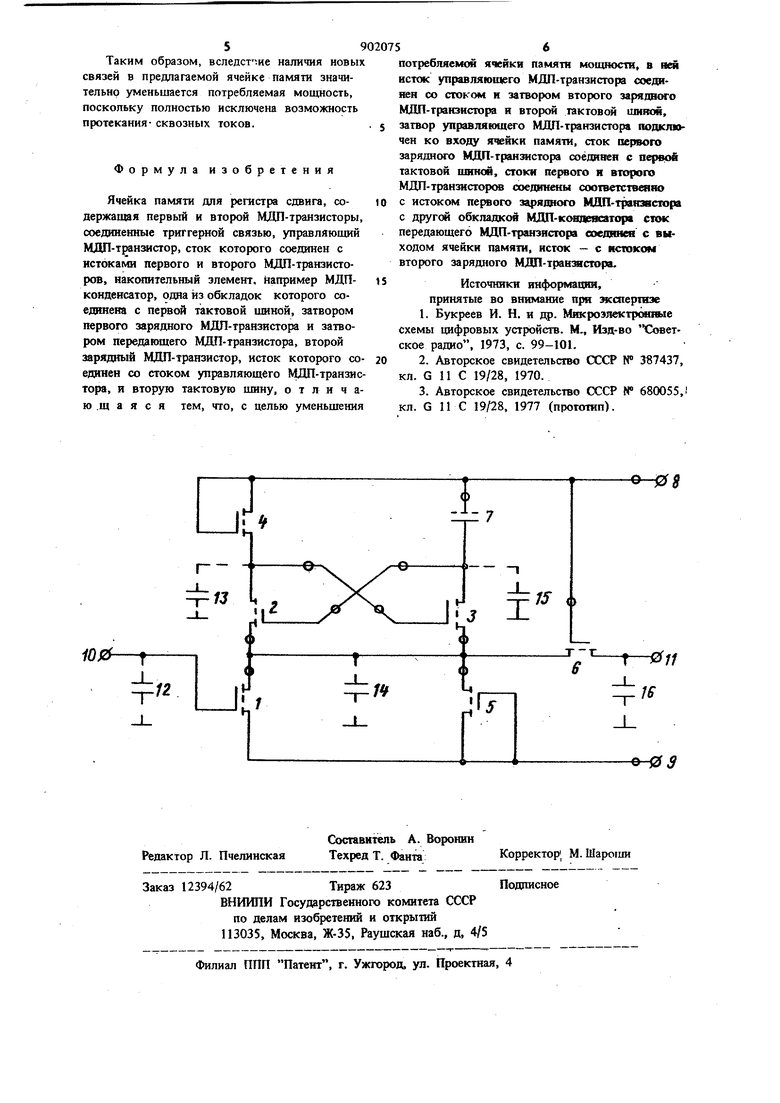

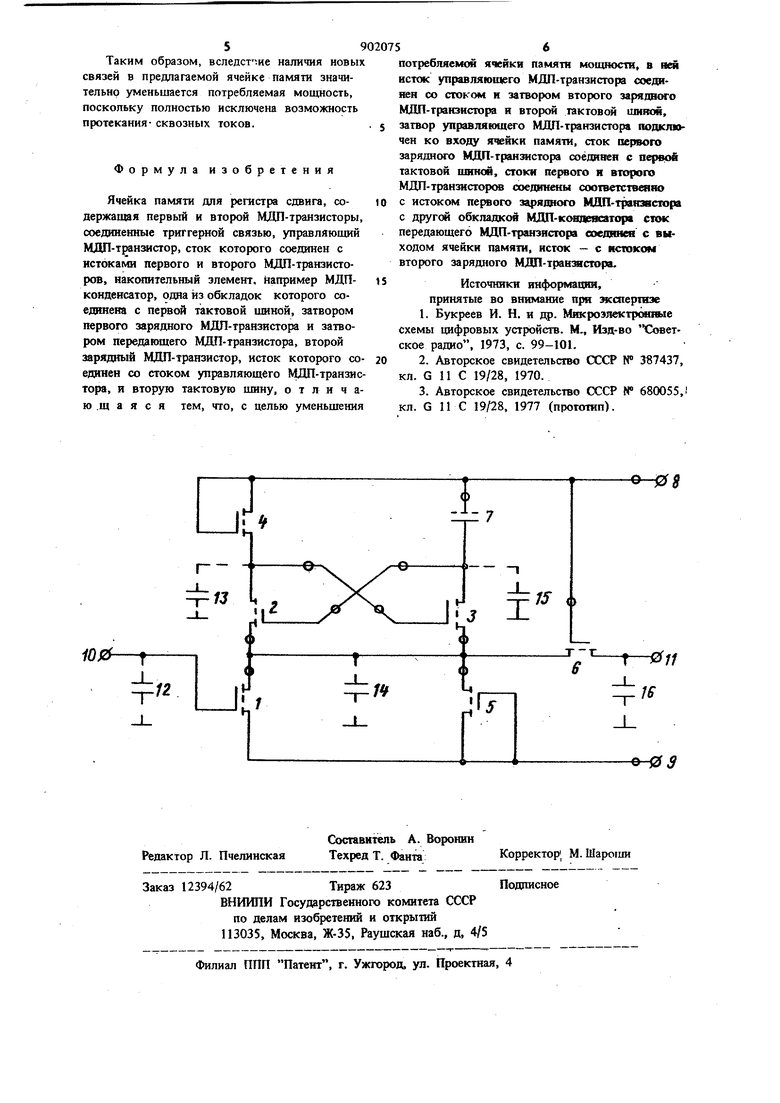

390 йена с первой тактовой ишиой, затвором первого зарядного МДП-транзистора и затвором передающегоМДП-транзистора, второй зарядный МДП-транзистор, исток которого соединен со стоком управляющего МДП-транзистора, и вторую тактовую шину, исток управляющего МДП-транзистора соединен со стоком и затвором второго зарядного МДП-траизистора и второй тактовой шиной, затвор управляющего МДП-транзистора подключен ко входу ячейки памяти, сток первого зарядного МДПтранзистора евоединен с первой тактовой ишной, стоки первого и второго МДП-транзисто-. ров соединены соответственно с истоком первого зарядного МДП-трайзИстора и другой обкладкой МДП-кс«денсатора, сток передающего МДШ-транзистора соединен с выходом ячейки памяти, исток - с истоком второго зарядного МДП-транзистора. На чертеже изображена электрическая схема предлагаемой ячейки памяти. Предлагаемая ячейка памяти содержит управляющий МДП-транзистор 1, первый 2 и второй 3 МДП-транзисторы, охваченные триггерной связью, первый 4 и второй 5 зарядны МДП-транзисторы, передающий МдаТ-транзистор 6, накопительный элемент, например МДП конденсатор 7, тактовые шины 8 и 9, вход 10 и выход 11 устройства и узловые емкости 12-16, образованные сое;аянительными элементами и линой нулевого потенциала (подJ у ложкой). Ячейка памяти функционирует следующим образом. Принцип работы ячейки памяти удобно рассматривать на примере сдвига сигнала, состоящего из напряжений логического нуля и логической единицы. Эта ячейка памяти инвер тирует информацию, т.е., если на вход подано напряжение логической еди1тцы, то на выходе - напряжение логического нуля. Пусть на входе 10 ячейки памяти - логический нуль. Узловая емкость 12 разряжена, транзистор 1 закрыт. В предыдущем такте от истопника тактового сигнала, действующего на шине 8, через транзистор 4 заряжается узловая емкость 13 до напряжения логической единицы. Транзистор 3 открыт. Во время действия тактового сигнала на шине 9 транзистор 5 открывается и происходит заряд узловых емкостей 14 и 15 до напряжения логической едиь-ицы. Значение емкости МДП-конденсатора 7 при этом становится максимальным, так как под его затвором индуцируется канал, служащий второй обкладкой МЛП-конденсатора. Во время действия тактового сигна ла на тине 8 через МДП-конденсатор 7 на затвор транзистора 2 передается, дополнительное напряжекие. Транзисторы 4, 2 и 6 открыты и на выход 11 ячейки памяти передается напряжение логической единицы, которое запоминается на узловой емкости 16. Однако емкости помнят информацию в течение малого промежутка времени (обычно 100-300 мкс). Из-за наличия токов утечки емкости узлов 12-16 разряжаются. Величина напряжения логической единицы уменьшается. Поэтому для того, чтобы информация не разрушалась, т.е. чтобы узловые емкости 12-16 не разряжались до напряжения ниже минимального значения логаческой едишщы, необходиморегулярно подзаряжать узловые емкости 12-16 до первоначального значения напряжения логической едишпщ. С этой целью подаются тактовые сигналы на шине 8 (спериодом повторения меньше 100 мкс). При этом с помощью МДПконденсатор 7 на затвор транзистора 2 передается дополнительное напряжение, откры; вающее этот транзистор. Транзистор 5 также открыт. В результате, происходит дозаряд узловых емкостей 14 и 16 до первоначального значения напряжения логической единицы. После окончания действия тактового сигнала на цшпе 8 через транзистор 3 происходит- перераспределение зарядов между узловыми емкостями 14 и 15, в результате которого обе емкости заряжены до напряжения логической единицы. Так происходит хранение в ячейке памяти напряжения логической единицы. Теперь пусть на входе 10 ячейки памяти - логическая единица. Узловая емкость 12 заряжена до напряжения логической единицы, транзистор 1 открыт. После окончания действия тактового сигнала на шине 9 через транзистор 1 происходит разряд узловых емкостей 14 и 15 до напряжения логического нуля. Значение емкости МДП-конденсатора 7 при этом минимальное. Поэтому во время действия тактового сигнала на шине 8 на затвор транзистора 2 не передается дополнительное напряжение и он остается закрытым. Открывается транзистор 6 и происходит перераспределение зарядов между узловыми емкостями 14, 15 и 16. А так как суммарное значение узловых емкостей 14 и 15 значительно пре:вышает значение емкости 16, то напряжение на узловых емкостях 14 и 15 хоть и повышается, однако остается меньше максимального значения напряжения логического нуля. После окончания действия тактового сигнала на шине 8 транзистор 6 закрывается, а на узловых емкостях 14, 15 и 16 запоминается напряжение логического нуля. Токи утечки оказь1вают полезное действие на процесс хранения напряжения логического нуля на узловых емкостях, поэтому оно может сохраняться сколь угодно долго.

Таким образом, вследст.ие наличия новых связей в предлагаемой ячейке памяти значительно уменьшается потребляемая мощность, поскольку полностью исключена возможность протекания- сквозных токов.

Формула изобретения

Ячейка памяти для регистра сдвига, содержащая первый и второй МДП-транзисторы, соединенные триГгертой связью, управляющий МДШ-транзистор, сток которого соединен с истоками первого и второго МДП-транзисторов, накопительный элемент, например МДПкоиденсатор, одна из обкладок которого соединена с первой тактовой шиной, затвором первого зарядного МДП-транзистора и затвором передающего МДП-транзистора, второй зарядный МДП-транзистор, исток которого соеданен со стоком управляющего МДП-транзистора, и вторую тактовую шину, о т л и ч аю .щ а я с я тем, что, с целью уменьшения

потребляемой ячейки памяти мощности, в нея истсмс управляющего МДП-транзистора соединен со стоком н затвором второго зарядвого МДШ-транзистора и второй тактовой шиной,

затвор управляющего МДП-траншстора подключен ко входу ячейки памяти, сток первого зарядного МДП-транзистора соёдивея с первой тактовой иганой, стоки первого н второго МДП-транзисторе соединены соответственно

с истсжом первого зарядного МДП- т ранзвсгира с другой обкладкой МДП-конпешатор сток передающего МДП-транзистора ооедннея с выходом ячейки памяти, исток - с истоком второго зарядного МДП-т{анэтстора.

Источники информации,

принятые во внимание при экспертизе 1. Букреев И. Н. и др. Мшероэлектрошые схемы цифровых устройств. М., Изд-во Х оветское радио, 1973, с. 99-101. 2. Авторское свидетельство СССР № 387437, кл. G 11 С 19/28, 1970.

3. Авторское свидетельство СССР № 680055,1 кл. G 11 С 19/28, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти для регистра сдвига | 1977 |

|

SU680055A2 |

| Элемент памяти для регистра сдвига | 1978 |

|

SU706880A1 |

| Запоминающая ячейка для регистра сдвига | 1974 |

|

SU519763A1 |

| Ячейка памяти на МДП транзисторах | 1981 |

|

SU968854A1 |

| Регистр сдвига | 1975 |

|

SU550678A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Ячейка памяти (ее варианты) | 1982 |

|

SU1070604A1 |

| Ячейка памяти | 1976 |

|

SU681455A1 |

| Дешифратор на МДП-транзисторах | 1986 |

|

SU1325558A1 |

| Ячейка памяти для регистра сдвига | 1983 |

|

SU1125655A1 |

I,

Т

13

еfS

н

Z

J

i00-tЛ Г

ff

Авторы

Даты

1982-01-30—Публикация

1980-06-02—Подача