(54) УСИЛИТЕЛЬ СЧИТЬШАНЙЯ Изобретение относится к микроэлектронике и может быть использовано в микросхемах постоянной памяти на МДП-элементах. В постоянных з-апоминакицих устройствах ( ПЗУ) на МДП-транзисторах. считываюпщм элементом традиционно яв Лялся ключевой транзистор инвертора передающий сигнал на выходной каскад. Это решение определяло невысокое быстродействие ПЗУ, поскольку для формирования .сигнала. на выходе приходилось ожидать полного перезаряда емкости разрядной шины. С целью увеличения быстродействия ПЗУ в них в качестве считывающего элемента стали использовать дифферен циальные усилители (ДУ) , разработанные первоначально для схем дина-. мических однотранзисторных ОЗУ, которые принципиально требуют высокой Чувствительности считывающего устрой ства. При использовании ДУ в ПЗУ отпадает необходимость ожидать полного переключения разрядной шины. ПУ во.рпринимает начальное изменение потенциала столбца и формирует с высокой скоростью сигналы для выходного каскада. Известны несколько вариантов реализации дифференциальных усилителей р. Такие схемы, обеспечивая высокую скорость считывания и чувствительность до ЮО мВ, обладают, в то же Время, рядом недостатков: а)скемы ДУ относительно сложны и Да1шмает на кристалле заметную пло щадь; б)некоторые из них потребляют значительную мощность от источника питания за счет наличия сквозного тока;в)ДУ требуют сложной диаграмма тактовых импульсов ТИ , что приводит к затратам мощности в генераторе ТИ, а, кроме того, усложняет расчет

схемы и уменьшает ее помехозащищенность;

Т/ существенным недостатком схем

ДУ является и то, что это наиболее сложные узлы мнкросхемы и они предъявляют жесткне требования к качеству технологического процесса, особенно к разбросам параметров элементов, что снижает надежность схемы. ДУ чувствительны к помехам, возникающим в БИС при переключениях логических вентилей и требуют тщательной проработки конструкторских решений.

Наиболее близким к предложенному является усилитель с переносом заряда, Это считывающий элемент представляет собой ДУ, в котором для создания приемлемого разбаланса на входе использован транзистор с переносом заряда, играющий роль предварительного усилителя, что позволяет увеличить чувствительность схемы до 60 мВ 2 .

Усихштель облада ет перечисленными вьше недостаткамиf присущими схемам с ДУ, но при высокой чувствительност (60 мВ ) имеет сравнительно низкое быстродействие.

Цель изобретения - упрощение усилителя, увеличение его помехозащищенности и надежности.

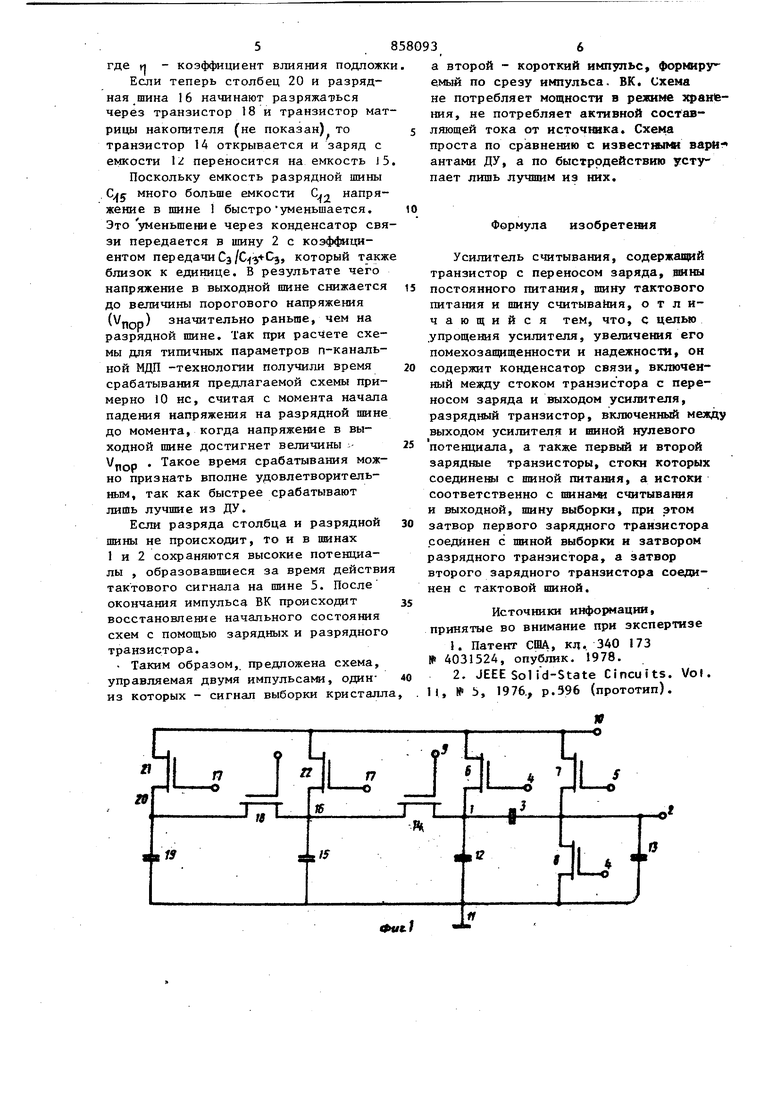

Поставленная цепь достигается тем что в усилитель считывания,содержащи транзистор с переносом заряда шины постоянного питания, щкну тактового питания и шину считывания, введены шина выборки, конденсатор связи, включенный между стоком транзистора с переносом заряда и выходом усилителя, разрядный транзистор, включенный между выходом усилителя и шиной нулевого потенциала, а также первый и второй зарядные транзисторы, стоки которых соединены с шиной питания. а истоки соответственно с шинами считывания и выходной, шину выборки, при этом затвор первого зарядного транзистора соединен с шиной выборки и затвором разрядного транзистора, а затвор второго зарядного тран зистора с тактовой шиной.

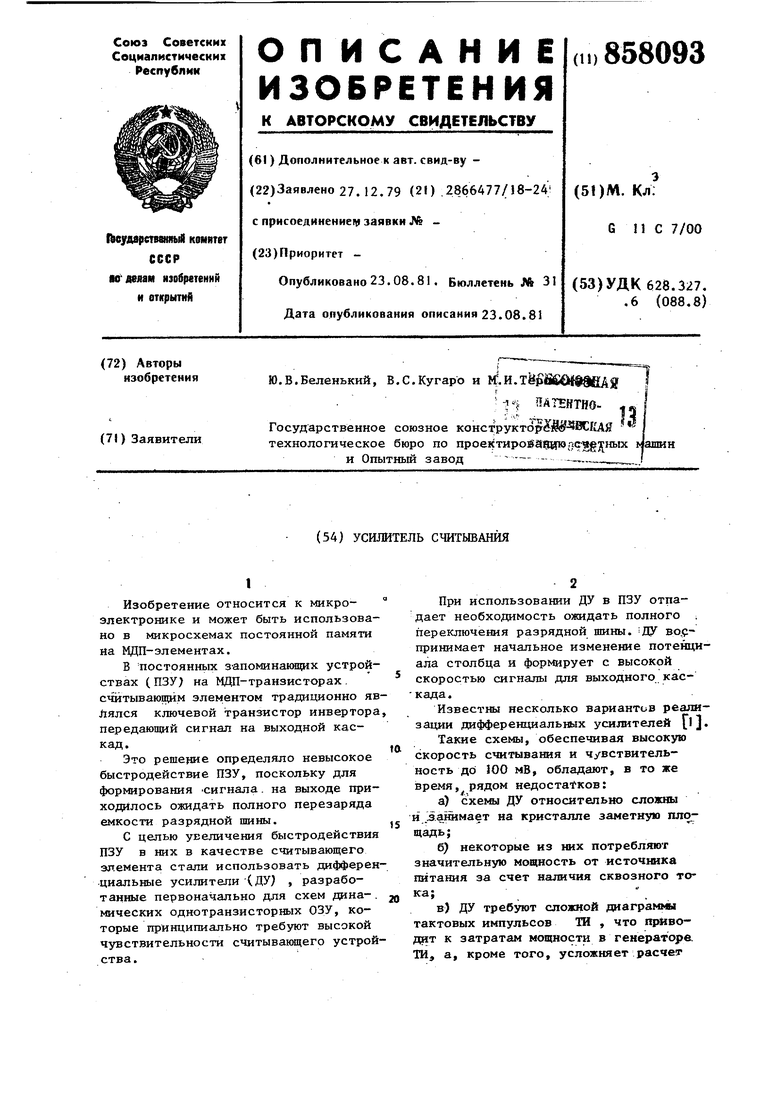

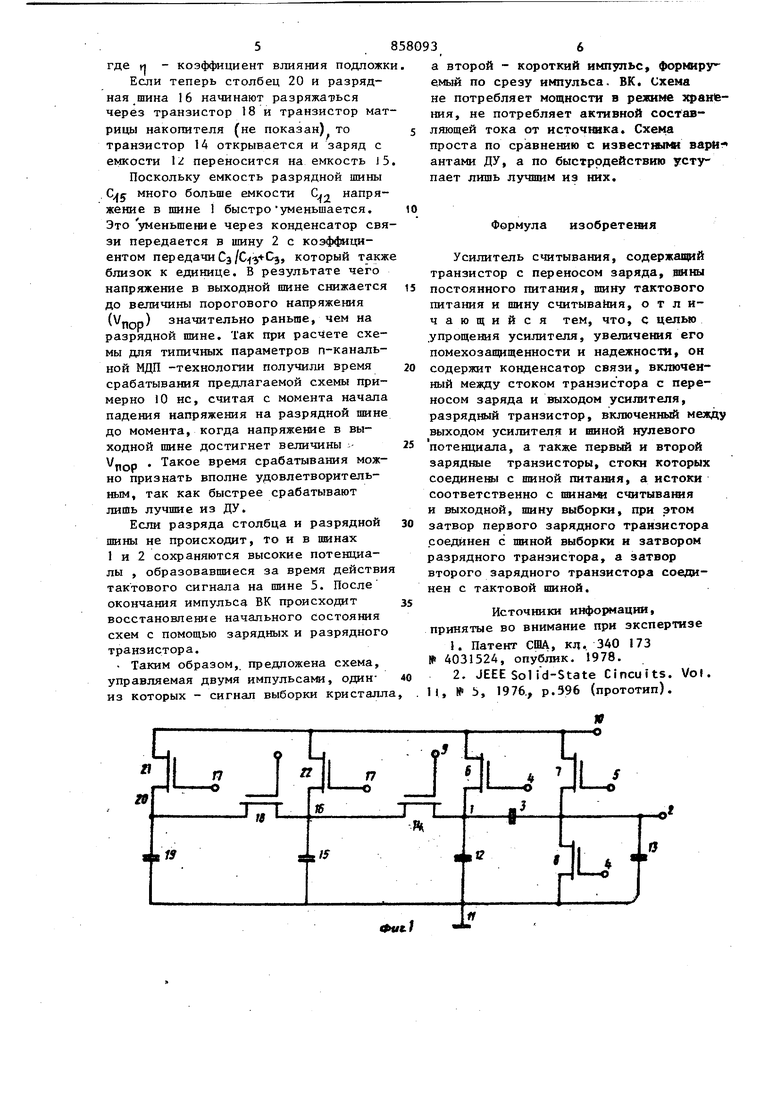

На фиг.1 представлена схема усилителя считывания; на (г.2 - временная диаграмма работы схемы,

Схема содержит шину 1 считывания, шину 2 выходную, конденсатор 3 связи шину 4 выборки, шину 5 тактовую, транзистор 6 зарядный, тактируемый сигналом выборки, транзистор 7 зарядный тактируемый сигналом 5, транзистор 8 разрядный, шину 9 опорного напряжения,, шину 10 питания, шину 1I нулевого потенциала, конденсатор 12 считывания, конденсатор 13 выходной, транзистор 14 переноса заряда.

Усилитель работает следующим образом.

В течение периода восст новления (отсутствие сигнала в выборки емкости 15 и 19 и шин матрицы накопители заряжаются через транзисторы 22 и 21 до напряжения V. ttOP 3 В. В это же время шина 1 заряжаs ется через транзистор 6 до напряжения Мл - VpiQp 6В, а выходная шина 2 приобретает потенциал общей шины 15 через открытый транзистор.8. С появлением сигнала РК (низкое

0 напряжение на шинах 4 и 17 на шине 5 формируется короткий (длительность 10-15 не) импульс с амплитудой 9В, который заряжает емкость I3 выходной шины до бВ. Конденсатор 3 связи передает часть потенциала в шину 1

в соответствии с коэффициентом передал чи, определяемым отношением А- Ми1шмизируя и выбирая величину С можно получить коэффициент переQ дачи близкий к единице.

После появления сигнала ВК начинают срабатывать адресные регистры и дешифраторы ПЗУ. Время срабатывания этих цепей больше длительности импульса на шине 5. Одновременно с ростом напряжения на шинах дешифраторов X И У начинается падение напряжения на столбце 20 и разрядной шине 16 (если в выбранной шине матрицы сформирован транзистор).

К этому моменту в шинах предлагаемой схемы имеются следующие напряжения: % УЗО- ЗВ; V 11 В; V - 6В; VQ-4,8 В (опорное напряжение) .

Приближенньш значения напряжений объясняются тем, что они получень) расчетом на ЭВМ, при котором используется математическая модель транзистора. Погрешность модели в описании характеристик транзистора может достигать 20%.

Таким образом, транзистор 14 находится в режиме отсечки,поскольку напряжение между его затвором и истоком с учетом влияния подложки меньше порогового напряжения (v пор )

(1 + 1 ) V

- V

пор

15 где ц - коэффициент влияния подложк Если теперь столбец 20 и разрядная шина 16 начинают разряжаться через транзистор 18 и транзистор мат рицы накопителя (не показан) то транзистор 14 открывается и заряд с емкости 2 переносится на емкость i5 Поскольку емкость разрядной шины . много больше емкости Ci напряжение в шине I быстроуменьшается. Это уменьшение через конденсатор свя зи передается в шину 2 с коэффициентом передачи Сз/С -«-Сз, который такж близок к единице. В результате чего напряжение в выходной шине снижается до вeJШЧины порогового напряжения () значительно раньше, чем на разрядной шине. Так при расчете схемы для типичных параметров п-канапьной МДП -технологии получили время срабатывания предлагаемой схемы примерно 10 НС, считая с момента начала падения напряжения на разрядной шине до момента, когда напряжение в выходной шине достигнет величины Такое время срабатывания можно признать вполне удовлетворительным, так как быстрее срабатывают лишь лучшие из ДУ. Если разряда столбца и разрядной шины не происходит, то и в шинах 1 и 2 сохраняются высокие потенциалы , образовавшиеся за время действи тактового сигнала на шине 5. После окончания импульса ВК происходит восстановление начального состояния схем с помощью зарядных и разрядного транзистора. Таким образом,, предложена схема, управляемая двумя импульсами, один ИЗ которых - сигнал выборки кристалл bu J J

№

w

19

If

-О

«

bf а второй - короткий импульс, формируемый по срезу импульса. ВК. Схема не потребляет мощности в режиме зфанЬния, не потребляет активной составляющей тока от источника. Схема проста по сравнению с иэвестшлв вари- антами ДУ, а по быстродействию уступает лишь лучшим из них. Формула изобретения Усилитель считывания, содержавши транзистор с переносом заряда, рвсны постоянного питания, шину тактового питания и шину считывания, отличающийся тем, что, с целью .упрощения усилителя, увеличения его помехозащищенности и надежности, он содержит конденсатор связи, включенный между стоком транзистора с переносом заряда и выходом усилителя, разрядный транзистор, включенный между выходом усилителя и шиной нулевого потенциала, а также первый и второй зарядгше транзисторы, стоки которых соединеш. с шиной питания, а истоки соответственно с считывания и выходной, шину выборки, при этом затвор первого зарядного транзистора соединен с шиной выборки и затвором разрядного транзистора, а затвор второго зарядного транзистора соединен с тактовой шиной. Источники информации, принятые во внимание при экспертизе 1.Патент США, кл. 340 173 № 4031524, опублик. 1978. 2,JEEE Solid-state Cincuits. Vol. 1, № 5, 1976., p.396 (прототип). у «JuIlu

| название | год | авторы | номер документа |

|---|---|---|---|

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Выходной усилитель | 1981 |

|

SU1015436A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| НАКОПИТЕЛЬ ЭЛЕКТРИЧЕСКИ ПРОГРАММИРУЕМОГО ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1991 |

|

RU2028676C1 |

| Усилитель считывания на мдп-транзисторах | 1978 |

|

SU721852A1 |

| Устройство для считывания информации из блоков памяти | 1977 |

|

SU746718A1 |

| Запоминающее устройство с перезаписью информации | 1974 |

|

SU570920A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Способ хранения информации на МДП-транзисторе и запоминающий элемент для осуществления этого способа | 1977 |

|

SU943846A1 |

Фие.1

Фиг.2

Авторы

Даты

1981-08-23—Публикация

1979-12-27—Подача