1

ИзОбретемие относится к области вычислительной техники и может быть использовано в системах обработки данных, системах уиравления и аналого-цифровых комплексах.

Известно устройство обмена, содержащее схему сравиения, иодключениую к счетчикам формирования адресов, которые соединены с числовыми и адресными шинами устройства и блоком управления, связанным с переключателем каналов.

Недостаток известного устройства заключается в том, что оно не нозволяет вести параллельную работу вводных и выводных устройств через общую буферную зону.

Цель изобретения - обеспечение иараллельной работы вводных и выводных устpoiiCTB через общую буферную зоиу.

Поставленная цель достигается тем, что устройство содержит регистр объема буферной зоны, триггер и схемы совнадения. Выход схемы сравнения соединен с первыми входами схем совпадения, вторые входы которых соедишены с иервым и вторым выходами триггера, третий выход и нервьп вход которого подключены к чис.товым Шинам устройства. Выходы схем совнадения соединены с соответствующими входами блока управления, соответствующие выходы которого соединены с первым и вторым установочными, с иервым и вторым управляющими входами триггера, с

управляющим входом регистра объема буферной зоны, разрядные входы и первые разрядные выходы которого соединены с числовыми щинами устройства, а вторые разрядные выходы соедипеиы с соответствующими входами счетчиков формирования адресов.

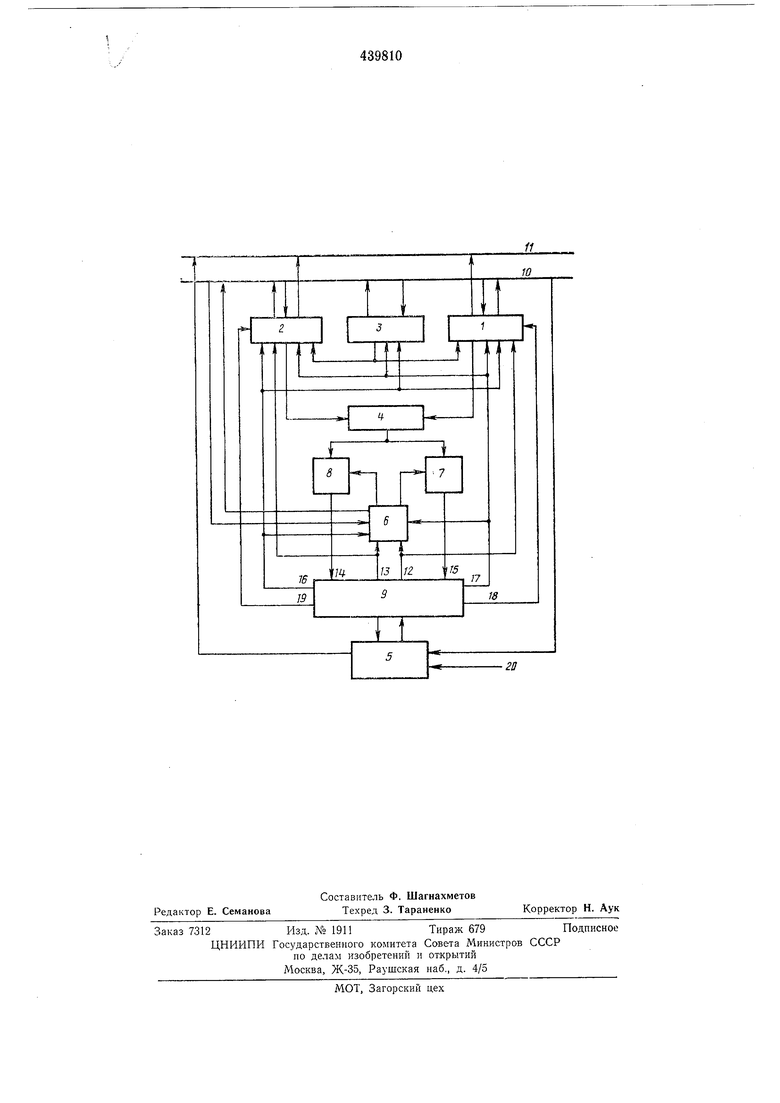

Блок-схема устройства представлена на чертеже.

Устройство обмена содерл ит счетчики 1 и

2формирования адресов, регистр 3 обьема буферной зоны 3, схему сравнения 4, переключатель каналов 5, триггер 6, схемы совпадения 7 и 8, блок управления 9, числовые щииы 10, адресиые щииы 11 и уиравлиющие шины 12-20.

Устройство обмена работает следующим образом.

Буферная зона с определенным номером закрепляется за парой обменивающихся устройств. Число ЗОИ определяется количеством таких пар. Адресные и числовые 1пины связывают устройство с обн;ей памятью системы, где хранятся также управл;ощие слова. Каждое управляюш,ее слово хранит содержимое счетчиков 1 и 2, регистра 3 и триггера 6. Содержимым счетчиков 1 и 2 являются базовые адреса буферных зон, содержимым регистра

3- - коды, задающие объемы бу{)ерных зон. Объем буферной зоны равен единиц информации, если единица записана в п-ом разряде рсгист)а 3. Содержимое триггера 6 фикоирует режим (запись или считывание) предыдущей операции обмена. Заявки от различных устройств поступают по шииам 20 в переключатель каиалов 5, который выделяет наиболее приоритетную заявку, обеспечивает прием от обслуживаемого устройства номер буферной зоны и направление обмена (запись в буферную зону или считывание из буферной зоиы) i по номеру зоны формирует адрес ячейки управляющего слова. По этому адресу блок управления 9 организует обращение к памяти и сигналом по шине 16 осуществляет прие.м управляющего слова в счетчики 1 и 2, регистр 3 и триггер 6. Если в данном цикле обслуживания должна быть осуществлена запись в буферяую зону, блок управления анализирует сигнал по ши«е 15. Запрещающий потенциал на щине 15 возникает, когда содержимое счетчиков равно, а триггер 6 находится в единичном состоянии. Такая ситуация возникает при перепол.нении буферной зовы, когда скорость записи в зону превышает- скорость считывания из нее. Тогда блок управления 9 запрещает запись в зону, а переключатель каналов 5 переходит к поиску других устройств, требующих обмена. Разрешающий нотенциал- на щине 15 возникает в том случае, когда содержимое счетчиков 1 и 2 не равно, что свидетельствует о том, что буферная зона заполнена не полностью. В этом случае блок управления вырабатывает импульс по щине 18, который добавляет едшшцу к содержимому счетчика I. Таким образом, в счетчике 1 формируется абсолютный адрес записи, который указывает очередную свободную ячейку для записи информации в данную буферную зоиу. Сигналом по шине 12 осуществляется выдача содержимого счетчика 1 на адресные щилы 11 и установка триггера 6 в единичное состояние. Одновременно переключатель каналов 5 обеспечивает выдачу данных устройства, участвующего в обмене, на числовые шины и занись информации в буферную зону но адресу, сфОр.мирован.ному в счетчике 1. После окончания онерации с памятью блок управления 9 выдает по шине 1 Усигнал, по которому модифицированное содержимое счетчиков 1 и 2, регистра 3 и триггера 6 возвращается в фиксированную ячейку памяти. Если в данном цикле должно быть осуществлено считывание из буферной зоны, блок управления 9 анализирует сигнал но нтине 14. Запрещающий нотенциал на шине 14 возникает в том случае, когда содержнмое счетчиков 1 и 2 равно, а триггер 6 находится в нулевом состоянии. Это означает, что буферная зона пуста. Прн этом блок управления 9 запрещает считывание из буферной зоны. Разрешающий нотенциал на шине 14 возникает в том случае, когда содержимое счетчиков 1 и 2 не равно, при этом блок управления 9 выдает но шине 19 импзльС; который добавляет единицу к содержимому счетчика 2. Сигналом по нгине 13 осуществляется выдача содержимого счетчиха 2 на адресные /.НИНЫ 11 и установка триггера 6 в нулевое состояние. Переключатель каналов 5 обеспечивает считывание данных из памяти в устройство, с которым в данный .момент осуществляется обмен. После око«чания операции с памятью сигналом по щине 17 содержимое счетчиков 1 и 2, регистра 3 и триггера 6 возвращается в фиксированную ячейку. Вышеописанная работа устройства обмена новторяется с приходом каждой заявки от устройства, требующего обмена. Формирование абсолютного адреса записи в буферную зону и считываНия из буферной зоны осуществляется путем присоединения кода относительного адреса к коду адреса в счетчиках 1 и 2. Формирова|Ние относительных адресов, задающнх расположепие текущей ячейки бу()ерной зоны для записи или считывания, осуществляется в тех младщих разрядах счетчиков 1 и 2, которые «ограничены единицей регистра 3. Эта часть счетчиков работает в кoльцeвo режиме. Остальные старшие разряды счетчиков 1 и 2 используются для хранения базового адреса, записанного перед началом обмена, и остаются постоянными на протяжении сеанса обмена. Физически сохранение базового адреса осуществляется блокированием переноса в разряд счетчиков, соответствующий тому разряду регистра 3, в котором записана единица. Предмет изобретения Устройство , содержащее схе.му сравнения, нодключенную к счетчикам формирования адресов, которые соединены с числовыми и адресными шинами устройства и блоком унравлеиа1я, связанным с переключателем каналов, отличающееся тем, что, с целью обеспечения параллельной работы вводных и выводных устройств через общую буферную зону, оно содержит регистр объема буферной зоны, триггер, схемы совпадения, причем выход схемы сравнения соединен с первыми входами схем совпадения, вторые входы которых соединены с первым и вторым выходами триггера, третий выход и первый вход которого подключены к числовым шинам устройства, выходы схем совпадения соединены с соответствующими входами блока управления, соответствующие выходы которого соединены с первы.м и вторым установочными, с нервы.м и вторым управляющи.ми входами триггера, с управляющаш входом регистра обтэема буферной зоны, р;)зрядные входы и первые разрядные выходы которого соединены с чнсловыми швнами устройства, а вторые разрядные выходы соединены с соответствующими входами счетчиков формирования адресов.

2и

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство обмена | 1973 |

|

SU473177A2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА ЦИЛИНДРИЧЕСКИХ МАГНИТНЫХ ПЛЕНКАХ | 1968 |

|

SU231224A1 |

| Буферное запоминающее устройство | 1978 |

|

SU750567A1 |

| Устройство обмена | 1974 |

|

SU503231A1 |

| Многофункциональное запоминающее устройство | 1972 |

|

SU458037A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Многокоординатный цифровой интерполятор | 1984 |

|

SU1200246A1 |

| Логический анализатор | 1988 |

|

SU1654822A1 |

| Устройство для управления оперативным накопителем | 1977 |

|

SU656106A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

Авторы

Даты

1974-08-15—Публикация

1971-07-12—Подача