I

Изобретение касается вычислительной техники, в частности устройств для контроля блоков цифровых вычислительных машин (ЦВМ).

Известны устройства для контроля ЦВМ, содерн ащие генератор импульсов, генератор тестов, сумматор, дешифратор неисправностей контролируемого блока, дешифратор неисправностей элементов, узел признака контролируемого блока, индикаторы неисправноС1ей.

Однако для этих устройств характерна недостаточная эффективность контроля, вызванная неопределенностью технического состояния устройств контроля в момент проведения блоков ЭВМ.

Целью изобретения является повышение эффективности контроля.

Это достигается тем, что устройство содержит схемы «И самоконтроля, схемы «И контроля, дешифратор самоконтроля, схему «ИЛИ, элемент задержки, индикатор самоконтроля и управляюш;ий триггер, единичный выход которого связан с первыми входами схем «И самоконтроля, вторые входы которых соединены соответственно с выходами генератора универсального теста, связанными также с первыми входами дешифратора самоконтроля, выходами дешифратора неисправностей блоков и дешифратора неисправностей элементов, нулевой выход управляюш,его

триггера подключен ко входу индикатора самоконтроля и к первым входам схем «И коптроля, вторые входы которых соединены с выходами контролируемого блока, выходы схем

«И контроля и схем «И самоконтроля подключены к соответствуюш,им входам сумматора, выходы которого связаны со вторыми входами дешифратора самоконтроля, выход которого соединен с первым входом схемы

«ИЛИ и нулевым входом управляющего триггера, единичный вход которого подключен ко второму входу схемы «ИЛИ, выход схемы «ИЛИ соединен с третьими входами генератора универсального теста и сумматора

непосредственно и со вторыми входами указанных блоков - через элемент задержки.

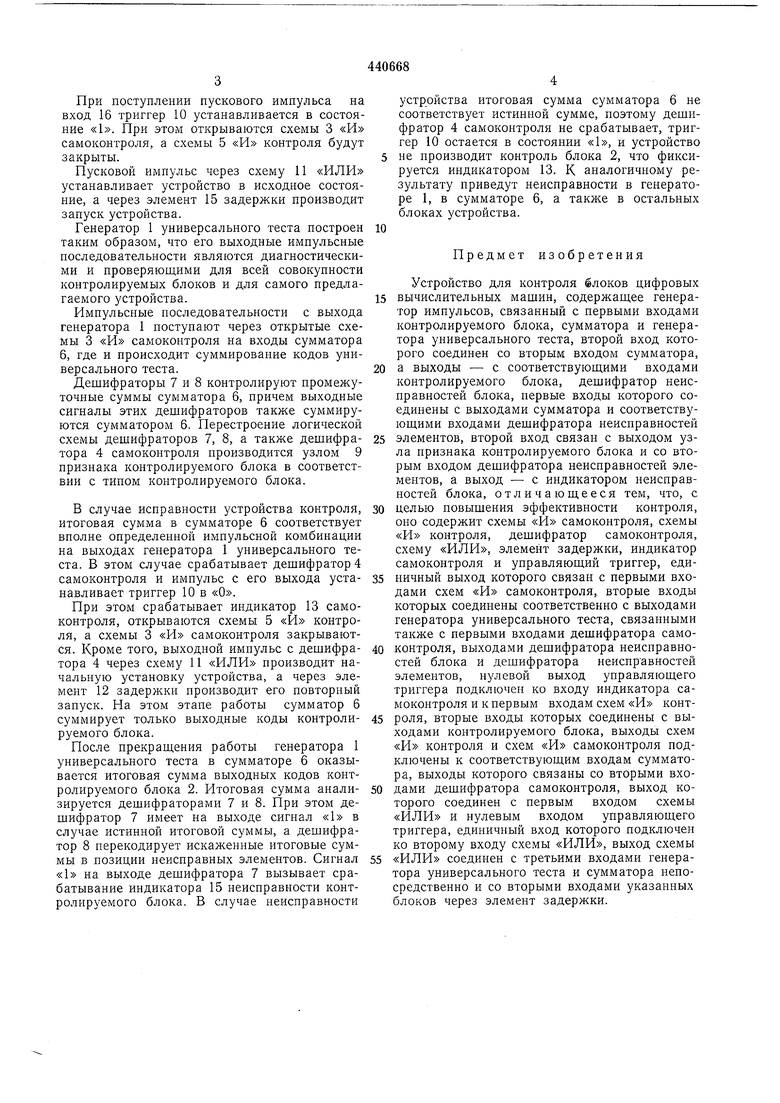

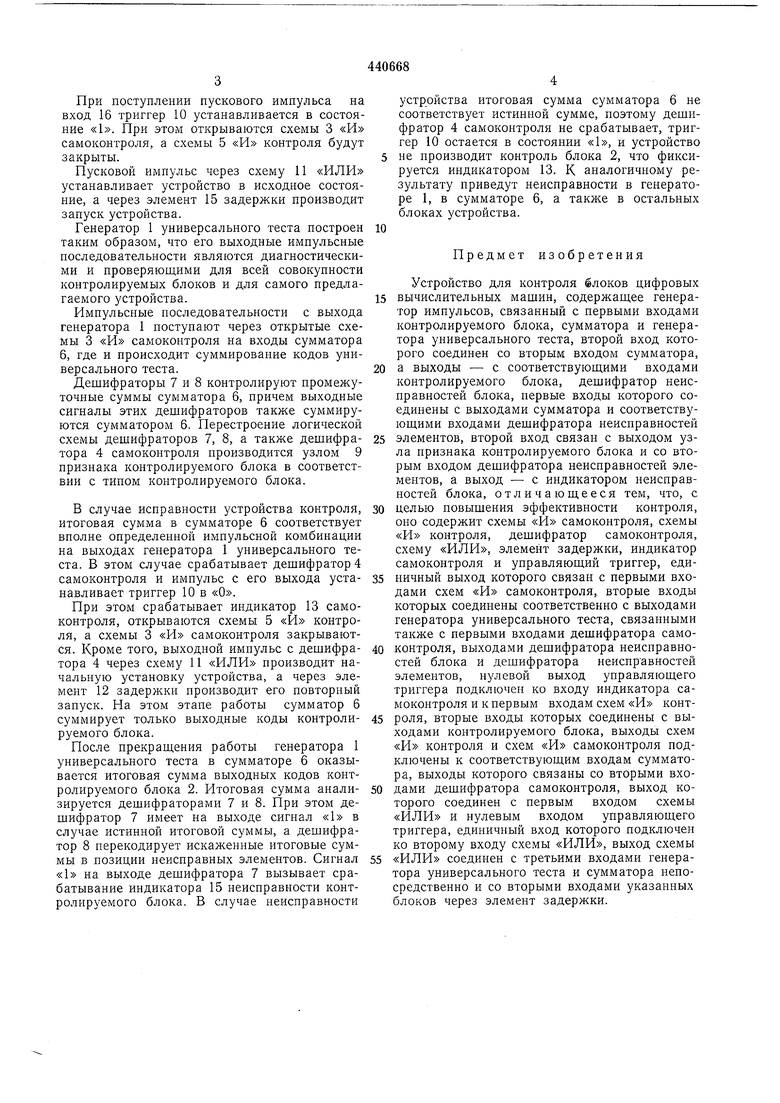

Иа чертеже приведена блок-схема предложенного устройства.

Оно содержит генератор 1 универсального теста, подключаемый ко входам проверяемого блока 2, схемы 3 «И самоконтроля, дешифратор 4 самоконтроля, схемы 5 «И контроля, сумматор б, дешифратор 7 неисправностей

блока, дешифратор 8 неисправностей элементов, узел 9 признака контролируемого блока, управляющий триггер 10, схему 11 «ИЛИ, элемент 12 задержки, индикатор 13 самоконтроля, генератор 14 импульсов и индикатор 15

неисправности блока.

При поступлении пускового импульса на вход 16 триггер 10 устанавливается в состояние «1. При этом открываются схемы 3 «И самоконтроля, а схемы 5 «И контроля будут закрыты.

Пусковой импульс через схему 11 «ИЛИ устанавливает устройство в исходное состояние, а через элемент 15 задержки производит запуск устройства.

Генератор 1 универсального теста построен таким образом, что его выходные импульсные последовательности являются диагностическими и проверяющими для всей совокупности контролируемых блоков и для самого предлагаемого устройства.

Импульсные последовательности с выхода генератора 1 поступают через открытые схемы 3 «И самоконтроля на входы сумматора 6, где и происходит суммирование кодов универсального теста.

Дешифраторы 7 и 8 контролируют нромел уточные суммы сумматора 6, причем выходные сигналы этих дешифраторов также суммируются сумматором 6. Перестроение логической схемы дешифраторов 7, 8, а также дешифратора 4 самоконтроля производится узлом 9 признака контролируемого блока в соответствии с типом контролируемого блока.

В случае исправности устройства контроля, итоговая сумма в сумматоре 6 соответствует вполне определенной импульсной комбинации на выходах генератора 1 универсального теста. В этом случае срабатывает дешифратор 4 самоконтроля и импульс с его выхода устанавливает триггер 10 в «О.

При этом срабатывает индикатор 13 самоконтроля, открываются схемы 5 «И контроля, а схемы 3 «И самоконтроля закрываются. Кроме того, выходной импульс с дешифратора 4 через схему 11 «ИЛИ производит начальную установку устройства, а через элемент 12 задержки производит его повторный запуск. На этом этапе работы сумматор 6 суммирует только выходные коды контролируемого блока.

После прекраш,ения работы генератора 1 универсального теста в сумматоре 6 оказывается итоговая сумма выходных кодов контролируемого блока 2. Итоговая сумма анализируется дешифраторами 7 и 8. При этом дешифратор 7 имеет на выходе сигнал «1 в случае истинной итоговой суммы, а дешифратор 8 перекодирует искаженные итоговые суммы в позиции неисправных элементов. Сигнал «1 на выходе дешифратора 7 вызывает срабатывание индикатора 15 неисправности контролируемого блока. В случае неисправности

устройства итоговая сумма сумматора 6 не соответствует истинной сумме, поэтому дешифратор 4 самоконтроля не срабатывает, триггер 10 остается в состоянии «1, и устройство 5 не производит контроль блока 2, что фиксируется индикатором 13. К аналогичному результату приведут неисправности в генераторе 1, в сумматоре 6, а также в остальных блоках устройства. 10

Предмет изобретения

Устройство для контроля блоков цифровых

15 вычислительных машин, содержащее генератор импульсов, связанный с первыми входами контролируемого блока, сумматора и генератора универсального теста, второй вход которого соединен со вторым входом сумматора,

0 а выходы - с соответствующими входами контролируемого блока, дешифратор неисправностей блока, первые входы которого соединены с выходами сумматора и соответствующими входами дешифратора неисправностей

5 элементов, второй вход связан с выходом узла признака контролируемого блока и со вторым входом дешифратора неисправностей элементов, а выход - с индикатором неисправностей блока, отличающееся тем, что, с

0 целью повышения эффективности контроля, оно содержит схемы «И самоконтроля, схемы «И контроля, дешифратор самоконтроля, схему «ИЛИ, элемент задержки, индикатор самоконтроля и управляюший триггер, единичный выход которого связан с первыми входами схем «И самоконтроля, вторые входы которых соединены соответственно с выходами генератора универсального теста, связанными также с первыми входами дешифратора самоконтроля, выходами дешифратора неисправностей блока и дешифратора неисправностей элементов, нулевой выход управляюшего триггера подключен ко входу индикатора самоконтроля и к первым входам схем «И контроля, вторые входы которых соединены с выходами контролируемого блока, выходы схем «И контроля и схем «И самоконтроля подключены к соответствующим входам сумматора, выходы которого связаны со вторыми входами дешифратора самоконтроля, выход которого соединен с первым входом схемы «ИЛИ и нулевым входом управляющего триггера, единичный вход которого подключен ко второму входу схемы «ИЛИ, выход схемы

«ИЛИ соединен с третьими входами генератора универсального теста и сумматора непосредственно и со вторыми входами указанных блоков через элемент задержки.

Позиции неиспрабHbif. злементоб

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения неисправностей | 1973 |

|

SU478309A1 |

| Устройство для обнаружения неисправностей | 1974 |

|

SU514294A1 |

| Устройство для контроля логических блоков | 1975 |

|

SU558266A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1264186A1 |

| Устройство для построения диагностического теста и диагностирования комбинационных схем | 1983 |

|

SU1160420A2 |

| Устройство для контроля регистра сдвига | 1978 |

|

SU752487A1 |

| Устройство для контроля аналоговых объектов | 1985 |

|

SU1288702A1 |

| Устройство для контроля цифровых блоков памяти | 1985 |

|

SU1256101A1 |

| Устройство для контроля каналов записи аппарата магнитной записи | 1986 |

|

SU1411818A1 |

| Устройство для контроля цифровых узлов | 1980 |

|

SU911532A1 |

Авторы

Даты

1974-08-25—Публикация

1972-03-27—Подача