(54) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ НЕИСПРАВНОСТЕЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения неисправностей | 1974 |

|

SU514294A1 |

| Устройство для контроля логических блоков | 1975 |

|

SU558266A1 |

| Генератор тестовой псевдослучайной двоичной последовательности | 1987 |

|

SU1640699A1 |

| Устройство для контроля цифровых блоков | 1978 |

|

SU706849A1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Устройство для контроля логических узлов | 1981 |

|

SU968816A1 |

| Устройство для контроля цифровых блоков | 1982 |

|

SU1037261A1 |

| Устройство для контроля неисправностей аппаратуры | 1981 |

|

SU966668A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для контроля цифровых узлов | 1980 |

|

SU911532A1 |

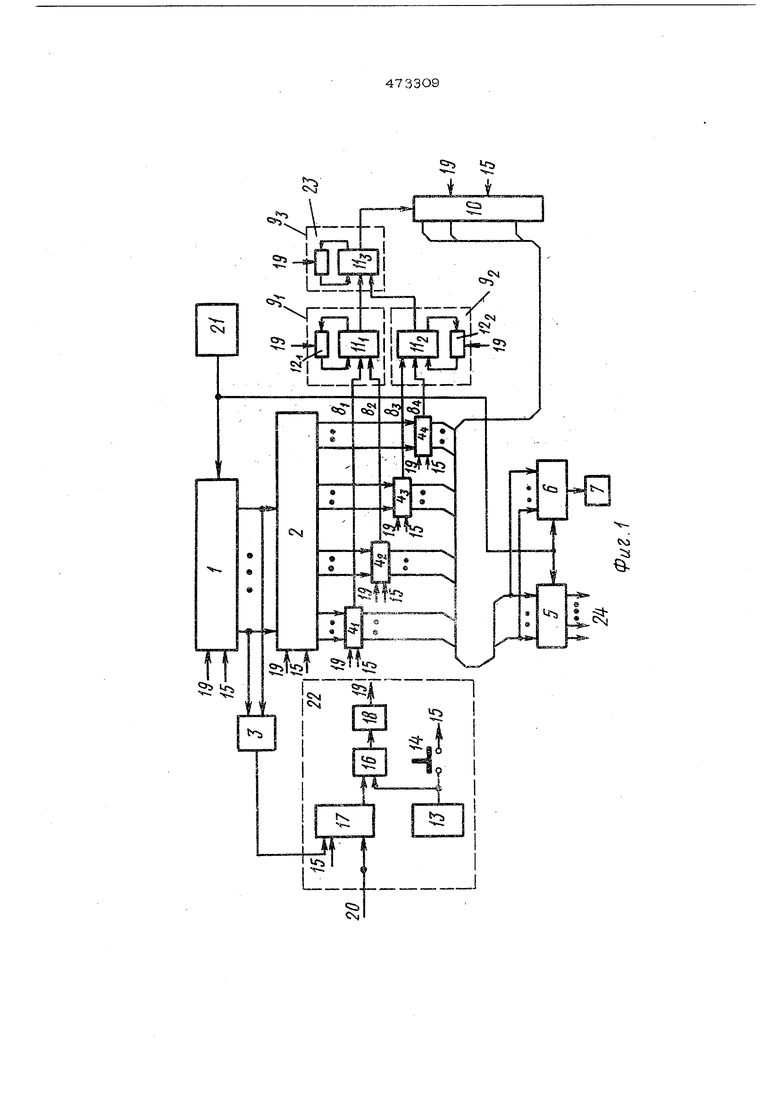

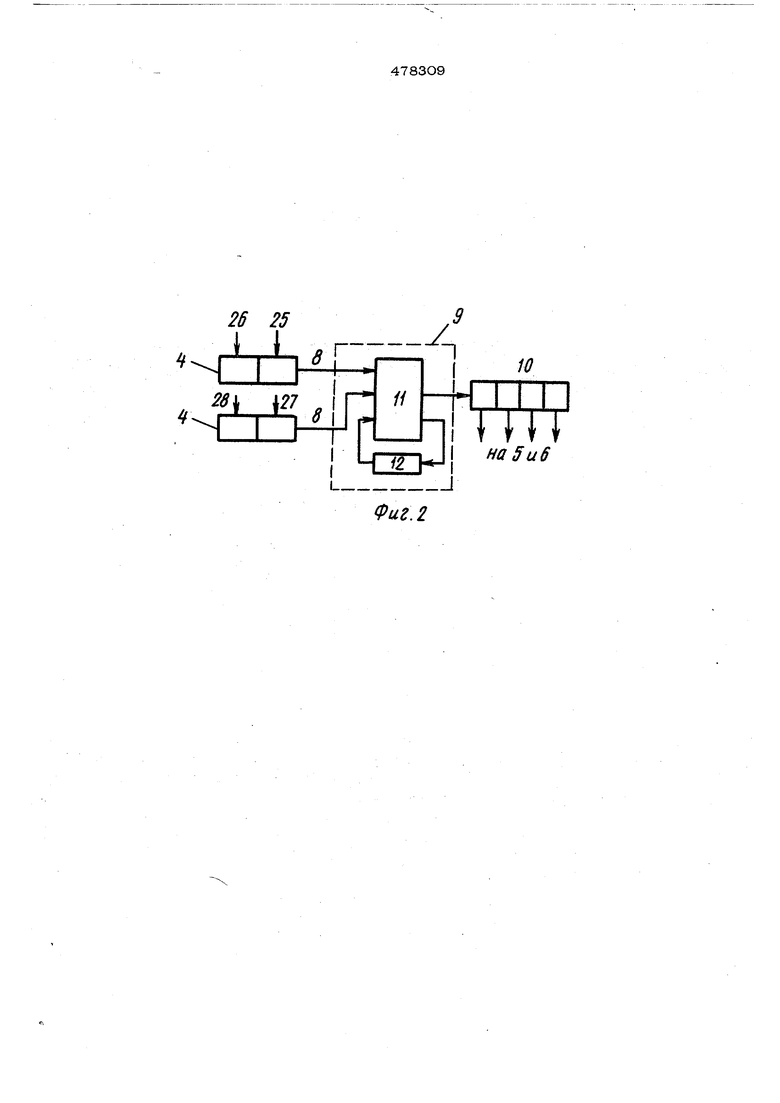

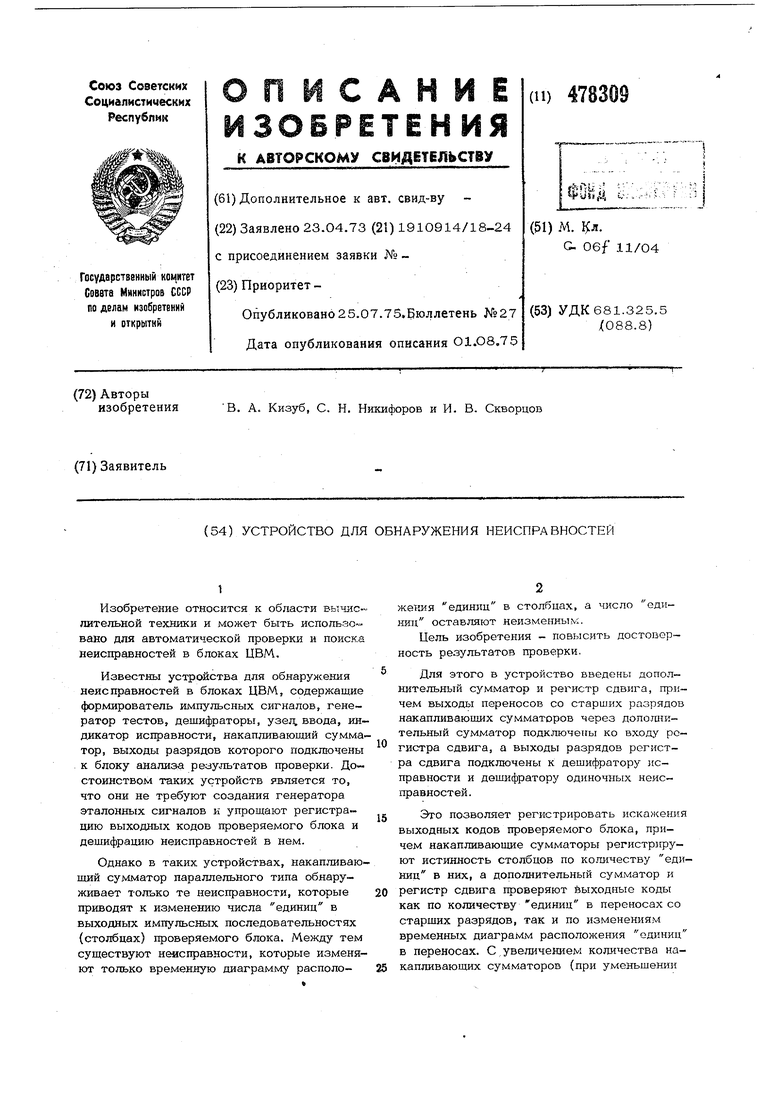

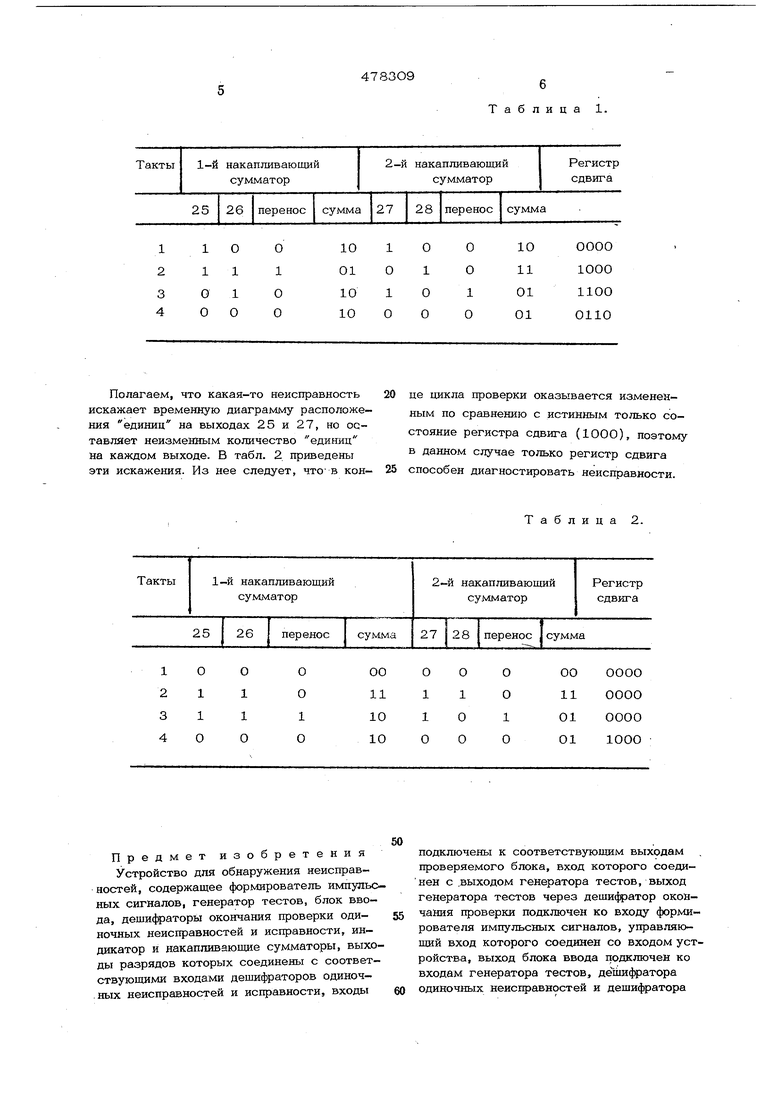

Изобретение относится к области вычислительной техники и может быть использовано для автоматической проверки и поиска неисправностей в блоках ЦВМ. Известны устройства для обнарухсения неисправностей в блоках ЦВМ, содержащие формирователь импульсных сигналов, генератор тестов, дешифраторы, узел, ввода, индикатор исправности, накапливающий сумма тор, выходы разрядов которого подключены к блоку анализа результатов проверки. Достоинством таких устройств является то, что они не требуют создания генератора эталонных сигналов и упрощают регистрацию выходных кодов проверяемого блока и дещифрацию неисправностей в нем. Однако в таких устройствах, накапливаю щий сумматор параллельного типа обнаруживает только те неисправности, которые приводят к изменению числа единиц в выходных импульсных последовательностях (столбцах) проверяемого блока. Между тем существуют неисправности, которые изменяют только временную диаграмму расположения единиц в столбцах, а число единиц оставляют неизменны :. Цель изобретения - повысить достоверность результатов проверки. Для этого в устройство введены дополнительный сумматор и регистр сдвига, причем выходы переносов со старших разрядов накапливающих сумматоров через ДОПОЛНР;тельный сумматор подключены ко входу регистра сдвига, а выходы разрядов регистра сдвига подключены к дещифратору исправности и дещифратору одиночных неисправностей. Это позволяет регистрировать искажения выходных кодов проверяемого блока, причем накапливающие сумматоры регистрируют истинность столбцов по количеству единиц Б них, а дополнительный сумматор и регистр сдвига проверяют быходные коды как по количеству единиц в переносах со старщих разрядов, так и по изменениям временных диаграмм расположения единиц в переносах. С увеличением количества накапливающих сумматоров (при уменьшении разрядности каждого) эффективность прове рок увеличивается. На фиг. 1 приведена схема устройства; ла фиг. 2 - пример для пояснения его работы. Генератор 1 тестов подключен своими выходами к проверяемому блоку 2 и к дешифратору 3 окончания проверки. Проверяе мый блок 2 всеми своими выходами соединен с накапливающими сумматорами параллельного типа, а выходы разрядов накапливающих сумматоров подключены к дешифратору 5 одиночных.-неисправностей и параллельно - к деши атору 6 исправности, который соединен с индикатором 7. Выходы 8 -8 переносов со старших разрядов накапливающих сумматоров подключены через одноразрядные сумматоры 9-9 - -13 последовательного действия ко входу регис ра 10 сдвига. Одноразрядные сумматоры 9-9 содержат комбинационные суммато- 1 3 одно- и элементы тактной задержки, которые подключены своими входами к выходам переносов комбинационных сумматоров, а выходы подключены на входы тех же комбинационных cy.iAMaTopOB. Выходы сумматоров 11 соединены со входами последующих одноразрядных сумматоров 9. Мультивибратор 13 подключен через кнопку 14 к шине 15 установки и к BeHTHJno 16, который соединен другим своим входом с единичным выходом триггера 17. Вентиль 16 соединен со входом усилителя 18, выход 19 которого подключен к узлам устройства. Триггер 17 устанавливается в 1 через вход 20 запуска. Дешифраторы 5 и 6, а также генератор 1 тестов перестраивается на проверку блоков определенного типа с помощью блока ввода 21; 22 и 23 - соответственно формирователь импульсных сигналов и дополнительный сумматор, выполненный на основе сумматоров 9; 24 - выходы дешифратора одиночных неисправностей; 25-28выходы проверяемого блока. Устройство работает следующим образом. При нажимании кнопки 14 на входы 15 установки поступают им 1ульсы, которые устанавливают в начальноесостояние все узлы устройства и проверяемого блока 2. При поступлении сигнала пуска по входу 20 триггер 17 устанавливается в единичное состояние, при этом триггер 17 открывает вентиль 16, и тактовые импульсы с выхода мультивибратора 13 через вентиль 16 и усилитель 18 поступают на шину 19. Генератор I тестов начинает выдавать по всем своим выходам импульсные последовательности, проверяющие блок 2. Выходные коды проверяемого блока 2 суммируются и хранятся в накапливающих сумматорах 4 параллельного типа, а последовательные коды переносов со старших разрядов сумматоров 4, поразрядно суммируясь в каскадах одноразр$1дных сумматоров 9 последовательного действия, поступают на вход регистра 10 сдвига. При этом переносы последовательного суммирования осуществляются с помощью элементов 12 однотактной задержки. Процесс генерации тестов и работы всего устройства продолжается до появления на выходах генератора 1 тестов комбинации, означающей окончание цикла проверки. При этом срабатывает дешифратор 3, и появляющийся на его выходе сигнал устанавливает триггер 17 в О, Вентиль 16 закрывается и поступление так- товых импульсов с выхода 19 усилителя 18 прекращается. В накапливающих сумматорах будут храниться итоговые суммы выходных кодов проверяемого блока 2, а в регистре 1О установится состояние, соответствующее сумме кодов переносов со старших разрядов сумматоров 4. Эти суммы определяют состояние проверяемого блока 2. Деши(}чэатор 6 исправности и индикатор 7 срабатывают при истинном значении сумм, а дешифратор 5 одиночных неисправностей перекодирует суммы (в случае их искажений) в позиции неисправных элементов. Сущность изобретения можно пояснить простейшим примером. Полагаем, проверяемый блок имеет четьфе выхода 25-28, которые соединяются со входами накапливающих сумматоров 4. В табл. 1 приведены примерные выходные коды исправного проверяемого блока, а также показаны состояния накапливающих сумматоров на каждом такте цикла проверки. В этой же таблице показаны (старшим разрядом вниз) последовательные коды переносов: со. старшего разряда первого накапливающего сумматора (ООЮ) и со старшего разряда второго накапливающего сумматора (010б). В регистре сдвига, в конце цикла проверки, устанавливается сумма кодов переносов (ОНО), а накапливающих сумматорах - итоговые уммы 10 и О1. Эти суммы дещифрируютя как исправные.

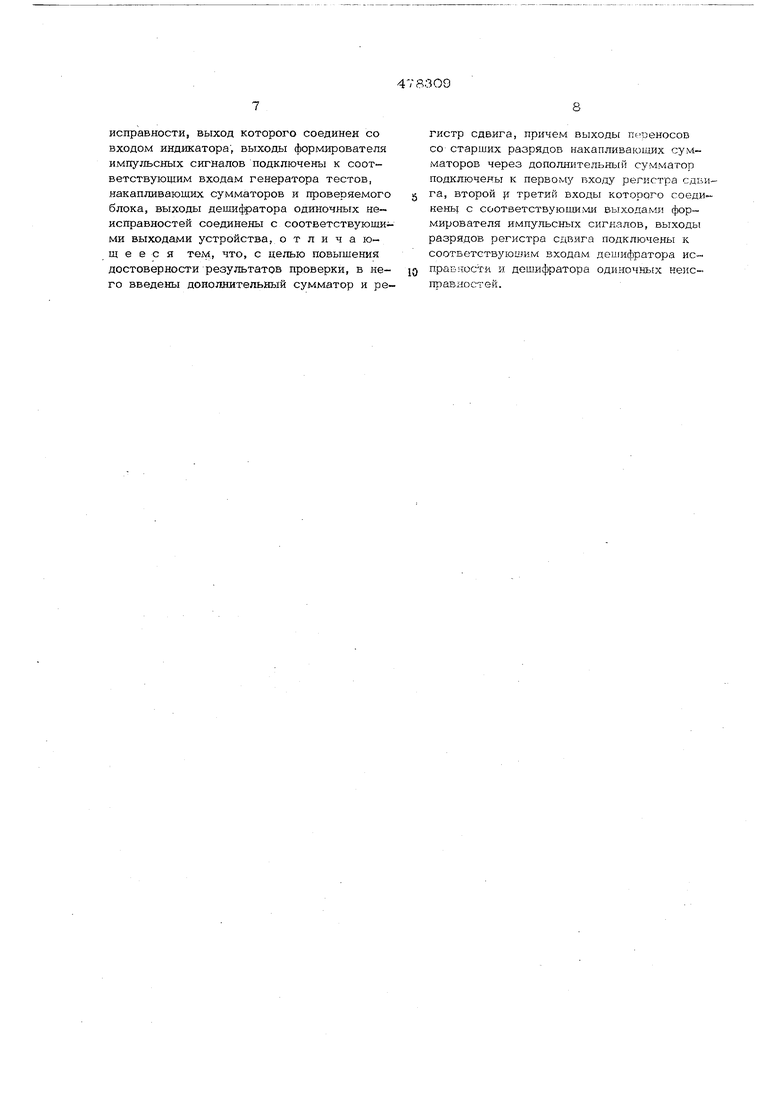

Полагаем, что какая-то неисправность искажает временную диаграмму расположения единиц на выходах 25 и 27, но оставляет неизменным количество единиц на каждом выходе. В табл. 2 приведены эти искажения. Из нее следует, что в кон- Предмет изобретения Устройство для обнаружения неисправностей, содержащее формирователь импульс ных сигналов, генератор тестов, блок ввода, дешифраторы окончания проверки одиночных неисправностей и исправности, индикатор и накапливающие сумматоры, выхо ды разрядов которых соединены с соответствующими входами дешифраторов одиноч.ных неисправностей и исправности, входы

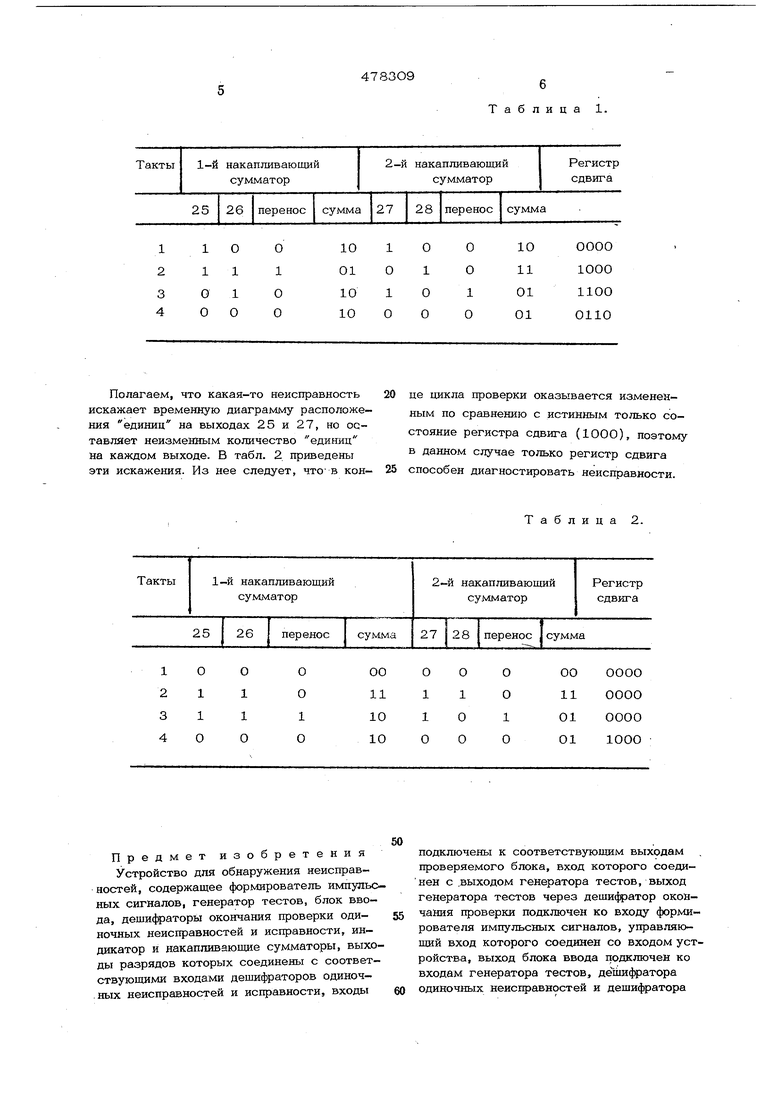

Таблица 1.

це цикла проверки оказывается измененным по сравнению с истинным только состояние регистра сдвига (1ООО), поэтому в данном случае только регистр сдвига способен диагностировать неисправности.

Таблица 2. подключены к соответствующим выходам проверяемого блока, вход которого соединен с .выходом генератора тестов, выход генератора тестов через деши(}ратор окончания проверки подключен ко входу формирователя импульсных сигналов, управляющий вход которого соединен со входом устройства, выход блока ввода подключен ко входам генератора тестов, дёши(|ратора одиночных неисправностей и дешифратора

7

исправности, выход которого соединен со входом индикатора, выходы формирователя импу/гьсных сигналов подключены к соответствующим входам генератора тестов, накапливающих сумматоров и проверяемого блока, выходы дешифратора ОДИНОЧНЬЕХ неисправностей соединены с соответствующими выходами устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности результатов проверки, в него введены доиолнительный сумматор и ре8

гкстр сдвига, причем выходы переносов со старших разрядов накапливающих сумматоров через дополнительный сумматор подключены к первому входу регистра сдвига, второй р третий входы которого соединены с соответствующими выходами формирователя импульсных сигналов, выходы разрядов регистра сдвига подключены к соответствующим входам дешифратора исправности и дешифратора одиночных неисправностей.

Авторы

Даты

1975-07-25—Публикация

1973-04-23—Подача