достигать величины 10 и более, построение регистра такой разрядности практически невозможно. Поэтому при реализации подобных устройств регистр сдвига выполняется закольцованным с помощью сумматора по модулю два. При этом, если неисправность, приводящая только к изменению выходной последовательности дополнительного сумматора, искал ает эту последовательность четное число раз и с периодом, равным или кратным числу разрядов закольцованного регистра сдвига, то она может быть и не обнаружена. Подобным образом могут проявляться как одиночные, так и кратные неиснравности. Это приводит к принятию неисправного блока за исправный.

Целью изобретения является повыщение достоверности результатов контроля.

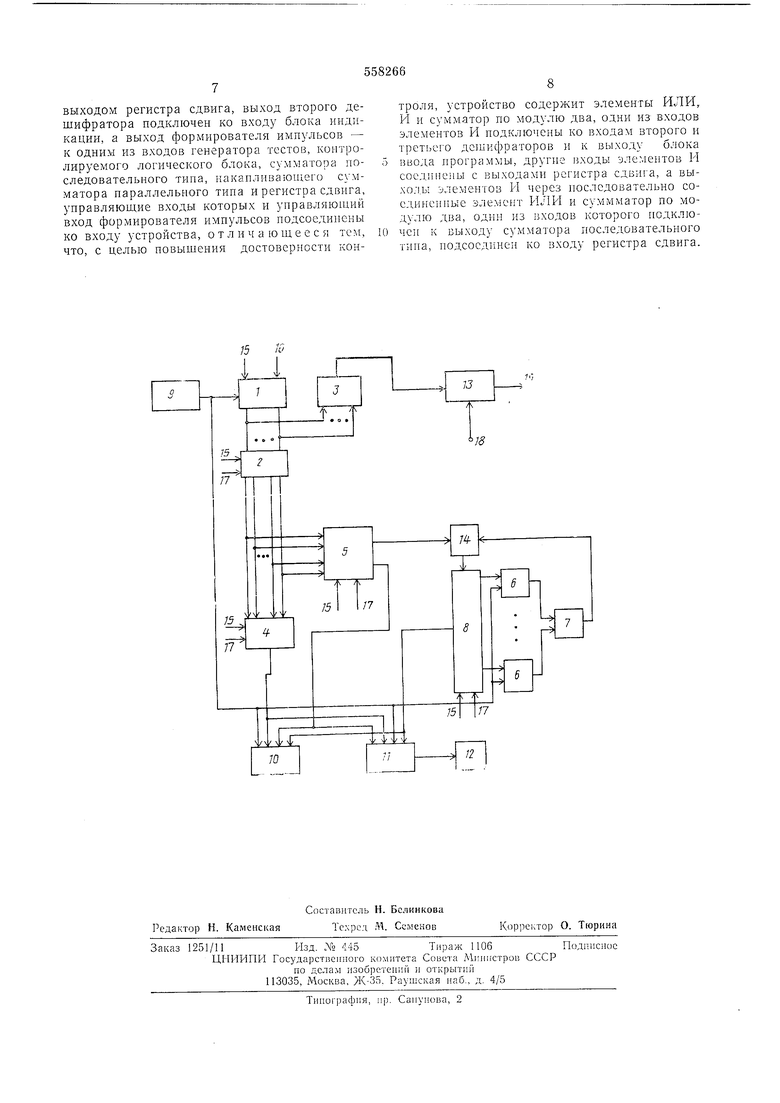

Это достигается тем, что предлагаемое устройство содержит элементы ИЛИ, И и сумматор по модулю два, одни из входов элементов И подключены ко входам второго и третьего дещифраторов и к выходу блока ввода программы, другие входы элементов И соединены с выходами регистра сдвига, а выходы элементов И через последовательно соединенные элемент ИЛИ и сумматор по модулю два, один из входов которого подключен к выходу сумматора последовательного типа, подсоединен ко входу регистра сдвига.

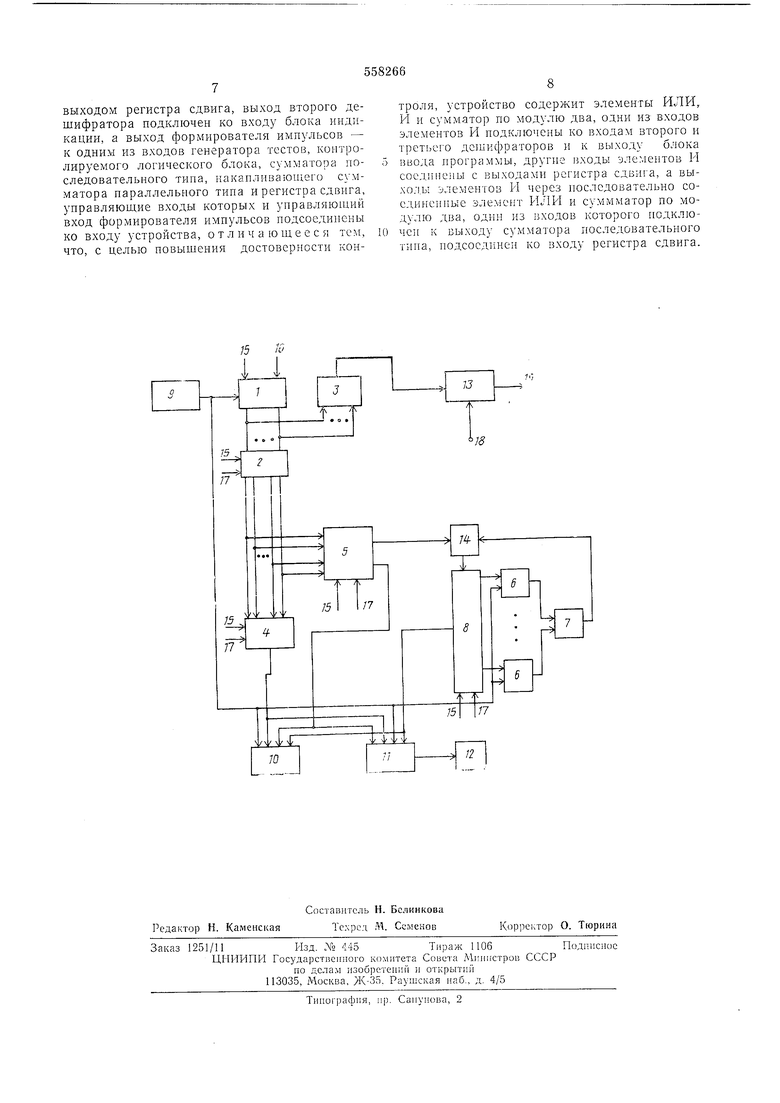

На чертеже показана блок-схема предлагаемого устройства, которая содержит генератор тестов 1, контролируемый логический блок 2, первый дешифратор 3, накапливающий сумматор нараллельпого типа 4, сумматор последовательного типа 5, элементы И 6, элемент ИЛР1 7, регистр сдвига 8, блок ввода программы 9, третий дешифратор 10, второй дешифратор 11, блок индикации 12, формирователь импульсов 13, сумматор по модулю два 14, выход 15 формирователя импульсов 13 подключен к входам 16 генератора тестов 1, контролируемого логического блока 2, сумматоров 4 и 5 и регистра сдвига 8, унравляющие входы 17 которых и уиравляющий вход 18 формирователя 13 являются входами устройства.

Устройство работает следующим образом.

При поступлении сигнала на управляющий вход 16 производится начальная установка всех узлов устройства, имеющих элементы памяти (например триггеры). Подача сигнала на управляющий вход 17 обеснечивает появление тактовых имнульсов на выходе 15 формирователя 13. Генератор тестов 1 начинает

выдавать по всем своим выходам импульсные иоследовательности, ироверяющие контролируемый логический блок 2. Выходные коды контролируемого логического блока 2 подвергаются операциям параллельного и носледовательного суммирования. Параллельное суммирование производится накапливающим сумматором параллельного типа 4, в котором и хранится результат суммирования. Последовательное суммирование выполняется в сумматоре последовательного тина 5, а результат суммирования через сумматор 14 по модулю два поступает на вход регистра сдвига 8. Регистр 8 закольцовывается через один

из элементов И 6, элемент ИЛИ 7 и сумматор 14. Модуль закольцовки, т. е. один из элементов И 6 выбирается с номощью блока ввода программы 9. Процесс генерации тестов и работа всего устройства нродолл ается до появления на выходах генератора тестов 1 комбинации, означающей окончание цикла проверки. При этом срабатывает первый дешифратор 3 и появляющийся на его выходе сигнал запрещает выработку тактовых импульсов на выходе 15 формирователя и.мпульсов 13. В накапливающем сумматоре 4 будет храниться итоговая сумма выходных кодов (строк) контролируемого логического блока 2, в регистре 8 будет находиться итоговая сумма выходных кодов (столбцов), а сумматор 5 будет хранить «единицы переполнения от суммирования столбцов.

Эти суммы и «единицы переполнения онределяют состояние контролируемого логического блока 2. Второй дешифратор 11 и блок индикации 12 срабатывают при истинном значении сумм и «единиц переносов, а третий дешифратор 10 перекодирует значения с}мм и «единиц переносов (в случае их нскаження

т. е. при одиночных неисправностях) в позиции неисправных элементов.

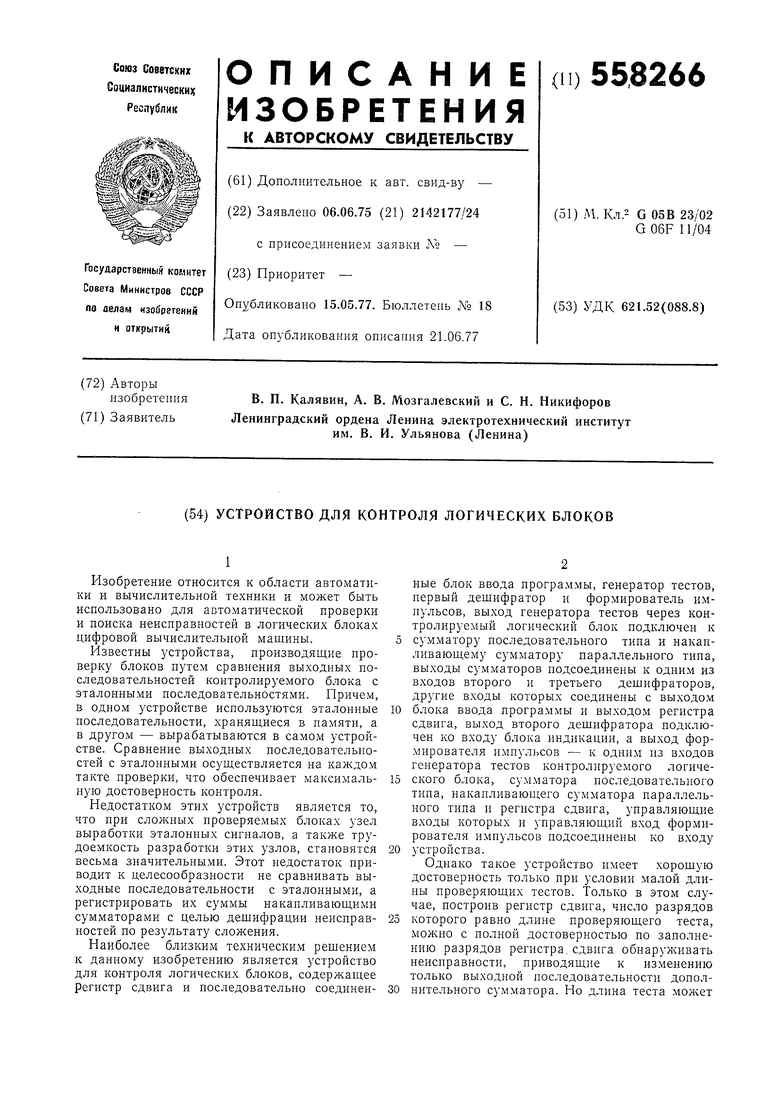

Сущность изобретения можно пояснить следующим иримером. Полагаем, что длина теста равна 15. В табл. 1 приведены примерные

значения выходных последовательностей сумматора последовательного типа для иснравного и неисправного (искажены компоненты в 4-ом н 10-ом тактах) контролируемого логического блоков. Причем в иеисправном контролируемом логическом блоке неисправность приводит только к искажению выходной последовательности сумматора последовательиого типа, значения сумм накапливающего сумматора идентичны и не ириводятся.

Таблица 1

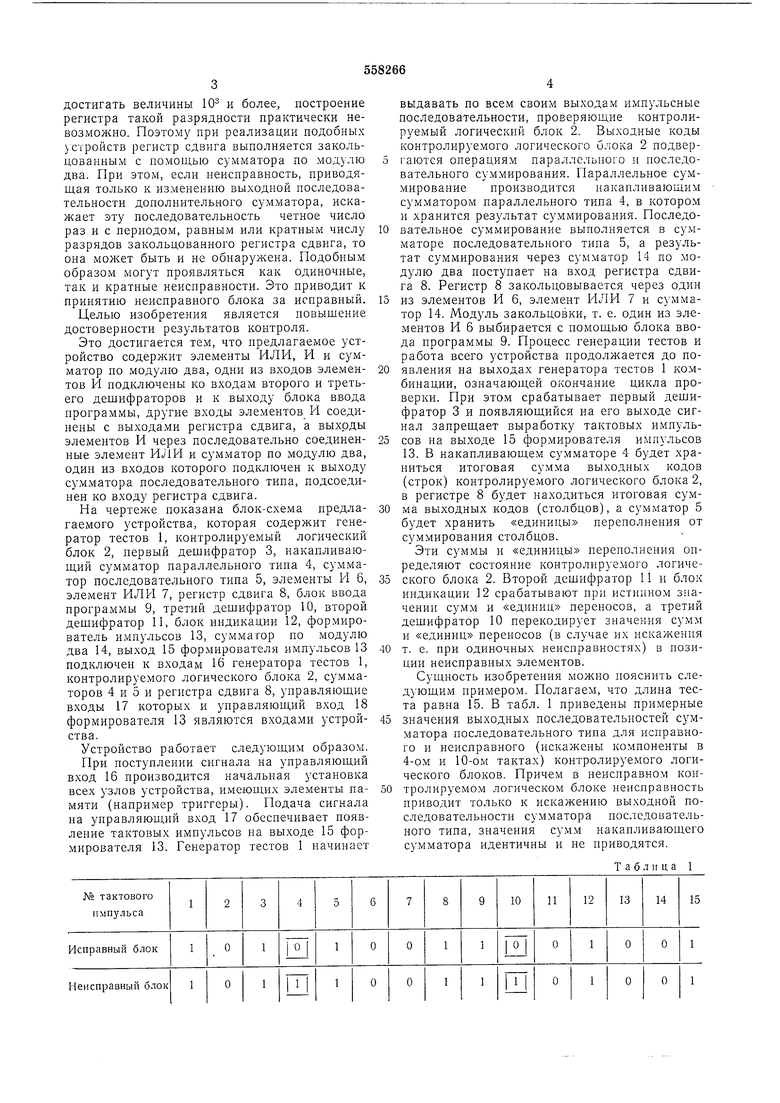

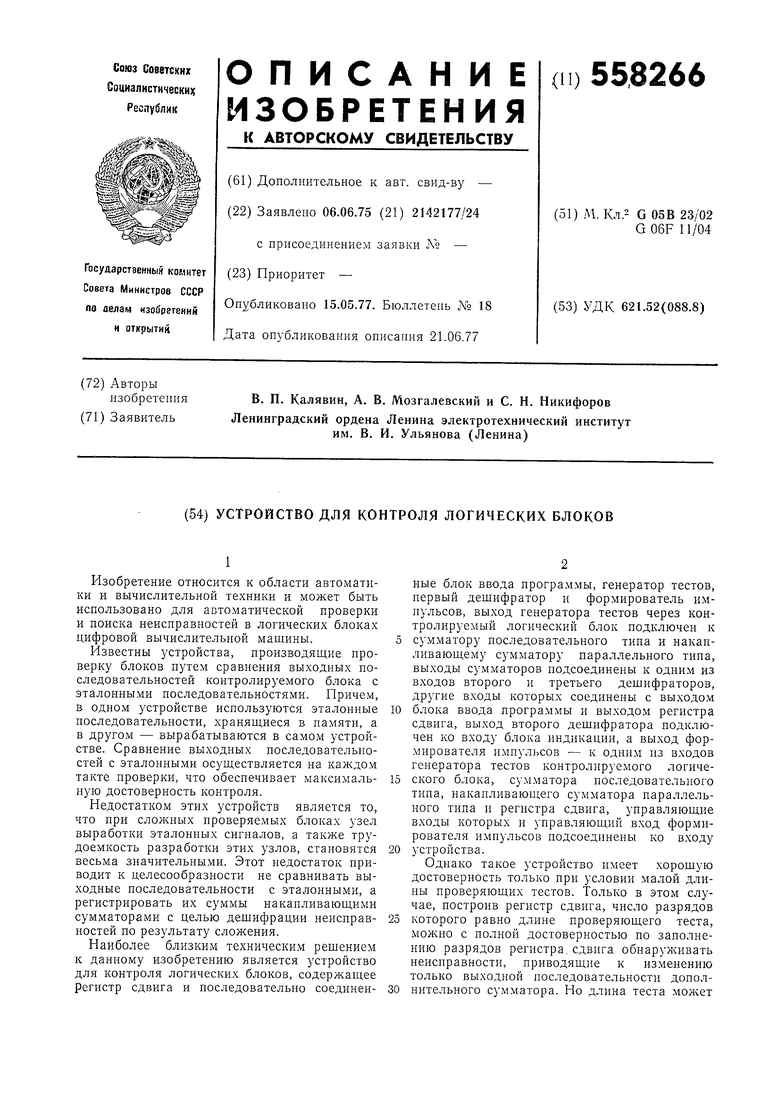

Выбранное значение модуля закольцовкн равнялось «3. В табл. 2 и 3 показано формирование итоговых сумм выходных последовательностей cyMMaTOjia последовательного тина для исправного и 1еиснравного контроляруемых логических блоков.

Таблица 2

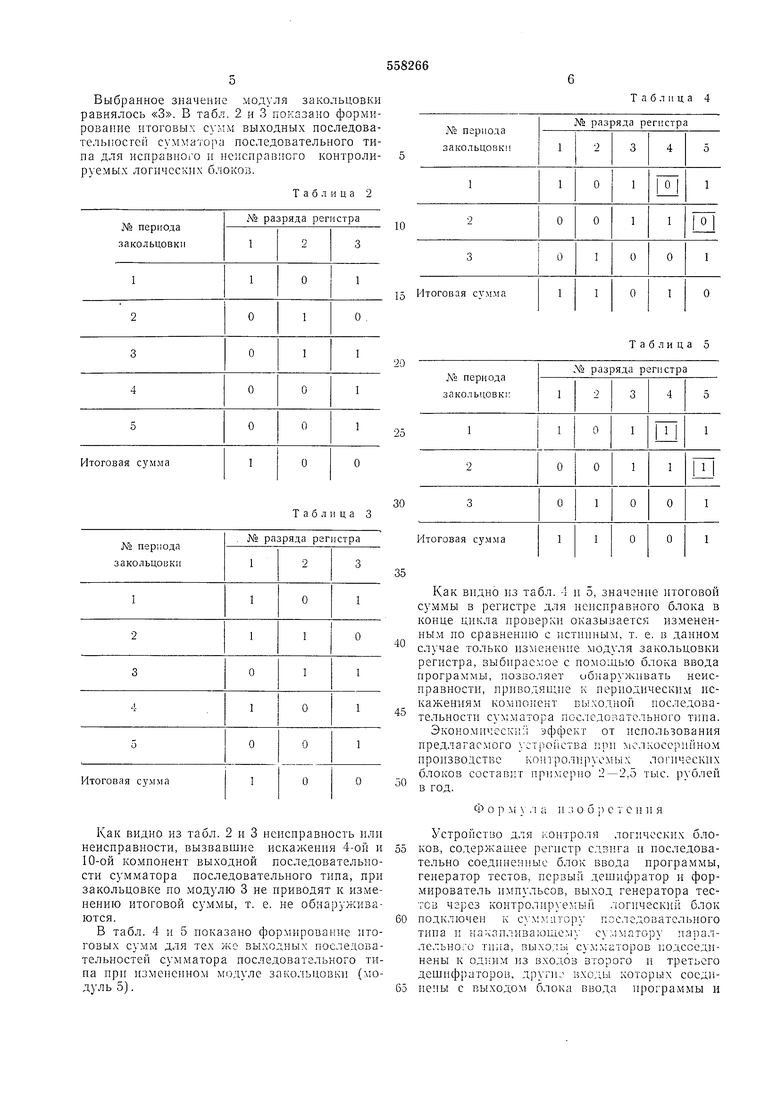

Таблица 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения неисправностей | 1974 |

|

SU514294A1 |

| Устройство для обнаружения неисправностей | 1973 |

|

SU478309A1 |

| Устройство для контроля логических блоков | 1978 |

|

SU763901A1 |

| Устройство для контроля логических узлов | 1981 |

|

SU968816A1 |

| Устройство для контроля блоков цифровых вычислительных машин | 1972 |

|

SU440668A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1180902A1 |

| Устройство для контроля логических узлов | 1980 |

|

SU890398A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Тренажер оператора радиоэлектронной аппаратуры | 1989 |

|

SU1658193A1 |

Таблица 3

Как видно из табл. 2 и 3 неисправность илн неисправности, вызвавшие искажения 4-ой и 10-ой комионент выходной последовательности сумматора последовательного типа, при закольцовке но модулю 3 не приводят к изменению итоговой суммы, т. е. не обнаруживаются.

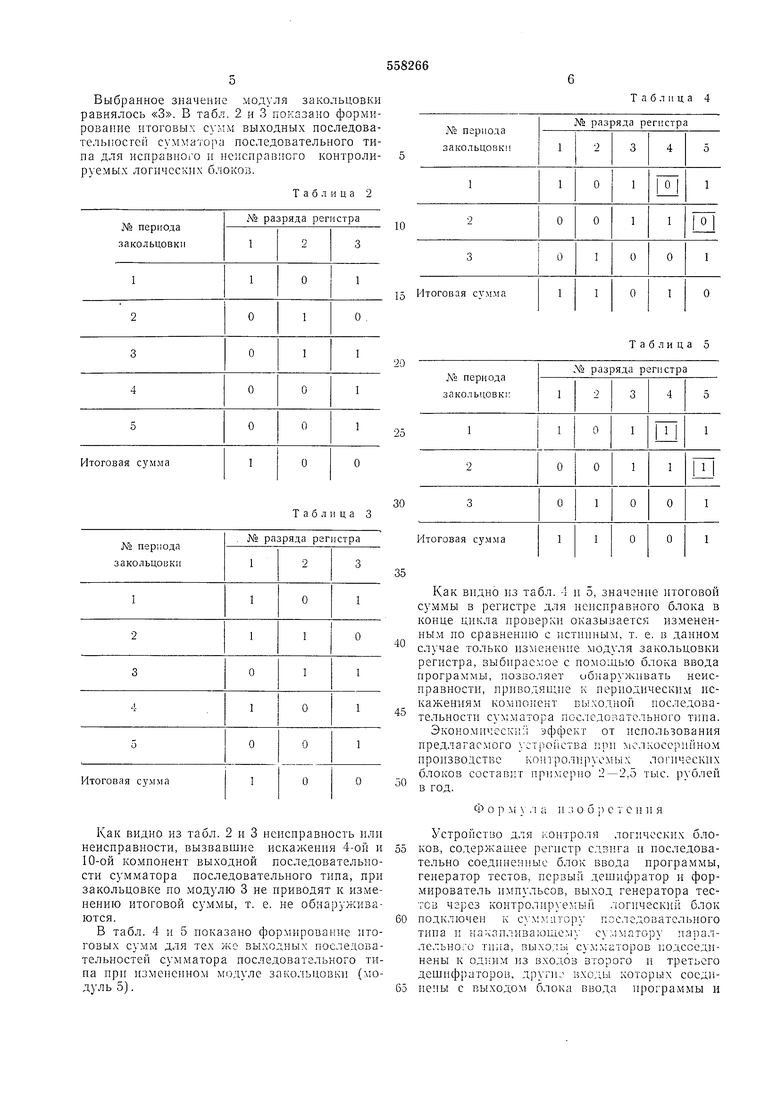

В табл. 4 и 5 показано формирование итоговых сумм для тех }ке выходных последовательностей сумматора последовательного тииа нри измененном модуле закольиовки (модуль 5).

Таблица 5

Как видно из табл. 4 и 5, значение итоговой суммы в регистре для неисправного блока в конце цикла проверки оказыиаетс.ч измененным по сравнению с истинным, т. е. в данном случае только изменение модуля закольцовки регистра, выбираемое с номощью блока ввода программы, позволяет ибнаружпвать неиснравности, приводящие к периодическим искажениям компонент выходной последова5ельностн сумматора последовательного .

Экономически эффект от использования пpeдлaгac ioгo ycijx iicTBa при мелкосерийном производстве контролируемых логических блоков составит примерно 2-2,5 тыс. рублей в год.

Ф о р .i у л а и 3 о б 11 е т е н н я

Устройство для контроля логических блоков, содержащее регистр сдвига и последовательно соединенные блок ввода программы, генератор теетов, первый дешифратор и формирователь импульсов, выход генератора тестев через контролируе, логически блок подключен к сумматору последовательпого типа и накапливающему сумматору параллельного типа, выходы сумматоров подсоедииены к одним из входов второго и третьего дешифраторов, други. входы которых соединены с выходом блока ввода программы н

выходом регистра сдвига, выход второго дешифратора подключеи ко входу блока индикации, а выход е1)орл1ирователя имиульсов - к одним из входов генератора тестов, контролируемого логического блока, сумматора последовательного типа, пакапливаюпхего сумматора иараллельиого типа и регистра сдвига, управляющие входы которых и уиравляюп1ий вход формирователя имиульсов подсоединены ко входу устройства, отличающееся тем, что, с целью повьииения достоверности контроля, устройство содержит элементы ИЛИ, И и сумматор по модулю два, одни из входов элементов PI подключены ко входам второго и третьего дешифраторов и к выходу блока ввода программы, другие входы элементов И соедн1геиь с выходами регистра сдвига, а выходы элементов И через последовательно соединенные элемент ИЛИ и суммматор ио модулю два, одни из входов которого подключен к выходу сумматора последовательного типа, иодсоединен ко входу регистра сдвига.

Авторы

Даты

1977-05-15—Публикация

1975-06-06—Подача