(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ 1ЩФРОВЫХ УЗЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1978 |

|

SU706849A1 |

| Устройство для контроля и диагностики дискретных объектов | 1983 |

|

SU1109756A1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1679487A1 |

| Устройство для контроля и диагностики цифровых узлов | 1980 |

|

SU896627A1 |

| Устройство для контроля логических блоков | 1983 |

|

SU1149266A1 |

| Устройство для контроля логических блоков | 1980 |

|

SU902018A1 |

| Устройство для диагностирования @ групп однотипных логических блоков | 1984 |

|

SU1196878A1 |

| Устройство для контроля цифровых блоков | 1982 |

|

SU1037261A1 |

| Устройство для контроля многовыходных цифровых узлов | 1982 |

|

SU1019454A1 |

| Устройство для контроля логических блоков | 1982 |

|

SU1105897A1 |

Изобретение относится к автоматик и вычислительной технике и может быт использовано в системах тестового ко троля дискретных блоков на этапе тех нического контроля и при эксплуатации, обеспечивая высокую достоверность контроля и сокращение времени проверки партии однотипных изделий. Известно устройство для контроля цифровых узлов,содержащее генератор тестов, выходы которого соединены с эталонным и контролируемым блоками, соединенными своими выходами с входами блоков сравнения, выходы ко торых соединены с входами блока ре-: гистрации и индикации К недостаткам известного у-стройства относятся низкая достоверность контроля в случае идентичных дефектов в эталонном и проверяемом блоках и значительные затраты времени при контроле партии однотипных изделий. Известно также устройство для контроля цифровых блоковi содержащее генератор тестов, выходы которого подключены к входу блока управления и к входам эталонного и контролируемых блоков, выходы которых через блоки сравнения подключены к блоку регистрации и индикации, выход и первый вход сумматора соединены соответственно с информационнымвходом и первым выходом регистра сдвига, вторые выходы которого подключены, через дешифратор исправности к входу индикатора исправности, а выходы блока управления соединены с управляющими входами генератора тестов и регистра сдвига 2J. Недостатком этого устройства является то, что имеется возможность записи информации в регистр- только из одного канала контролируемого блока, т.е. в устройстве отсутствует параллельная обработка выходного слова, что существенно увеличи39

вает время контроля при последовательной обработке всех выходов контролируемого блока.

Наиболее близким техническим решением к предлагаемому является устройство для контроля цифровых блоков, содержащее генератор тестов, выходы которого подключены к входу блока управления и к входам эталонного и контролируемого блоков, выходы которых через блоки сравнения подключаются к блоку регистрации и индикации, выход и первый вход сумматора соединены соответственно с информа:щонным входом и первым выходом регистра сдвига, вторые выходы которого подключены к дешифратору неисправностей и через дешифратор исправности к входу индикатора исправности, второй вход сумматора соединен с выходом блока пирамидальной свертки, входы которого соединены с выходами эталонного блока, а выходы блока управления соединены с управляющими входами генератора тестов з.

Работа известного устройства заключается в следующем.

При поступлении команды Пуск в блок управления, импульсы ijjaKTOвой частоты поступают на генератор тестов и на управляющий вход регистра сдвига. Генератор тестов выдает по всем выходам тестовые последовательности, поступающие на идентиные входы эталонного и контролируемого блоков. Ответные реакции этих блоков сравниваются между собой блоками сравнения. В случае рассогласования в каналах контроля сбои регистрируют блок регистрации и индикации. При полном соответствии ответных реакций эталонного и контролируемого блоков на тестовые последовательности, срабатывает индикатор блока регистрации и индикации, Выходные последовательности сигналов с эталонного блока преобразуются в одну последовательность сигналов при помощи блока пирамидальной свертки, после чего через сумматор записываются в регистр сдвига. Информация, которая переполняет регистр сдвига, поступает через сумматор на информационный вход регистра сдвига. Дешифратор исправности и индикатор исправности срабатывают при истинном знчении информации, записанной в ре4

гистр сдвига, а дешифратор неисправности перекодирует информацию в позиции неисправных элементов.

Однако в этом устройстве блок пирамидальной свертки не фиксирует искажение значений выходных сигналов эталонного блока на четном числе единиц, т.е. при подаче на вход блока тестового набора обнаруживается только такая неисправность, которая приводит к искажению значений выходных сигналов этого блока на нечетном чцсле единиц.

Таким образом, недостатком известного устройства является низкая достоверность контроля.

Цель изобретения - повышение достоверности контроля.

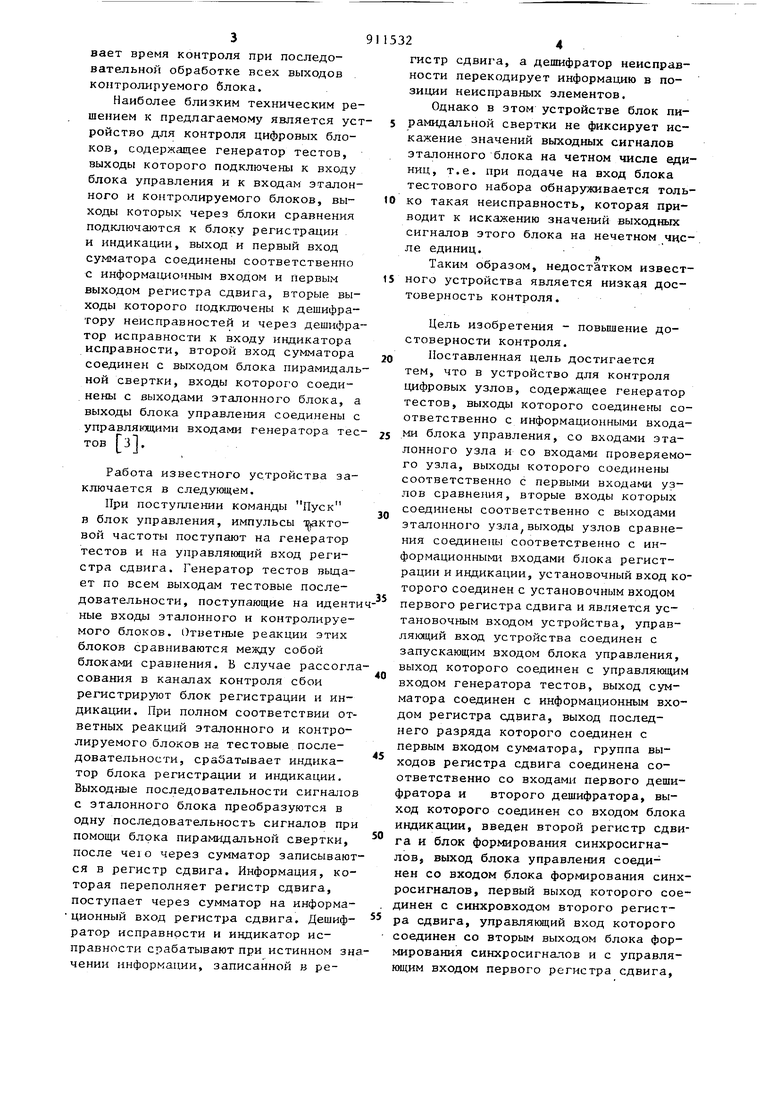

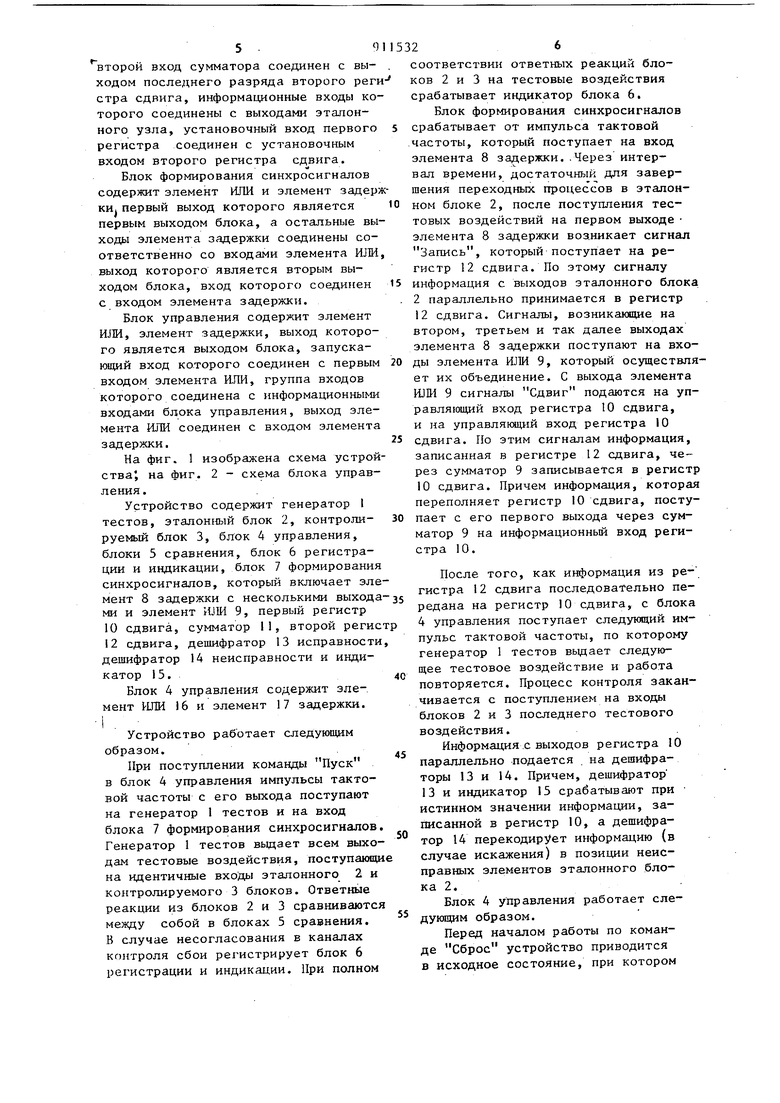

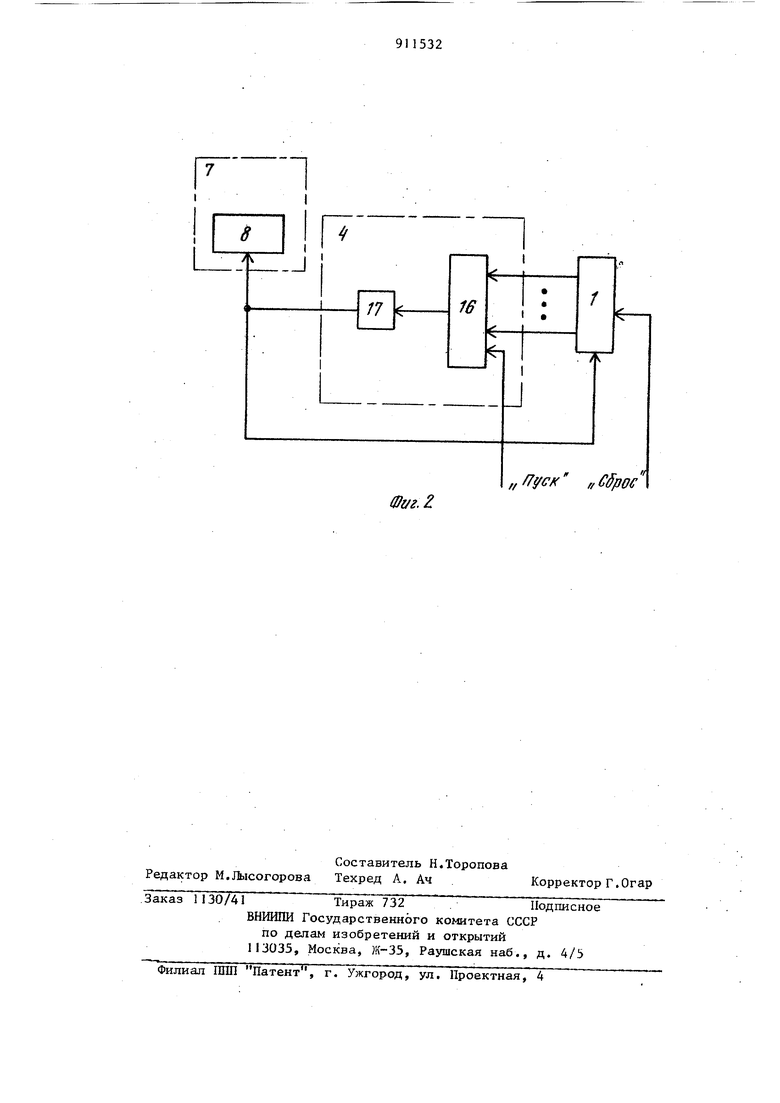

Поставленная цель достигается тем, что в устройство для контроля цифровых узлов, содержащее генератор тестов, выходы которого соединены соответственно с информацио}1ными входами блока управления, со входами эталонного узла и со входами проверяемого узла, выходы которого соединены соответственно с первыми входами узлов сравнения, вторые входы которых соединены соответственно с выходами эталонного узла,выходы узлов сравнения соединены соответственно с информационными входами блока регистрации и индикации, установочный вход которого соединен с установочным входом первого регистра сдвига и является установочным входом устройства, управляюций вход устройства соединен с запускающим входом блока управления, выход которого соединен с управляющим входом генератора тестов, выход сумматора соединен с информационным входом регистра сдвига, выход последнего разряда которого соединен с первым входом сумматора, группа выходов регистра сдвига соединена соответственно со входами первого дешифратора и второго дешифратора, выход которого соединен со входом блока индикации, введен второй регистр сдвига и блок формирования синхросигналов, выход блока управления соединен со входом блока формирования синхросигналов, первый выход которого соединен с синхровходом второго регистра сдвига, управляющий вход которого соединен со вторым выходом блока формирования синхросигналов и с управляющим входом первого регистра сдвига. второй вход сумматора соединен с выходом последнего разряда второго рег стра сдвига, информационные входы ко торого соединены с выходами эталонного узла, установочный вход первого регистра соединен с установочным входом второго регистра сдвига. Блок формирования синхросигналов содержит элемент ИЛИ и элемент задер ки, первый выход которого является первым выходом блока, а остальные вы ходы элемента задержки соединены соответственно со входами элемента ИЛИ выход которого является вторым выходом блока, вход которого соединен с входом элемента задержки. Блок управления содержит элемент ШШ, элемент задержки, выход которого является выходом блока, запускающий вход которого соединен с первым входом элемента ИЛИ, группа входов которого соединена с информационными входами блока управления, выход элемента ИЛИ соединен с входом элемента задержки. На фиг. 1 изображена схема устрой CTBaJ на фиг. 2 - схема блока управления. Устройство содержит генератор 1 тестов, эталонный блок 2, контролируемый блок 3, блок 4 управления, блоки 5 сравнения, блок 6 регистрации и индикации, блок 7 формирования синхросигналов, который включает эле мент 8 задержки с несколькими выхода ми и элемент ИЛИ 9, первый регистр 10 сдвига, сумматор 11, второй регис 12 сдвига, дешифратор 13 исправности дешифратор 14 неисправности и индикатор 15. Блок 4 управления содержит элемент ИЛИ 16 и элемент 17 задержки. Устройство работает следующим образом. При поступлении команды Пуск в блок 4 управления импульсы тактовой частоты с его выхода поступают на генератор 1 тестов и на вход блока 7 формирования синхросигналов. Генератор 1 тестов выдает всем выходам тестовые воздействия, поступающи на идентичные входы эталонного 2 и контролируемого 3 блоков. Ответные реакции из блоков 2 и 3 сравниваются между собой в блоках 5 сравнения. В случае несогласования в каналах контроля сбои регистрирует блок 6 регистрации и индикации. При полном соответствии ответных реакций блоков 2 и 3 на тестовые воздействия срабатывает индикатор блока 6, Блок формирования синхросигналов срабатывает от импульса тактовой частоты, который поступает на вход элемента 8 задержки. .Через интервал времени, достаточный для завершения переходных процессов в эталонном блоке 2, после поступления тестовых воздействий на первом выходе элемента 8 задержки возникает сигнал Запись, который поступает на регистр 12 сдвига. По этому сигналу информация с выходов эталонного блока 2 параллельно принимается в регистр 12 сдвига. Сигналы, возникающие на втором, третьем и так далее выходах элемента 8 задержки поступают на входы элемента ИЛИ 9, который осуществляет их объединение. С выхода элемента ШМ 9 сигналы Сдвиг подаются на управляющий вход регистра 10 сдвига, и на управлякяций вход регистра 10 сдвига. По этим сигналам информация, записанная в регистре 12 сдвига, через сумматор 9 записывается в регистр 10 сдвига. Причем информация, которая переполняет регистр 10 сдвига, поступает с его первого выхода через сумматор 9 на информационньй вход регистра 10. После того, как информация из регистра 12 сдвига последовательно передана на регистр 10 сдвига, с блока 4 управления поступает следуквдий импульс тактовой частоты, по которому генератор 1 тестов выдает следующее тестовое воздействие и работа повторяется. Процесс контроля заканчивается с поступлением на входы блоков 2 и 3 последнего тестового воздействия. Информация .с выходов регистра 10 параллельно подается . на дешифраторы 13 и 14. Причем, дешифратор 13 и индикатор 15 срабатывают при истинном значении информации, записанной в регистр 10, а дешифратор 14 перекодирует информацию (в случае искажения) в позиции неисправных элементов эталонного блока 2. Блок 4 управления работает следующим образом. Перед началом работы по команде Сброс устройство приводится в исходное состояние, при котором

на всех выходах генератора I тестов устанавливаются нулевые значения сигналов. При поступлении команды Пуск (соответствующей единичному значению сигнала на шине пуска) на вход элемента ИЛИ 16, на его выходе образуется единичный сигнал, который подается ,на вход элемента 17 задержки. С выхода элемента 17 задержки сигнал подается на вход генератора 1 тестов и на блок 7 формирования синхросигналов. Под воздействием этого сигнала генератор 1 тестов вырабатывает на своих выходах тестовое воздействие, представляющее собой комбинацию нулевых и единичных сигналов, а блок 7 формирует синхросигналы для управления работой регистров сдвига. Тестовое воздействие поступает на входы элемента ШИ 1 6. Единичный сигнал с выхода элемента ИЛИ 16 поступает на вход элемента .17 задержки, который обеспечивает задержку этого сигнала на интервал времени, необходимый устройству для работы по одному тестовому воздействию. В дальнейшем задержанный сигнал с выхода элемента 17 подается на генератор 1 тестов, под воздействием которого последний формирует очередное тестовое воздействие. Работа устройства заканчивается, когда все тестовые воздействия сформированы и генератор 1 тестов выдает на все свои выходы нулевые значения сигналов.

Схема представляет собой возможный вариант построения блока 4 управления устройства для контроля цифровых блоков.

Таким образом, при контроле цифрвых узлов предлагаемым устройством становится возможным проверять работоспособность одновременно двух блоков, получая информацию о годности первого из .блоков, условно названного эталонным, по информации, записанной в первом регистре, а другогопо ответной реакции на входные тесты, сравниваемого с первым блоком. При этом вероятность .обнаружения неисправностей не зависит от того, на четном или нечетном числе .эталонного блока проявилась та или иная неисправность.

Форму.ча изобретения 1. Устройство для контроля цифровых узлов, содержащее генератор тестов, выходы которого соединены соответственно с информационныьш входами блока управления, с входами эталонного узла и с входами проверяемого 5 узла, выходы которого соединены соответственно с первыми входами узлов сравнения, вторые входы которых соединены соответственно с выходами эталонного узла, выходы узлов сравнения

О соединены соответственно с информационньми входами блока регистрации, и индикации, установочный вход которого соединен с установонным входом первого регистра сдвига и является

5 установочным входом устройства, управляющий вход устройства соединен с запускающим входом блока управления, выход которого соединен с управляющим входом генератора тестов, выход

0 сумматора соединен с информационным входом регистра сдвига, выход последнего разряда которого соединен с первым входом сумматора, группа выходов регистра сдвига соединена соответственно с входами первого дешифратора и второго дешифратора, выход которого соединен с входом блока индикации, отличающееся тем, что, с целью повышения достоверности .

0 контроля, в устройство введены второй регистр сдвига и блок формирования синхросигналов, причем выход блока управления соединен с входом блока формирования синхросигналов, первый

выход которого соединен с синхровходом второго регистра сдвига, управляющий вход которого соединен с вторым выходом блока формирования синхросигналов и с управляющим входом первого регистра сдвига, второй вход сумматора, соединен с выходом последнего . разряда второго регистра сдвига, информационные входы которого соединены с выходами эталонного узла, установрчный вход первого регистра соединен с установочным входом второго регистра сдвига.

Авторы

Даты

1982-03-07—Публикация

1980-06-27—Подача