вестном устройстве нет связи выходов элементов однотактной задержки со входами дешифраторов одиночной неисправности и исправности. При малой длине теста это может привести к дополнительному снижению достоверности проверок.

Целью изобретения является повышение достоверности работы устройст1ва. В описываемом устройстве это достигается тем, что в пем входы сумматора подключены к соответствующим выходам проверяемого блока, выходы- к соответствующим входам дешифраторов одиночной неисправности и исправности. Это .позволяет регистрировать искажение выходных кодов проверяемого блока, причем накапливающий сумматор регистрирует сумму параллельных кодов (строк), а сумматор и регистр сдвига - сумму последовательных кодов (столбцов), независящую от длины накапливающего сумматора, причем дешифраторы одинОЧ«ой неисправности и исправности уч1итывают информацию, хранящуюся в элементах одпотажтйой задержки сумматора.

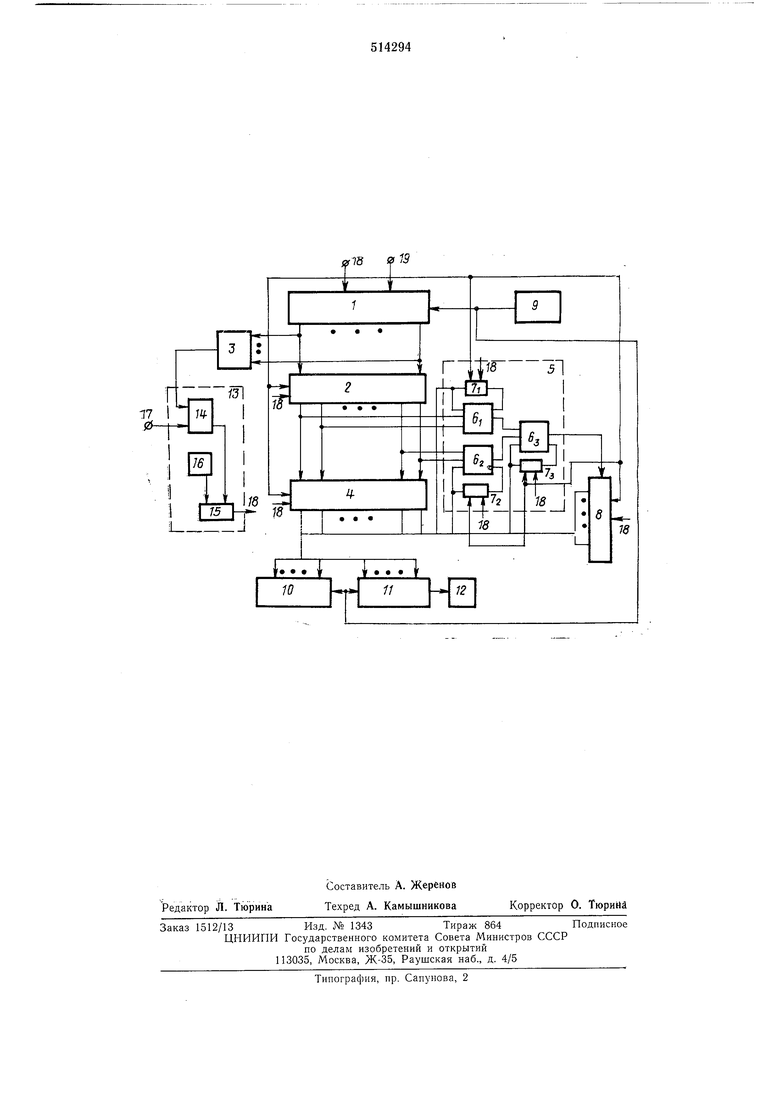

На чертеже приведена схема описываемого устройства.

Генератор 1 тестов подключен своими выходами к проверяемому блоку 2 и к дешифратору 3 окончания .проверки. Проверяемый блок 2 всеми своими выходами соединен со входами накапливающего сумматора 4 параллельного типа и со входами сумматора 5, содержащего каскады комбинационных сумматоров 6i-63, причем выходы суммы комбинационных сумматоров предыдущих каскадов связаны со входами комбинационных сумматоро-в последующих каскадов, а выходы переносов комбинационных сумматоров 6i-63 через элементы задержки 7i-7з подключены ко входам этих же сумматоров 6i-63. Выход сумматора 5 подключен ко входу младшего разряда регистра 8 сдвига. Блок 9 ввода перестраивает генератор 1 тестов, дешифратор 10 одиночных неисправностей и дешифратор И исправности настроены на проверку блоков определенного типа. Выход дешифратора исправности подключен к индикатору 12. Формирователь 13 Импульсных сигналов содержит триггер 14, элемент «И 15 и мультивибратор 16. Запуск формирователя 13 производится через управляющий вход 17. Выход 18 импульсных сигналов подключен к первым входам генератора 1 тестов, проверяемого блока 2, накапливающего сумматора 4, регистра 8 сдвига, элементов 7i-7з задержки. Вход 19 установки производит первоначальную установку всех узлов устройства.

При поступлении сигнала .на вход 19 устаНОВ.КИ производится начальная установка всех узлов устройства, имеющих элементы памяти (например, триггеры).. При поступлении сигнала на управляющий вход 17 формирователя 13 триггер 14 перебрасывается в состояние «1, при этом открывается элемент «И 15, и тактовые импульсы с выхода мультивибратора 16 через элемент «И 15 поступают

на выход 18 формирователя импульсных сигналов 13, генератор 1 тестов начинает выдавать ко всем своим выходам импульсные последовательности, проверяющие блок 2. Выходные коды проверяемого блока 2 суммируются и хранятся в накапливающем сумматоре 4 параллельного типа, а последовательные коды выходов проверяемого блока 2 суммируются в каскадах комбинационных сумматоров 6i-63 и поступают на вход регистра сдвига 8, при этом переносы последовательного суммирования осуществляются с помощью элементов 7i-7з однотакт1ной задержки. Процесс генерации тестов и работы всего устройства продолжается до появления на выходах генератора 1 тестов комбинации, означающей окончание цикла проверки. Пр.и этом срабатывает дешифратор 3, появляюшийся на его выходе сигнал устанавливает триггер 14

в «нулевое состояние, элемент «И 15 закрывается и поступление тактовых импульсов с выхода 18 прекращается.

В пакаплнвающем сумматоре 4 хранится итоговая сумма выходных кодов (строк) проверяемого блока 2, в регистре 8 хранится итоговая сумма последовательных кодов (столбцов), а элементы аднотактной задержки содержат «единицы переполнения от сумм.ирования столбцов. Эти суммы и переполнения определяют состояние проверяемого блока 2. Дешифратор 11 исправности и индикатор 12 срабатывают при истинном значении сумм и переполнений, а дешифратор 10 одиночных неисправностей перекодирует суммы и переполнения (в случае их искажений) в позиции пепсправных элементов.

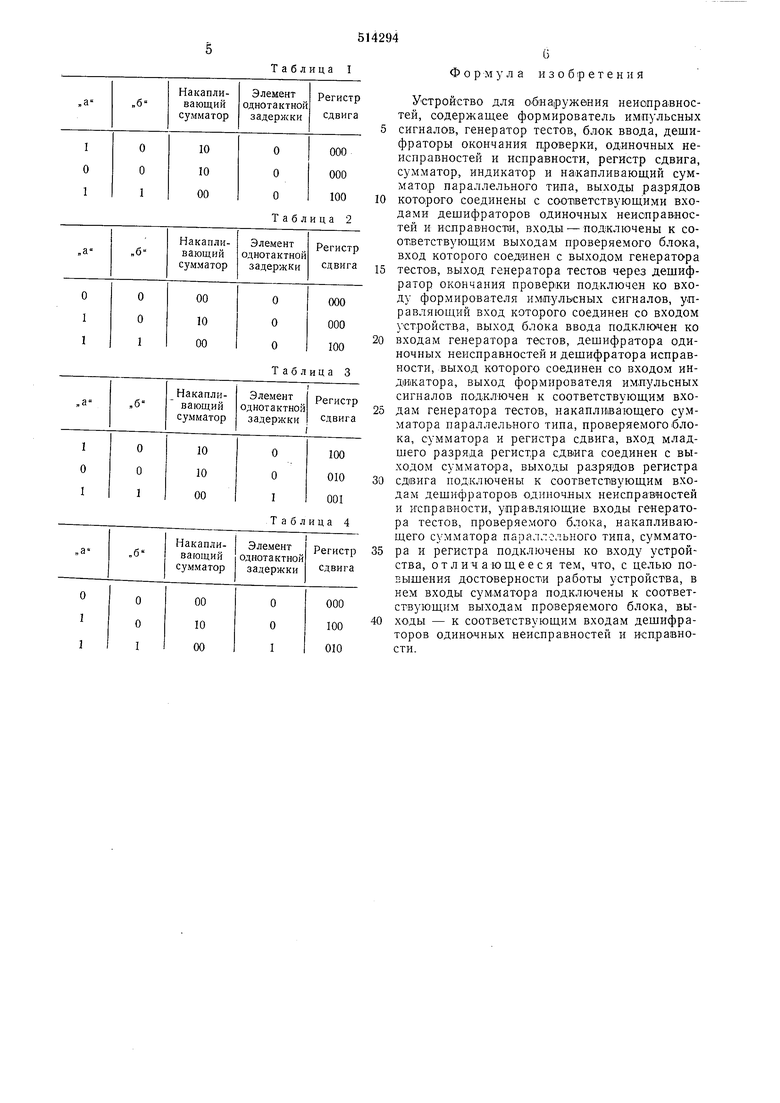

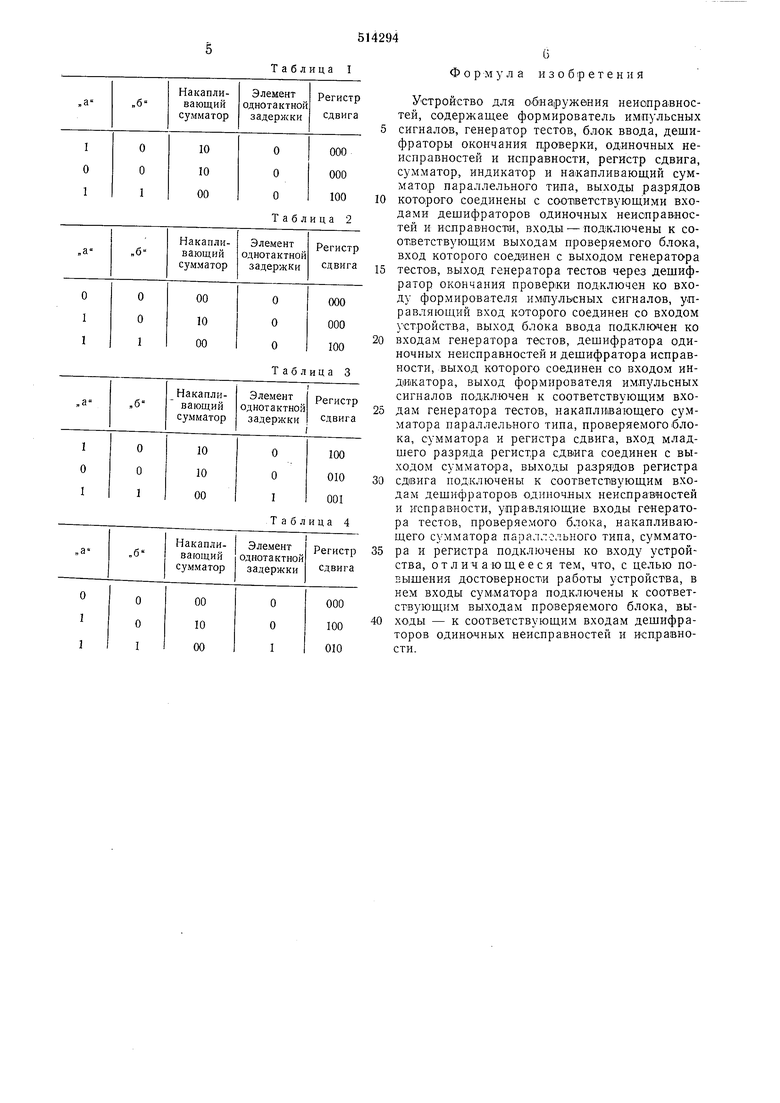

Сущность изобретения можно пояснить простейщим примером. Полагаем проверяемый блок имеет два выхода «а и «б. В. таблице 1 приведены примерные выходные коды и переполнение исправного проверяемого блока, а также показаны состояния накапливающего сумматора, элемента одотактной задержки и генератора сдвига в случае регистрации сумматором 5 и регистром 8 переноса со старшего разряда накапливающего сумматора так, ка.к это производится в известном устррйстве. В таблице 2 дано искажение кода на выходе «а, вызванное какой-то неисправностью. Как

видно из табл. 2, это не приводит ни к какому изменению кодов в узлах регистрации. В таблице 3 показаны состояния сумматора, элемента однотактной задержки и регистра сдвига в случае подключения дополнительного сумматора к выходам проверяемого блока при условии отсутствия искажения в проверяемом блоке, а в таблице 4 - ори наличии искажения аналогичного табл. 2. Как видно из табл. 3 и 4 в конце цикла проверки оказывается измененным, .по сравнению с истинным, только состояние регистра сдвига, поэтому в данном случае только регистр сдвига, подключенный через дополнительный сумматор прямо к выходам проверяемого блока, способен обнаружить неисправности.

Таблица I

G Формула изобретения

Устройство для Об на1ружения неисправностей, содержащее формирователь импульсных сигналов, генератор тестов, блок ввода, дешифраторы окончания проверки, одиночных неисправностей и исправности, регистр сдвига, сумматор, индикатор и на.капливающий сумматор параллельного типа, выходы разрядов

которого соединены с соответствующими входами дешифраторов одиночных неиоправяостей и исправности, входы - подключены к соответствующим выходам проверяемого блока, вход которого соединен с выходом генератора

тестОВ, выход генератора тестов через дешифратор окончания проверки подключен ко входу формирователя импульсных сигналов, управляющий вход которого соединен со входом устройства, выход блока ввода подклю чен ко

входам генератора тестов, дешифратора одиночных неисправностей и дешифратора исправности, выход которого соединен со входом индикатора, выход формирователя импульсных сигналов пОДключен к соответствующим входам генератора тестов, накапливающего сумматора параллельного типа, проверяемого блока, сумматора и регистра сдвига, вход младшего разряда регистра сдвига соединен с выходом сумматора, выходы разрядов регистра

сдвига подключены к соответствующим входам дешифраторов одиночных неисправностей и исправности, управляющие входы генератора тестов, проверяемого блока, накапливающего сумматора параллельного типа, сумматора и регистра подключены ко входу устройства, отличающееся тем, что, с целью повышения достоверности работы устройства, в нем входы сумматора подключены к соответствующим выходам проверяемого блока, выходы - к соответствующим входам дешифраторов одиночных неисправностей и исправности.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения неисправностей | 1973 |

|

SU478309A1 |

| Устройство для контроля логических блоков | 1975 |

|

SU558266A1 |

| Тренажер оператора радиоэлектронной аппаратуры | 1989 |

|

SU1658193A1 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU868843A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1278854A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1589280A2 |

| Устройство для нахождения кратных неисправностей в схемах цвм | 1974 |

|

SU533894A1 |

| Генератор тестовой псевдослучайной двоичной последовательности | 1987 |

|

SU1640699A1 |

| Устройство для контроля цифровых узлов | 1980 |

|

SU911532A1 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

Авторы

Даты

1976-05-15—Публикация

1974-09-06—Подача