Изобретение относится к вычислительной технике и может быть использовано для контроля- блоков памяти.

Цель изобретения - повышение достоверности контроля.

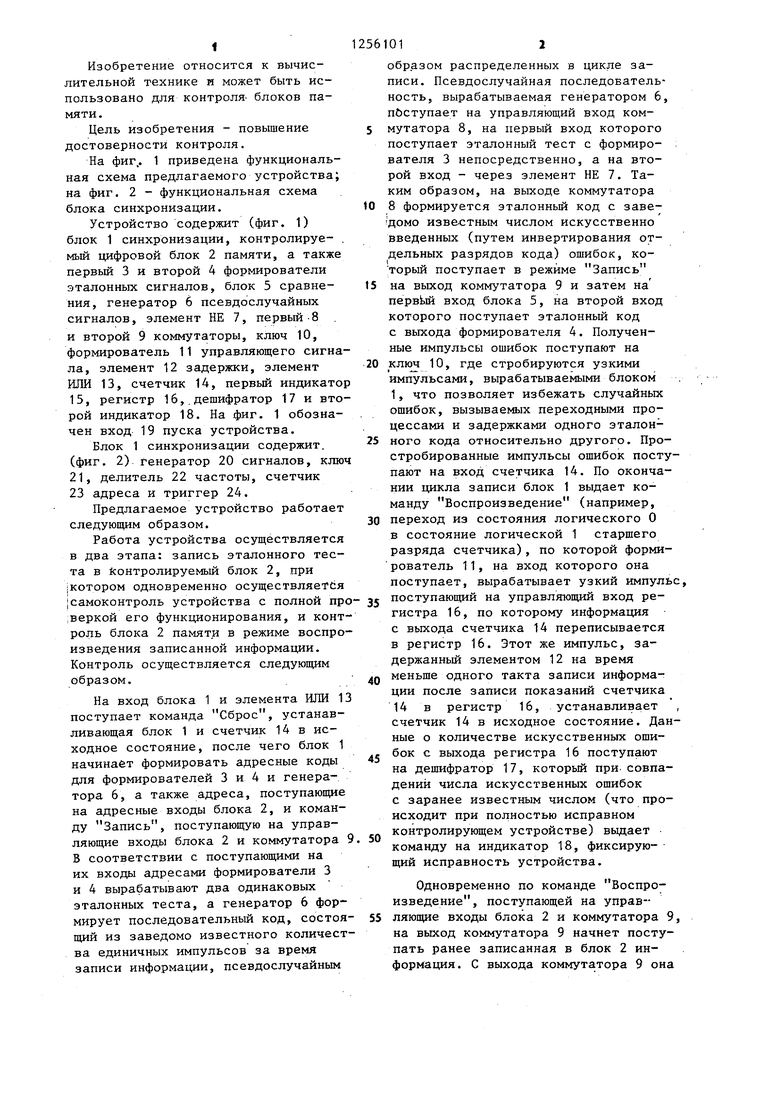

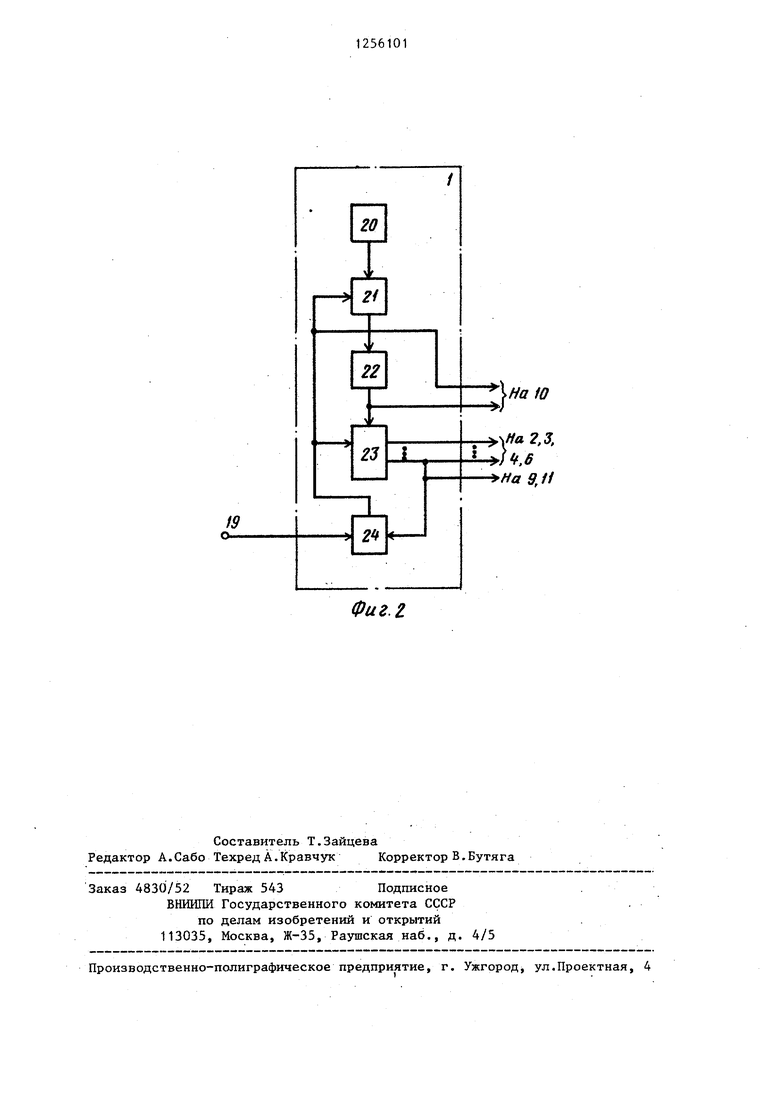

На фиг.. 1 приведена функциональная схема предлагаемого устройства; на фиг. 2 - функциональная схема блока синхронизации.

Устройство содержит (фиг. 1) блок 1 синхронизации, контролируе- . мый цифровой блок 2 памяти, а также первый 3 и второй 4 формирователи эталонных сигналов, блок 5 сравнения, генератор 6 псевдослучайных сигналов, элемент НЕ 7, первый-8 и второй 9 коммутаторы, ключ 10, формирователь 11 управляющего сигнала, элемент 12 задержки, элемент ИЛИ 13, счетчик 14, первый индикатор 15, регистр 16,.дешифратор 17 и второй индикатор 18. На фиг. 1 обозначен вход 19 пуска устройства.

Блок 1 синхронизации содержит, (фиг. 2) Генератор 20 сигналов, ключ 21, делитель 22 частоты, счетчик 23 адреса и триггер 24.

Предлагаемое устройство работает следующим образом.

Работа устройства осуществляется в два этапа: запись эталонного геста в Контролируемый блок 2, при jKOTOpOM одновременно осуществляется I самоконтроль устройства с полной проверкой его функционирования, и контроль блока 2 памяти в режиме воспроизведения записанной информации. Контроль осуществляется следующим образом.

На вход блока 1 и элемента ИЛИ 13 поступает команда Сброс, устанавливающая блок 1 и счетчик 14 в исходное состояние, после чего блок 1 начинает формировать адресные коды для формирователей 3 и 4 и генератора 6, а также адреса, поступающие на адресные входы блока 2, и команду Запись, поступающую на управляющие входы блока 2 и коммутатора 9 В соответствии с поступающими на их входы адресами формирователи 3 и 4 вырабатывают два одинаковых эталонных теста, а генератор 6 формирует последовательный код, состоящий из заведомо известного количества единичных импульсов за время записи информации, псевдослучайным

561012

образом распределенных в цикле записи. Псевдослучайная последовательность, вырабатываемая генератором 6, пЬступает на управляющий вход ком5 мутатора 8, на первый вход которого поступает эталонный тест с формиро- : вателя 3 непосредственно, а на второй вход - через элемент НЕ 7. Таким образом, на выходе коммутатора

0 8 формируется эталонный код с заве- домо известным числом искусственно введенных (путем инвертирования отдельных разрядов кода) ошибок, ко- торый поступает в режиме Запись

5 на выход коммутатора 9 и затем на первой вход блока 5, на второй вход которого поступает эталонный код с выхода формирователя 4. Полученные импульсы ошибок поступают на

20 ключ 10, где стробируются узкими

импульсами, вырабатываемыми блоком . 1, что позволяет избежать случайных ошибок, вызываемых переходными процессами и задержками одного эталон25 ного кода относительно другого. Про- стробированные импульсы ошибок поступают на вход счетчика 14. По окончании цикла записи блок 1 выдает команду Воспроизведение (например,

30 переход из состояния логического О в состояние логической 1 старшего разряда счетчика), по которой формирователь 11, на вход которого она поступает, вырабатывает узкий импульс,

r поступающий на управляющий вход регистра 16, по которому информация с выхода счетчика 14 переписывается в регистр 16. Этот же импульс, задержанный элементом 12 на время

Q меньше одного такта записи информации после записи показаний счетчика 14 в регистр 16, устанавливает , счетчик 14 в исходное состояние. Данные о количестве искусственных оши, бок с выхода регистра 16 поступают на дешифратор 17, который при совпадений числа искусственных ошибок с заранее известным числом (что происходит при полностью исправном контролирующем устройстве) вьщает команду на индикатор 18, фиксирующий исправность устройства.

50

Одновременно по команде Воспроизведение, поступающей на управ- ляющие входы блока 2 и коммутатора 9, на выход коммутатора 9 начнет поступать ранее записанная в блок 2 информация. С выхода коммутатора 9 она

31

поступает на первый вход блока 5, на второй вход которого поступает эталонный код с выхода формирователя 4. В случае неисправности какого- либо числа ячеек памяти в блоке 2 блок 5 формирует импульсы несовпадения, которые стробируются на ключе 10 узкими импульсами, поступающими с блока 1, затем подсчитываются счетчиком 14. Суммарное число опта- бок, соответствующее числу неисправных ячеек памяти блока 2, отображается на индикаторе 15. По окончании цикла Воспроизведение (после прохождения конечного адреса) блок 1 переходит в исходное состояние - первый адрес цикла Запись, Повторный запуск устройства осуществляется при поступлении новой команды Сброс

Формула изобретения

Устройство для контроля цифровых блоков памяти, содержащее первый формирователь эталонных сигналов, блок сравнения, индикаторы и блок синхронизации, выходы первой группы которого подключены к входам первого формирователя эталонных сигна- |лов, выход которого является конт- рольным выходом устройства, адресны- .ми выходами которого являются выходы ;первой группы блока синхронизации, отличающееся тем, что, с целью повышения достоверности контроля, в него введены второй фор- мирователь эталонных сигналов, генератор псевдослучайных сигналов, коммутаторы, формирователь управляющего сигнала, счетчик, регистр.

s 5

0

5

.0

1014

дешифратор, элемент НЕ, ключ, элемент задержки и элемент ИЛИ, причем входы генератора псевдослучайных сигналов и второго формирователя эталонных сигналов подключены к выходам первой группы блока синхронизации, а выходы - соответственно к управляющему входу первого коммутатора и первому входу блока сравнения, второй вход и выход которого соединены соответственно с выходом второго коммутатора и входом ключа, управляющие входы которого подключе- ны к выходам второй группы блока синхронизации, выход которого соединен с управляющим входом второго коммутатора и входом формирователя управляющего сигнала, выход которого подключен к тактовому входу регистра и входу элемента задержки, выход которого соединен с первым входом элемента ИЛИ, выход которого подключен к установочному входу счетчика, счетный вход которого соединен с выходом ключа, а выходы подключены к входам первого индикатора-и регистра, выходы которого соединены с входами дешифратора, выход которого подключен к входу второго индикатора, первый вход первого коммутатора соединен с выходом элемента НЕ, вход которого подключен к выходу первого формирователя эталонных сигналов и второму, входу первого коммутатора, выход которого соединен с первым входом второго коммутатора, второй вход которого является информационным входом устройства, входом пус. ка которого являются вход блока синхронизации ивторой вход элемента ИЛИ.

HaW

7- Х у«гз:

I f.B На 9,11

Фиг. г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков памяти | 1984 |

|

SU1215136A1 |

| Устройство для контроля блоков памяти | 1984 |

|

SU1226533A1 |

| Устройство для контроля памяти | 1987 |

|

SU1587598A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

| Устройство контроля ошибок многоканальной аппаратуры магнитной записи | 1987 |

|

SU1529285A1 |

| Устройство для контроля программных автоматов | 1988 |

|

SU1571552A1 |

| Устройство для контроля многоканального аппарата магнитной записи | 1987 |

|

SU1432602A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство для контроля каналов записи аппарата магнитной записи | 1986 |

|

SU1411818A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля блоков памяти. Целью изобретения является повышение достоверности контроля. Устройство содержит блок синхронизации, первый формирователь эталонных сигналов, блок сравнения, индикаторы. Новыми элементами являются генератор псевдослучайных сигналов, второй формирователь эталонных си1- налов, два коммутатора, счетчик, регистр, дешифратор, формирователь управляющего сигнала, ключ, элемент ИЛИ, элемент НЕ и элемент задержки. Контроль блока памяти выполняется путем записи в него эталонного ко да и последующего сравнения считанной информации с .эталонной. Достоверность контроля повышается благодаря самоконтролю устройства, для чего в нем формируется из эталонного кода всевдослучайная последовательность сигналов с известным числом искусственно введенных ошибок, число которых после прохождения через блоки устройства сравнивается с заранее известным числом ошибок причем совпадение их соответствует . исправности устройства. 2 ил. I (Л to ел О5

| Устройство для контроля блоков оперативной памяти | 1979 |

|

SU888211A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля блоков памяти | 1980 |

|

SU926725A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-09-07—Публикация

1985-03-22—Подача