изобретение О2носи сй к вапома« нающим устройсЕвам,

Извесгны ассоциа ивше закода нающиб элементы на МОП 1ранзис10,рах, содержащие триггер, логйчеекую схему Неравнозначвос1ь г состоящую из гранзйсгоров, сгоки которых подключены к соотве5С5вущий плечам триггера, затворы - к раз рядныы шинам, а истоки - к стоку

ключевого транзистора, управляю-.

щие транзисторы и числовун шину,

Однако в таких элементах дня получения выходного сигнала дря считывании и сравнении требуется изменение напряжения на плече триБ. гера, что может.привести к разрушению информации, кроме того, в . . известных элементах используются , дополнительные источники питания и .управляющие шинн

1 Цель изобретения - упрощение

{ассоциативного запоминающего злё мбнтаИ исключение возможнбсии разрушения информации при считывании и сравнении

Это достигается тем, что в эле1ганте аагворы управляющих транаист-оров подключены к соответствующим плечам триггера, истоки - к разрядным шинам, стоки - к числовой шина, подсоединенной к затвору ключевого транзистора, исток которого.подключен к общей ШИЕЭ элемента

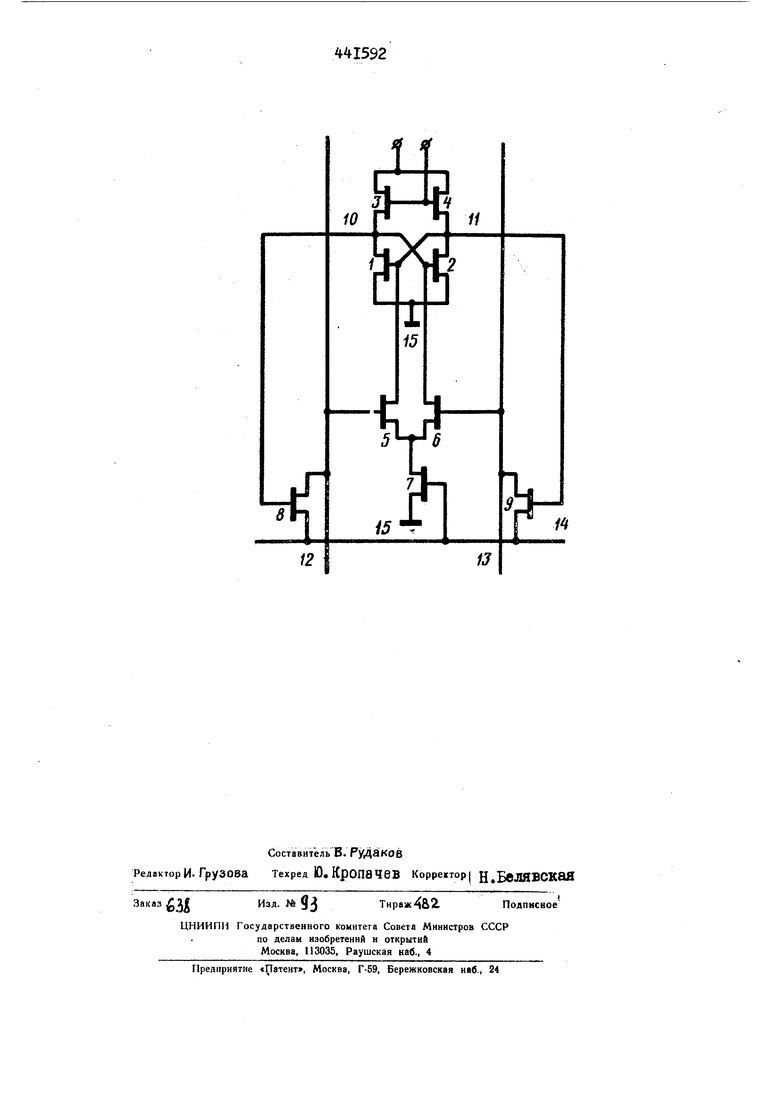

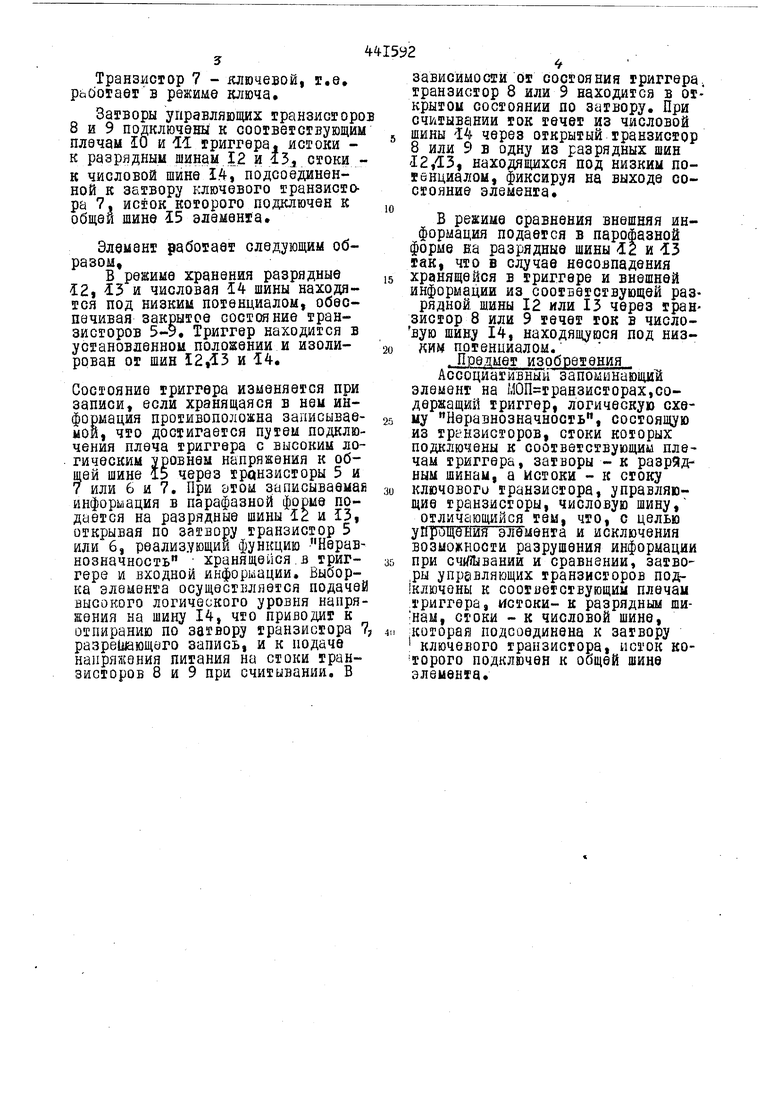

На чертеже показана схема ассог циативного запоминающего элемента.

Злбмент содергит активные 1,2 я нагрузочные 3,4 МОП гранзисторы, образующие статический триггер, гранзисторы 5, 7, реализующие логическую схему НеравнозначноCTb j управляюоще транзисторы 8 и Транзистор 7 - ялючевой, г.е pfadoiaei в режиме ключа Затворы управляющих транзисторо 8 и 9 подключены к соответствующим плечам Ю и -11 триггера, истоки к разрядным шинам 12 и 13., стоки к числовой шике IA-, подсоединенной к затвору ключевого транзистора 7. исток которого подключен к общей шине i5 элеменга. Элемент работает следующим образом, В режиме хранения разрядные 12, 13 и числовая 14 шины находятся под низким потенциалом, обеспечивая закрытое состшние транзисторов 5-9, Триггер находится в установленном положении и изолирован от шин I2,i3 и 14. Состояние триггера изменяется при записи, если хранящаяся в нем информация противоположна записываемои, что достигается путем подключения плеча триггера с высоким логическим уровнем напряжения к общей шине 15 через транзисторы 5 и 7 ИЛИ 6 И 7. При этом записываемая информация в парафазной форме подается на разрядные шины 12 и 13, открывая по затвору транзистор 5 или 6, реализ.ующии функцию Неравнозначность хранящейся.в триггере и входной информации. Выборка элемента осуществляется подачей высокого логического уровня напряжения на wi&KS 14, что приводит к отпиранию по затвору транзистора 7 разре1шющаго запись, и к подаче напряжения питания на стоки транзисторов 8 и 9 при считывании, В зависимости от состояния триггера транзистор 8 или 9 находится в открытом состоянии по затвору. При считывании ток течет из числовой шины 14 через открытый транзистор В или 9 в одну из разрядных шин 12,ЕЗ, находящихся под низким потенциалом, фиксируя на выходе состояние элемента. В режиме сравнения внешняя информация подается в парофазной форме на разрядные шины 2 и 13 так, что в случае несовпадения хранящейся в триггере и внешней информации из соответствующей разрядной шины 12 или 13 через транзистор 8 или 9 течет ток в числовую шину 14, находящуюся под низяим потенциалом. „Предмет изобретения Ассоциативный запоминающий злемент на М011 транзисторах,содержащий триггер, логическую схему Неравнозначность, состоящую из транзисторов, стоки которых подключены к соответствующим плечам триггера, затворы - к разрядным шинам, а истоки - к стоку ключевого транзистора, управляющие транзисторы, числовую шину, отличающ11йся тем, что, с целью упрощения элемента и исключения Бозмоксности разрушения информации при сч Швании и сравнении, затво,ры управляющих транзисторов под1КЛЮЧОНЫ к соответствующим плечам триггера, истоки- к разрядным шинам, стоки - к числовой шине, :Которай подсоединена к затвору ключевого транзистора, исток которого подключен к общей шина элзмaнfЁ|.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативный запоминающий элемент на мдп-транзисторах | 1980 |

|

SU868834A1 |

| Ассоциативный запоминающий элемент на моп-транзисторах | 1978 |

|

SU752480A1 |

| Усилитель считывания для матрицы однотранзисторных запоминающих элементов | 1976 |

|

SU661605A1 |

| Ассоциативный запоминающий элемент на мдп-транзисторах | 1977 |

|

SU708417A1 |

| Ячейка памяти | 1977 |

|

SU693437A1 |

| Ячейка памяти (ее варианты) | 1982 |

|

SU1115106A1 |

| ЯЧЕЙКА ПАМЯТИ ДЛЯ БЫСТРОДЕЙСТВУЮЩЕГО ЭСППЗУ С УПРАВЛЯЕМЫМ ПОТЕНЦИАЛОМ ПОДЗАТВОРНОЙ ОБЛАСТИ | 2011 |

|

RU2465659C1 |

| Усилитель считывания на моп-транзисторах /его варианты/ | 1980 |

|

SU883968A1 |

| Ассоциативный запоминающий элемент на моп транзисторах | 1974 |

|

SU527740A1 |

| Элемент памяти | 1990 |

|

SU1786508A1 |

Авторы

Даты

1974-08-30—Публикация

1972-10-13—Подача