1

Изобретение относится к области заполоогающих устройств к может быть использовано в памяти ЭВМ и н ассоциативных процессорах.

ИзвестШ) ассоциативные запоминающие элементы на МДП-транзисторах 1,2.

Один из известных элементов входит в состав устройства, ячейки которого обладают способностью маскирования как по словам, так и по .разрядам, и содержит ишны управления записью, считыванием и опросом 1. Недостатком этого элемента являются большие аппаратурные затраты.

Из известных ассоциативных запоминшощих элементов наиболее близким техническим решешем к данному изобретению является ассоциативный запоминающий элемент на МДПтранзисторах, содержащий запоминающие и нагрузочные транзисторы, соедкненные по схеме триггера,, шину сравнения, транзисторы опроса, транзисторы записи, истоки и загзоры одних из которых подключены соответственно к стокам запоминающих транзисторов и словарной шине, истоки и затворы других -к ишне нулевого потенциала и разря;шым шю1ам, а стоки

транзисторов записи соединены соответственно с затвора.ми транзисторов считывания и истоками ускоряющих транзисторов, затворы которых подключены к соответствующим разрядным шинам, стоки - к шине питания 2.

На основеэлементов, объединенных rio строкам словам и столбцам - разрядам с помоиЦ)Ю щин отправления создаются регулярные матрищь которые используются для построения ассоциативных запошшающих устройств и процессоров .

Недостаток этого элемента заключается в том, что при записи информации в матрицу невыбранные ячейки шунтируют управляющие шины и создают дополнительную наарузку по току на подключенные к этим шинам управляющие схемы, что приводит к увеличению потребляемой мощности.

В результате уменьшается скорость нарастания сигнала на управляющей шине, что снижает быстродействие ассоциативного эапоминаюпдего элемента.

370

Целью настоящего изобретения является повьгшение быстродействия элемента и снижения потребляемой им мощности.

Поставленная цель достигается тем, что а ассоциативном запоминающем элементе стоки транзисторов опроса подключены к стокам соответствутощих транзисторов записи, затворы к стокам соответствующих запоминазощих транзисторов, истоки - к шине сравнения, стоки транзисторов считывания соединеШ с шиной питания, а истоки - с соответствующими разрядными шинами.

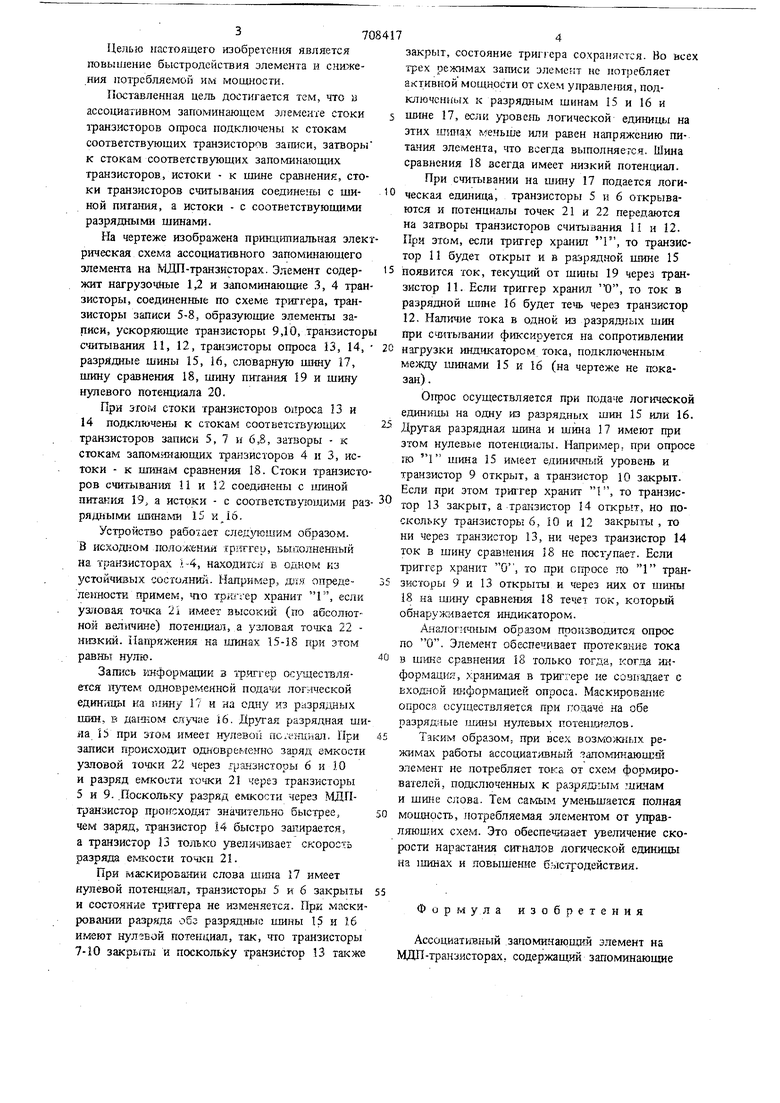

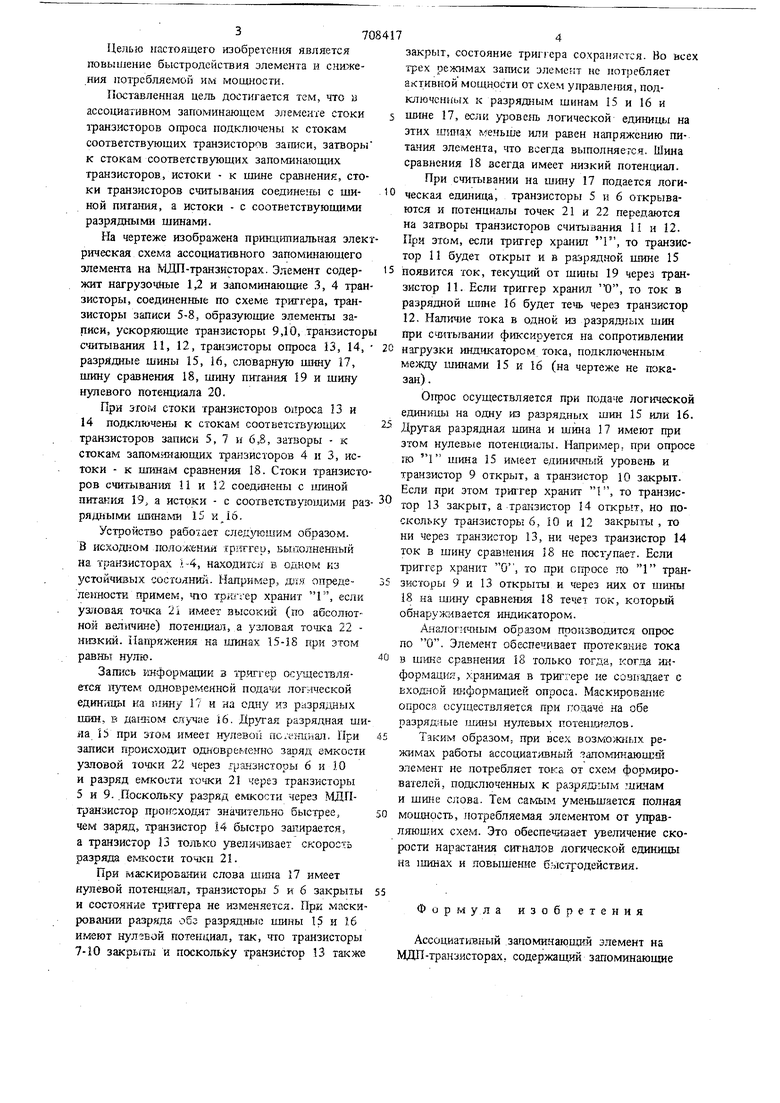

На чертеже изображена принципиальная элекхрическая схема ассоциативного запоминающего элемента на ЩП-транзисторах. Элемент содержиг нагрузочные 1Д и запоминающие 3, 4 транзисторы, соединенные по схеме триггера, транзисторы записи 5-8, образующие элементы записи, ускоряющие транзисторы 9,10, транзисторы считывания И, 12, транзисторы опроса 13, 14, разрядные шины 15, 16, словарную шину 17, шину сравнения 18, питания 19 и шину нулевого потенц Ш1а 20.

При этом стоки транзисторов опроса 13 и 14 подключены к стокам соответствующих

транзисторов записи 5, 7 и 6,8, затворы - к стокам запом1-шающих транзисторов 4 и 3, истоки - к шинам сравнения 18. Стоки транзисторов считыван «1 11 и 12 соединены с шиной питакия 19, я истоки - с соответствшоидими раз рядныр ш Ш1шами 15 .

Устройство работает следтешлм образом. В исходном положений триггер, выполненный на транзисторах 1-4, находится в едком из устойчивых состолний. Например, для определениостк примем, чю тршгер хранит 1, если узловая точка 21 имеет высокий (по абсолютной величине) потешдаал, а узловая точка 22 низкий. Напряжения на шинах 15-18 при этом равны нулю.

Запись ршформации з ipnrrep ос)тцесталяется 1тутем одновременной подачя логической единицы ка мину 17 и на одну из разрядаых шин, в случае 16. Другая разрядная шияа 15 при этом имеет нулево пс.енциал, При записи происходит одьовременно заряд емкости уповой точки 22 через гршзисторы б и 10 и разряд емкости точки 21 через транзисторы 5 и 9. .Поскольку разряд емкости через МДПгранзистор прог-гоходит значительно быстрее,

чем заряд, транзистор 14 быстро запирается, а транзистор 13 только увеличивает скорость разряда емкости точки 21.

При маскировании слова шина 17 имеет нулевой потендиал, транзисторы 5 и б закрыты и состояние триггера не изменяется. При маскировании разряда об; разр.ядныс шины 15 и 16 имеют нулевой потендиал, так, что транзисторы 7-10 закрытьг и поскольку транзистор 13 также

закрыт, состояние триггера сохраняется. Во все трех режимах записи :)лемент не потребляет активной мощности от схем управлеюш, подютючснных к разрядным шинам 15 и 16 и пише 17, если уровегп. логической единицы на этих fe.чьшe или равен напряжению питания элемента, что всегда выполняется. Шина сравнения 18 всегда имеет низкий потенциал.

При считывании на шшу 17 подается логическая единица, транзисторы 5 и б открываются и потенциалы точек 21 и 22 передаются на затворы транзисторов считывания II и 12. При этом, если триггер хранил 1, то транзистор 11 будет открыт и в разрядной шине 15 появится ток, текущий от шины 19 через транзистор 11. Если триггер хранил О, то ток в разрядной unme 16 будет течь через транзистор 12. Наличие тока в одной из разрядных шин При счонтывании фиксируется на сопротивлении нагрузки индикатором тока, подключенным между шинами 15 и 16 (на чертеже не показан).

Опрос осуществляется при подаче логической единицы на одну из разрядных шин 15 или 16 Другая разрядная шина и шина 17 имеют при этом нулевые потенциалы. Например, при опрос гю 1 шина 15 имеет ед1-шичный уровень и транзистор 9 открыт, а транзистор Ю закрыт. Если при этом триггер хранит 1, то транзистор 13 закрыт, а транзистор 14 открыт, но поскольку транзисторы 6, 10 и 12 закрыты , то ни через транзистор 13, ни через транзистор 14 ток в шину сравнения 18 не поступает. Если триггер хранит О, то при спросе по 1 транзисторы 9 и 13 открыты и через них от шины 18 на шину сравнения 18 течет ток, который обнаруживается индикатором.

Аналогичным образом производится опрос по О. Элемент обеспечивает протекэлие тока в шине сравнения 18 только тогда, когда информация, хранимая в триггере не созг адает с входной информацией опроса. Маскирование опроса осуществляется при подаче на обе разрядные ишны нулевых потен1гиэлов.

Таким образом, при всех возможных режимах работы ассоциатявный запоминаюшш элемент не потребляет тока от схем формирователей, подключенных к разркд} ым шинам и шине слова. Тем самым уменьшается полная мощность, лотребляемая элементом от управляюш.их схем. Это обеспечивает уве;гачение скорости нарастания сигналов логической единицы на шинах и повышение б-жтродейсгвия.

Формула изобретения

Ассоциатшный .запоминающий элемент на МДП-транзисторах, содержащий запоминающие 5708 и нагрузочнь е 1ранзисторы, соединенные по схеме триггера, шш1у сравнения, транзисторы опроса, транзисторы записи, истоки и затворы одних из которых подключены соответственно к стокам запоминающих транзисторов и словар ной шине, истоки и затворы других к шине нулевого потенциала и разрядным шинам, а стоки транзисторов записи соединены соответственно с затворами транзисторов считывания и истоками ускоряюшях транзисторов, затворы ко торых подключены к соответствуюшим разрядным шинам, стоки - к шине питания, о тличающийся тем, что, с целью повышения быстродействия элемента и снижения потребляемой им мощности, в нем стоки тран зисторов опроса подключены к стокам соответствующих транзисторов записи, затворы - к стокам соответствующих запоминающих транзисторов, истоки к шине сравнения, стоки транзисторов сч1ггыван}ш соединены с шиной питания, а истоки - с соответствующими разрядными шинами. Источники информации, принятые во внимание при экспертизе 1.Прангкщвили И. В. и др. Однородные микроэлектронные ассоциативные процессоры. Сов.радио, М., 1973, с. 25-51. 2,Electronics Letters, том. 8, 15,. 1972, с. 391-393 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Элемент памяти для ассоциативного накопителя | 1976 |

|

SU690565A1 |

| Полупроводниковая ячейка памяти | 1976 |

|

SU723680A1 |

| Ассоциативный запоминающийэлЕМЕНТ | 1979 |

|

SU805412A1 |

| Усилитель считывания с регенерациейНА Мдп-ТРАНзиСТОРАХ | 1979 |

|

SU830575A1 |

| Ассоциативный запоминающий элемент | 1978 |

|

SU675452A1 |

| ЯЧЕЙКА ПАМЯТИ АССОЦИАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2008 |

|

RU2390860C1 |

| Ассоциативный запоминающий элемент на мдп-транзисторах | 1980 |

|

SU868834A1 |

| АССОЦИАТИВНЫЙ ЭЛЕМЕНТ ПАМЯТИ | 1991 |

|

RU2006964C1 |

| ЯЧЕЙКА ПАМЯТИ НА ТРАНЗИСТОРАХ СО СТРУКТУРОЙ МЕТАЛЛ-ДИЭЛЕКТРИК-ПОЛУПРОВОДНИК12 | 1972 |

|

SU330490A1 |

| Элемент памяти | 1979 |

|

SU788175A1 |

Авторы

Даты

1980-01-05—Публикация

1977-07-26—Подача