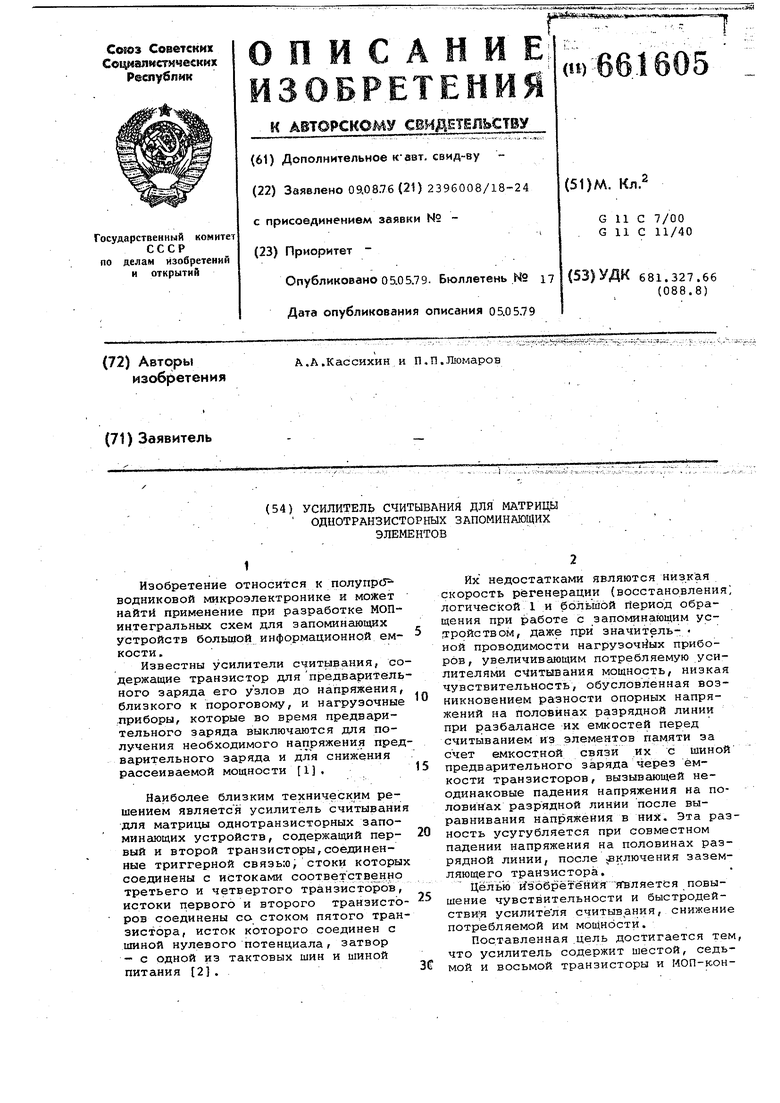

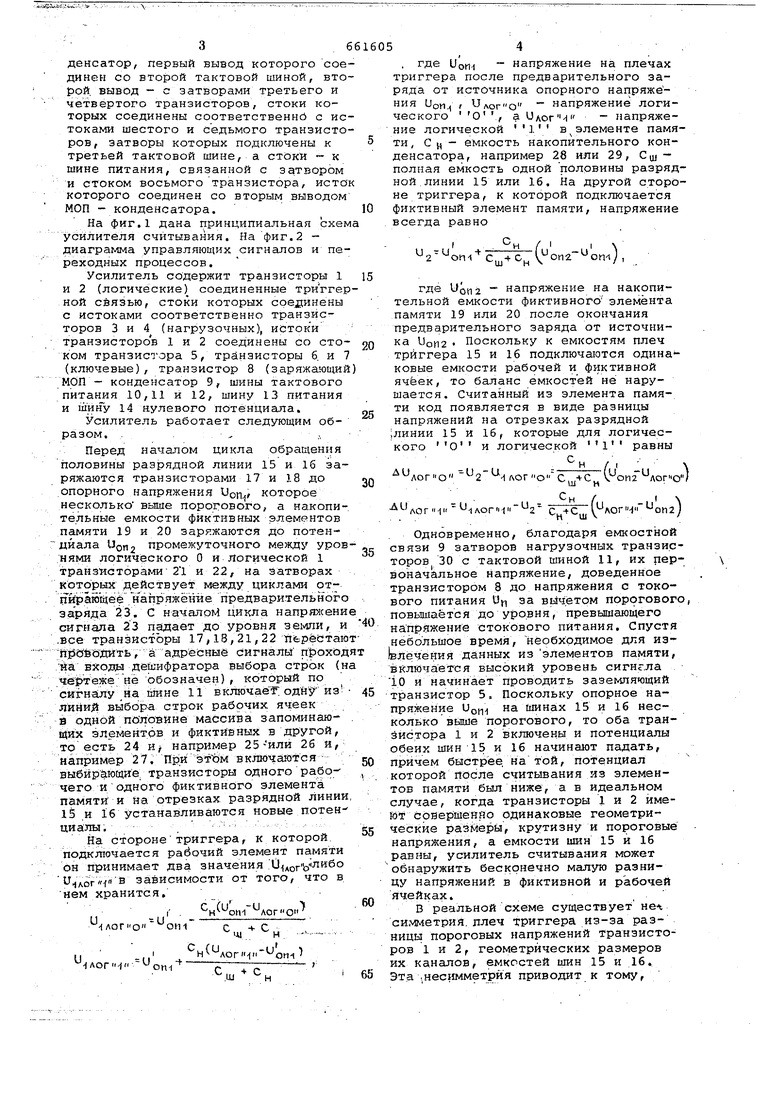

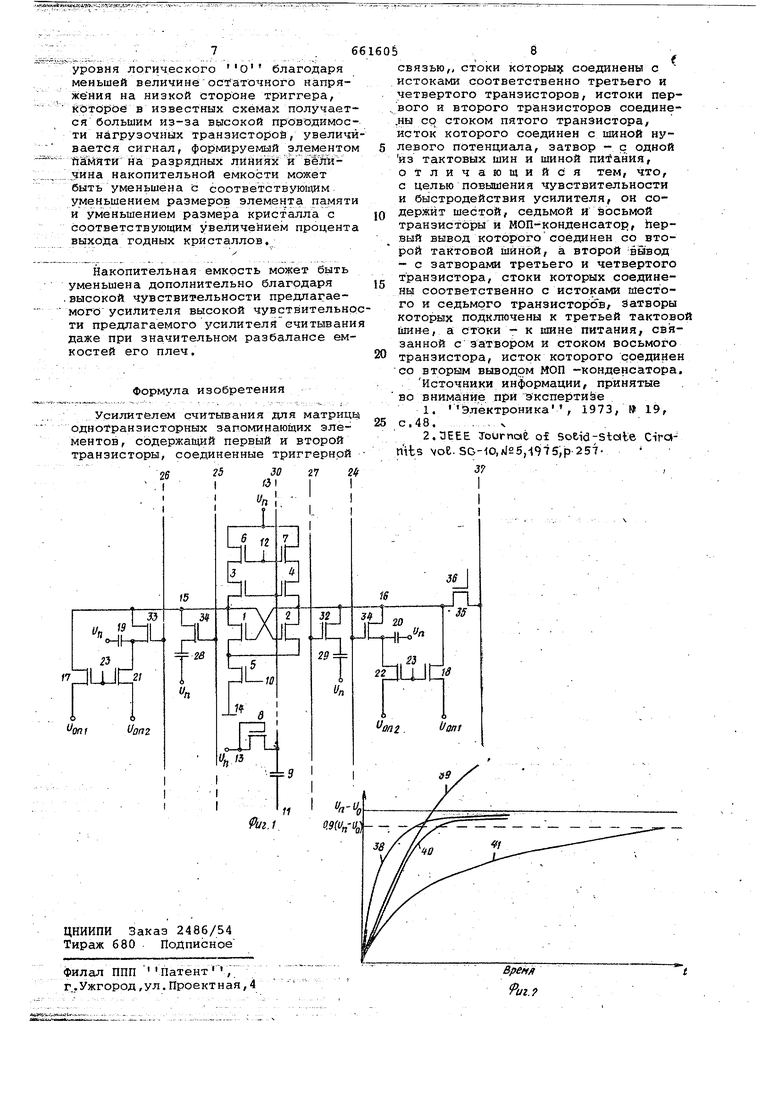

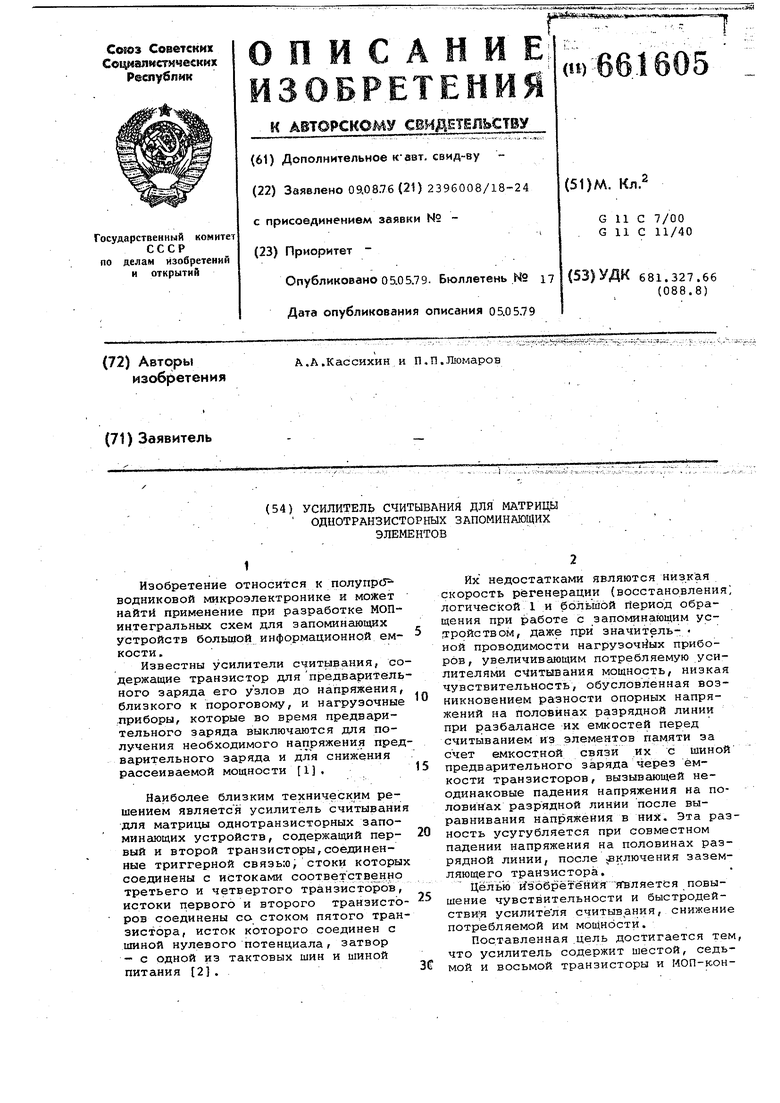

Изобретение относится к полупрс5 водниковой микроэлектронике и может найти применение при разработке МОПинтегральных схем для запоминающих устройств большой информационной емкости. Известны усилители считывания, со держащие транзистор для предваритель ного заряда его узлов до напряжения, близкого к пороговому, и нагрузочные .приборы, которые во время предварительного заряда выключаются для получения необходимого напряжения пред варительного заряда и для снижения рассеиваемой мощности 1, Наиболее близким техническим решением является усилитель считывания для матрицы однотранзисторных запоминающих устройств, содержащий первый и второй транзисторы,соединенные триггерной связью, стоки которых соединены с истоками соответственно третьего и четвертого транзисторов, истоки первого и второго транзисторов соединены со. стоком пятого транзистора, исток которого соединен с шиной нулевого потенциала, затвор - с одной из тактовых шин и шиной питания 2. Их недостатками являются низкая скорость регенерации {восстановления, логической 1 и большой Период обращения при работе с запоминающим усггройством, даже при значительной проводимости нагрузочных приборов, увеличивающим потребляемую усилителями считывания мощность, низкая чувствительность, обусловленная возникновением разности опорных напряжений на половинах разрядной линии при разбалансе их емкостей перед считыванием из элементов памяти за счет емкостной связи их с шиной предварительного заряда через ёмкости транзисторов, вызывающей неодинаковые падения напряжения на половин ах разрядной линии после выравнивания напряжения в них. Эта разность усугубляется при совместном падении напряжения на половинах разрядной линии, после -включения заземляющего транзистора. Целью йзобрётё нйя ягвляется повышение чувствительности и быстродействи;я усилителя считывания, снижение потребляемой им мощности. Поставленная .цель достигается тем, что усилитель содержит шестой, седьмой и восьмой транзисторы и МОП-конденсатор, первый вывод которого сое динен со второй тактовой шиной, вто рой, вывод - с затворами третьего и четвертого транзисторов, стоки которых соединены соответственнб с ис токами шестого и седьмого транзисто ров, затворы которых подключены к третьей тактовой шине, а стоки к шине питания, связанной с затвором и стоком восьмого транзистора, исто которого соединен со вторым выводом МОП - конденсатора. На фиг.1 дана принципиальная схем усилителя считывания. На фиг.2 - диаграмма управляющих сигналов и переходных процессов. Усилитель содержит транзисторы 1 и 2 (логические) соединенные триггер ной связью, стоки которых соединены с истоками соответственно транзисторов 3 и 4 (нагрузочных), истоки транзисторов 1 и 2 соединены со стоком транзистора 5, трйнзисторы 6. и 7 (ключевые), транзистор 8 (заряжающий МОП - конденсатор 9, шины тактового питан ия 10,11 и 12, шину 13 питания и шину 14 нулевого потенциала. Усилитель работает следующим образом, , . . Перед началом цикла обращения половины разрядной линии 15 и 16 заряжаются транзисторами 17 и 18 до опорного напряжения Don,, которое несколько выше порогового, а накопительные емкости фиктивных элементов памяти 19 и 20 заряжаются до потенцйала Uonj промежуточного между уров нями логического О и логической 1 транзисторами 21 и 22, на затворах которых действует ькжду циклами отпйрагойеё напряжение предварительного заряда 23. С началом цикла напршсени сигнала 23 падает до уровня звмлк, и .все транзисторы 17,18,21,22 перестаю П|5Ш&дйть, а адресные сигналы проход ,;йа входы дешифратора выбора строк (н чертвженё обозначен) , который по сигналу на шине 11 включает одйГ из лйни-й выбора строк рабочих ячеек в одной половйне массива запоминаю14ИХ элементов и фиктивных в другой, то есть 24 и например 25-или 26 и, например 27. ПриэтШ включаются- : выбйрающие. транзисторы одного рабочего иодного фиктивного элемента памяти и на отрезках разрядной линии 15 и 16 устанавливаются новые потенциалы. , на сторонетриггера, к которой подключается рабочий элемент памяти он принимает два значения . и дог-fB зависимости от того, что в. нем хранится, - dAOriO от - н илогчм- лoгЧ . , где УОИ-) напряжение на плечах триггера после предварительного заряда от источника опорного напряжения UQY. г напряжение логического О, а и лог41 - напряжение логической в элементе памяти, Сн - емкость накопительного конденсатора, например 28 или 29, Сщ полная емкость одной половины разрядной линии 15 или 16. На другой стороне триггера, к которой подключается фиктивный элемент памяти, напряжение всегда равно ( , ОЛ2 On-l где Uon2 напряжение на накопительной емкости фиктивного элемента памяти 19 или 20 после окончания предварительного заряда от источника 1)оп2 Поскольку к емкостям плеч триггера 15 и 16 подключаются одинаковые емкости рабочей и фиктивной ячеек, то баланс емкостей не нарушается. Считанный из элемента памяти код появляется в виде разницы напряжений на отрезках разрядной ;линии 15 и 16f которые для логического О и логической равны 1 лог О Одновременно, благодаря емкостной связи 9 затворов нагрузочных транзисторов 30 с тактовой шиной 11, их первоначальное Напряжение, доведенное транзистором 8 до напряжения с токового питания Ufi за вычетом порогового, повышается до уровня, превышающего напряжение стокового питания. Спустя небольшое время, Необходимое для извлечения данных из элементов памяти, йключается высокий уровень сигнгла , 10 и начинает проводить заземляющий транзистор 5, Поскольку опорное напряжение VQ на шинах 15 и 16 несколько выше порогового, то оба транзистора 1 и 2 включены и потенциалы обеих шин 15 и 16 начинают падать, причем быстрее, на той, потенциал которой после считывания из элементов памяти был ниже, а в идеальном случае, когда транзисторы 1 и 2 имеют совершеняо одинаковые геометрические размеры, крутизну и пороговые напряжения, а емкости шин 15 и 16 равны, усилитель считывания может обнаружить бесконечно малую разЕШцу напряжений в фиктивной и рабочей ячейках. В реальной схеме существует не симметрия, плеч триггера из-за разницы пороговых напряжений транзисторов 1 и 2 f геометрических размеров их каналов, емкостей шин 15 и Д6.. Эта ..несюлметрйя приводит к тому. что требуется вполне определенная минимальная величина разности напряжений в рабочем и фиктивном 9лемен те памяти, зависящая от величины разбаланса плеч триггера считывания, Основной вклад в него дает разность пороговых напряжений транзисторов 1 и 2, которая принципиально ограничивает чувсТвительность усилителя в личиной этой разности, а также разба ланс емкостей плеч усилителя, которы усугубляется тем, что рабочая:(на тра эйсторах 31 и 32) и фиктивная ячейка (на транзисторах 33 и 34) могут нахо диться на разных расстояниях от триг гера и благодаря конечному времени р пространения их сигналов по шинам 15 и 16 по-разному влиять на две сторон триггера. Благодаря соединению затворов транзисторов 3 и 4 через емкость 9 с тактовой шиной 11 и емкостной связи этих затворов с шинами 15 и 16 за счет емкостей затвор - канал, при повышении напряжения на затворах на переднем фронте сигнала по шине 11 из-за емк.рсти 9 потенциалы шин 15 и 16 получают некоторое положительное приращение, зависящее в том чнгсле от размеров каналов транзисторов 3 и 4. Причем меньшая емкость получает большее приращение напряжения и к моменту включения транзистора 5 ее потенциал оказывается выше.потенциала противоположного плеча триггера, имеющего большуто емкость При работе транзистора 5 эта меньшая емкость начинает разряжаться от большего потенциала, а параметры транзисторов 3 и 4 и емкостей шин 15 16 можно выбрать такими, что при падении потенциалов на 15 и 16 она не будет обгонять другое плечо, а направление переключения триггера будет определяться лишь сигналами, фор мируемыми . эле ментами .памяти, а не асимметрией емкостей плеч, и чувстви тельность усилителя в широком диапазоне разбросов емкостей плеч не будет зависеть от величин этого разброса., . Следующим включается тактовый сиг rictn по шине 12 и начинают проводить транзисторы 6 и 7, повышая через открытые транзисторы 3 и 4 потенциал в том плече триггера, в котором он был выше после сигнала по шине 10 и данные, которые при считывании из элементов памяти разрушаются, восстанавливаются и возвращаются вЭле.менты памяти , из которых они, были извлечены. В конкретном столбце элементов памяти, определенном дешифратором выбора столбцов (на чертеже не обозначен), включается транзистор 35 по сигналу на входе 36 и считанный из элемента памяти код передаеггся на мультиплексную шинуввод-вывод 34, с которой может быть считан. . В конце цикла считывания выключаются выбранные в нем линии выбора строк и данные фиксируются в элементах памяти и выключаются сигналы 10, 12 и 36, а включается сигнал предварительного заряда 23 и происхо дит подготовка к следующему циклу обращения. В цикле записи, в ходе которого прежнее содержимое элемента памяти заменяется новым, триггер в выбран- . ном столбце опрокидывается извне nq одному плечу ч;ерез транзистор 35 кодом, установленным ,на мультиплексной шине ввода-вывода 37.Триггер устанавливает на шинах 15 и 16 и на накопительной емкости выбранного элемента памяти новые напряжения в соответствии с записываемым числом, В невыбранных столбцах мультиплексная шина 37 не соединяется с триггерами и. они не обмениваются с ней данными, а только восстанавливают напряжение на накопительных емкостях выбранных в них элементов памяти, которое спадает со временем под действием тока тепловой утечки через р-п переход. Предлагаемая схема усилителя считывания обладает феиг- уществами перед известными. В ней полностью устраняется отрицательное влияние разбаланса емкостей плеч усилителя на его чувствительность, вследствие чего можно исключить из фиктивных элементов, памяти накопительные конденсаторы, а из схемы запоиданающего устройства-заряжающий.их генератор опорного напряжений .- За счет последовательного включения мощных ключевых транзисторов 6 и 7, характеристика заряда которых 38 показана на фиг,2 с нагрузочными 3 и 4, на затворы которых подается благодаря емкости 9, в качестве которой используется обычная МОП-емкость, напряжение, превышающее напряжение стокового питания, характеристика заряда которых 39, достигнута суммарная 40 характеристика с В 4 раза более ВЫСОКОЙ скоростью нарастания напряжения в плече триггера с логическо.й по сравнению с обычной нагрузкой 41 до уровня 0,9 - максиNtyMa при ТОМ же самом потреблении мощности в другом плече усилителя с Это преимущество логическим может бь1ть йспбльзовйно ке сколькими различными путями. Можно получить значительный выигрьпл в мощности при прежнем быстродействии, можно суще.ствённо выиграть в быстродействии при неизменной мощности, либр одновременно уменьшить потребляемую мощность и улучшить быстродействие. Кроме того, вследствие увеличения уровня логической , остающегося в элементе памяти после выключения выбирающеготранзистора и уменьшения

уровня логического благодаря меньшей величине остаточного напряжения на низкой стороне триггера, катсЗрое в известных схемах получается большим из-за высокой проводимости нагрузочнйх транзисторной, увеличивается сигнал, формируемый элементом ЙШйти на разрядных лййиях и веАичина накопительной емкости может быть уменьшена с соответствуютцим. уменьшением размеров элемента памяти и уменьшением размера кристалла с соответствующим увеличением процента выхода годных кристаллов.

Накопительная емкость может быть уменьшена дополнительно благодаря .высокой чувствительности предлагаемого усилителя высокой чувствительности предлагаемого усилители считывания даже при значительном разбалансе емкостей его плеч.

Формула изобретения

Усилителем считывания для матрицц одноТранзисторных запоминающих элементов, содержащий первый и второй транзисторы, соединенные триггернрй

8

связью,, стоки которыз соединены с истоками соответственно третьего и четвертого транзисторов, истоки пер. вого и второго транзисторов соедине.ны со стоком пятого транзистора, исток которого соединен с шиной нулевого потенциала, затвор - с одной из тактовых шин и шиной писания, отличающийся тем, что, с целью повышения чувствительности и быстродействия усилителя, он содержит шестой, седьмой и восьмой транзисторы и МОП-конденсатор, hepвый вывод которогосоединен со второй тактовой шиной, а второй вйвод - с затворами третьего и четвертого транзистора, стоки которых соединены соответственно с истоками шестого и седьмого транзистор гэвл Затворы которых подключены к третьей тактовой шине, а стоки - к шине питания, связанной с затвором и стоком восьмого транзистора, исток которого соединен со вторым выводом МОП -конденсатора.

Источники информации, принятые во внимание при экспертийе

1973, № 19,

II

1.

Электроника с.48. ч

2.3ЕЕЕ Тоигпае of Sobid-Stoite Circ nits voe. SG-1O,Je5,1975,p-257-

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Усилитель считывания на мдп-транзисторах | 1978 |

|

SU721852A1 |

| Усилитель считывания с регенерациейНА Мдп-ТРАНзиСТОРАХ | 1979 |

|

SU830575A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1976 |

|

SU928405A1 |

| Усилитель считывания | 1982 |

|

SU1084889A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Устройство для выборки адресов из блоков памяти | 1976 |

|

SU744722A1 |

| Усилитель считывания на моп-транзисторах /его варианты/ | 1980 |

|

SU883968A1 |

| Выходной усилитель | 1981 |

|

SU1015436A1 |

Авторы

Даты

1979-05-05—Публикация

1976-08-09—Подача