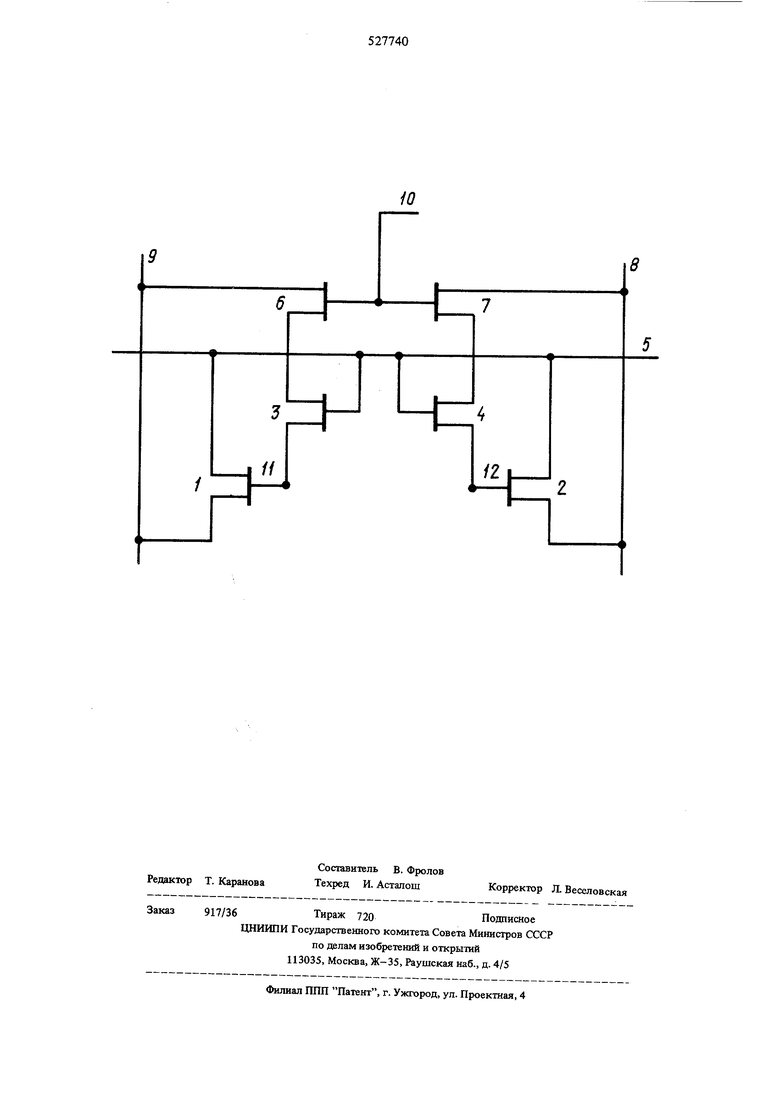

приводит к отпиранию транзисторов 3 и 4, позволяющих осуществить запись информации. Заряды емкостей изменяются при записи, если хранящаяся в них нформация противоположна записьшаемой, чго достигается путем подключения затворов транзисторов 3, 4 к выбранной адресной щине 5, а затворов транзисторов 6, 7 - к шине питания 10, находящейся при записи на уровне логической 1, что приводит к отпиранию этих транзисторов. При этом записьшаемая информация в парафазной форме подается на разрядные цшны 8, 9 и через открытые транзисторы 3, 4, 6, 7 поступает на узловые емкости 11 и 12 запоминающего злемента. При считьтании ток течет из выбранной адресной щины 5 через открытый транзистор 1 или 2, в зависимости от заряда емкостей 11 и 12, в одну из разрядных шин 8, 9, находящихся на уровне логического , фиксируя на выходе состояние элемента. Дополнительные транзисторы 6, 7 при считывании и сравнении заперты путем подачи уровня логического О на шину питания 10, что исключает возможность разрушения информации в этих режимах. В режимах сравнения внешняя информация подается парафазно обратным кодом на разрядные шины 8, 9 так, что в случае несовпадения хранящеГ ся на емкости и прямого кода внешней информации из соответствующей разрядной шины 8 или 9 через один из транзисторов 1 или 2 потечет ток в адресную щину 5, находящуюся при сравнении на уровне логического О. Состояние маскирования при сравнешй получается, когда на обе разрядные шины 8 и 9 подается уровень логического О ,. В результате транзисторы 1, 2 будут отключены и независимо от состояния емкостей 11 и 12 ток в адресной шине не появится, что указьшает на совпадение прямого кода внешней и хранящейся в данном элементе информации. Применение предложенного элемента в ассоциативных запоминающих устройствах позволяет повысить надежность их в работе. Формула изобретения Ассоциативньш запоминающий элемент на МОП-транзисторах, содержащий транзисторы записи, затворы которых подключены к адресной шине, истоки - к затворам транзисторов сравнения, истоки которых подключены к разрядным шинам, отличающийся тем, что, с целью упрощения конструкции и повышения надежности в работе, в него введены дополнительные транзисторы, затворы которых подключены к шине питания, стоки - к разрядным шинам, истоки - к стокам транзисторов записи, истоки транзисторов сравнения подключены к разрядным шинам, стоки - к адресной шине. Источники информации, принятые во внимание при экспертизе: 1.Патент США N 3609710 кл. 340-173, 1971 г. 2.Авторское свидетельство № 408374, кл G 11 15/00, 1971 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативный запоминающий элемент на моп-транзисторах | 1972 |

|

SU441592A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Адресный дешифратор для полупроводникового постоянного запоминающего устройства | 1980 |

|

SU960949A1 |

| Ассоциативный запоминающий элемент на мдп-транзисторах | 1980 |

|

SU868834A1 |

| СТАТИЧЕСКАЯ ЗАПОМИНАЮЩАЯ ЯЧЕЙКА С ДВУМЯ АДРЕСНЫМИ ВХОДАМИ | 2011 |

|

RU2470390C1 |

| Накопитель для полупостоянного запоминающего устройства с электрической перезаписью информации | 1973 |

|

SU519760A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1978 |

|

SU769628A1 |

| Элемент памяти для ассоциативного накопителя | 1976 |

|

SU690565A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА МДП-ТРАНЗИСТОРАХ | 1973 |

|

SU408374A1 |

Авторы

Даты

1976-09-05—Публикация

1974-10-23—Подача