1

Изобретение относится к области запоминающих устройств.

Известно устройство для контроля оперативного накопителя информации, содержащее схему пуска, выход которой подключен к регистру числа, счетчику адресов и счетчику циклов, схему сравнения, выход которой соединен со схемой регистрации, подключенной к схеме останова, схему «И.

Известное устройство .позволяет контролировать работу оперативного накопителя информации при помощи теста «дождь, правильность которого определяется визуально с помощью растра на осциллографе. Такой контроль накопителя в производственных условиях имеет тот недостаток, что в определении правильной работы накопителя по тесту «дождь всегда должен участвовать оператор.

Описываемое устройство отличается от известного тем, что оно соодержит коммутатор разрядов, вход которого подключен к входной шине устройства, а выход - к одному входу схемы «И, дешифратор цикла, вход которого подсоединен к первому выходу счетчика циклов, а выход - к другому входу схемы «И, дополнительные счетчики, входы которых .подключены ко второму выходу счетчика циклов и выходу схемы «И, соответственно, а выходы - ко входам схемы сравнения.

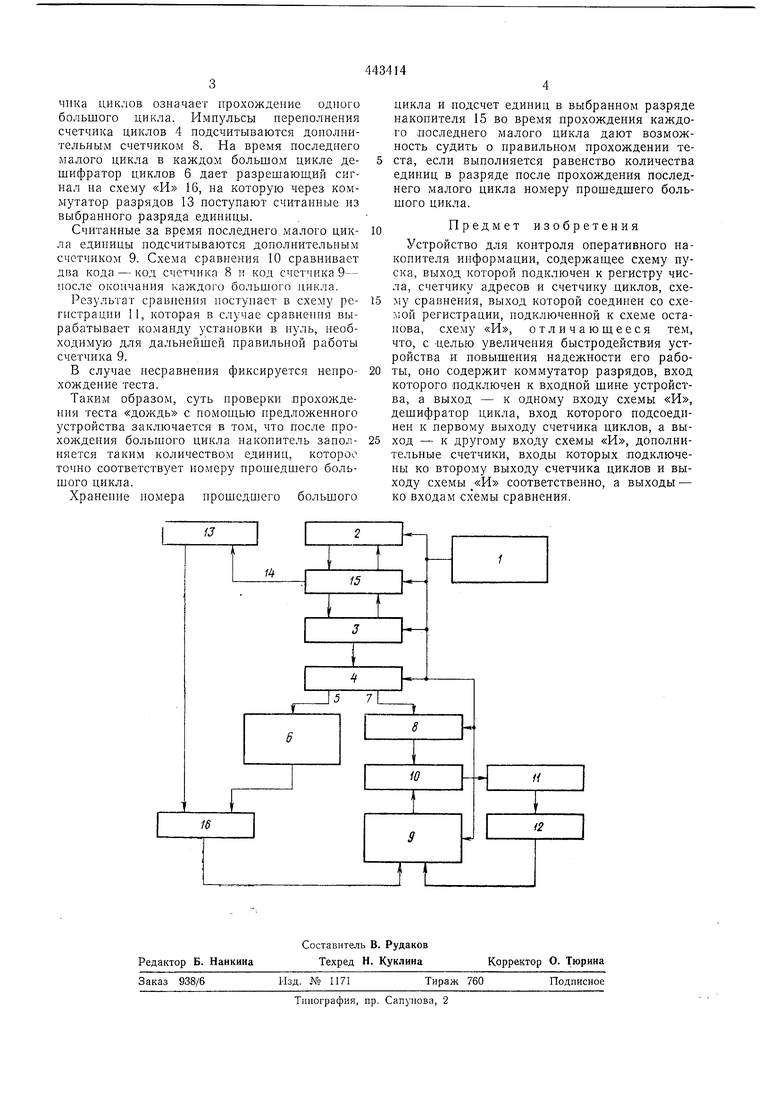

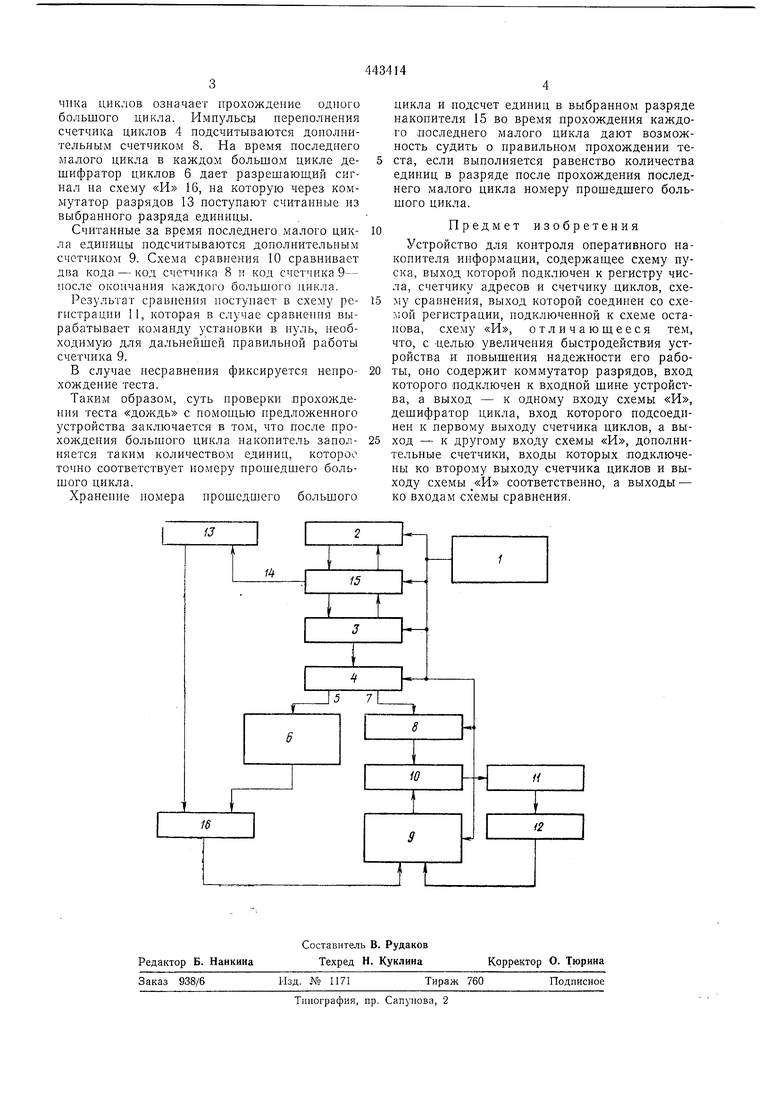

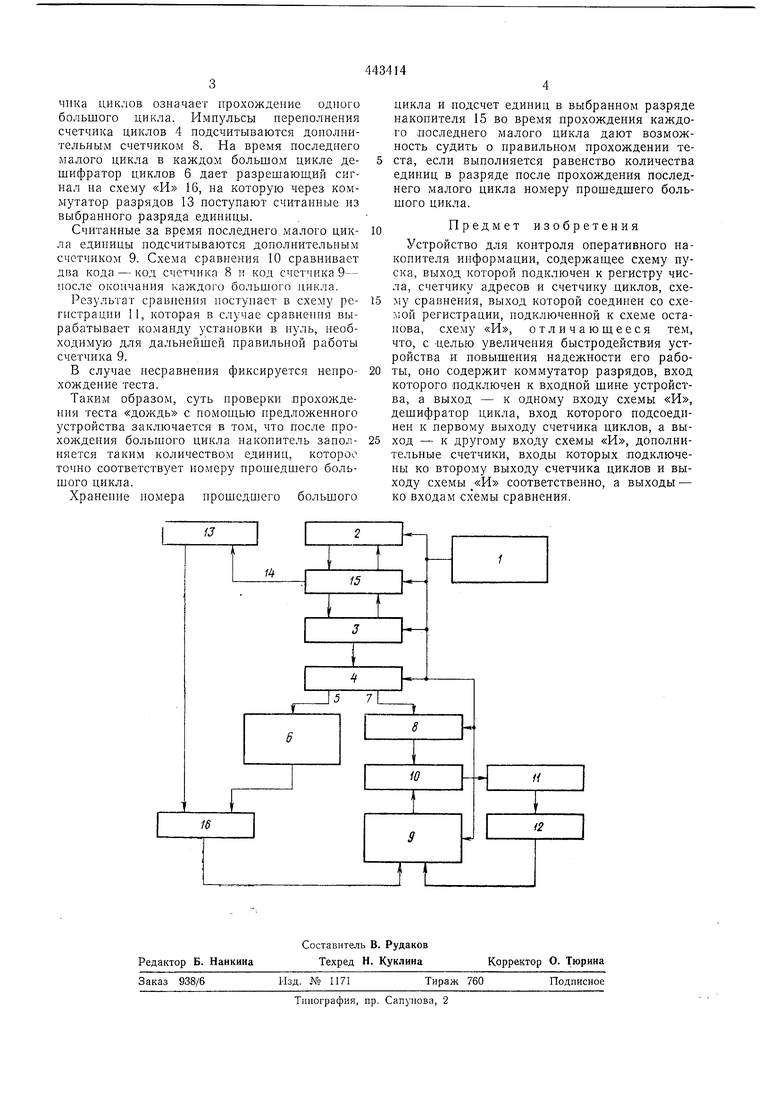

Указанные отличия позволяют увеличить быстродействие устройства и повысить надежность его работы. На чертеже изображена блок-схема предлагаемого устройства.

Оно содержит схему пуска 1, выход которой подключен к регистру числа 2, счетчику адресов 3 и счетчику циклов 4, первый выход 5 которого подсоединен ко входу дешифратора

циклов 6, а второй выход 7 - к одному из дополнительных счетчиков 8 и 9, схему сравнения 10, входы которой подключены к выходам счетчиков 8 и 9, а выход - к схеме регистрации 11, Подключенной к схе.ме останова 12,

коммутатор разрядов 13, вход которого подключен к входной шине 14 устройства, связанной с проверяемым накопителем 15, а выход- к одному входу схемы «И 16, другой вход которой подсоединен к выходу дешифратора

циклов 6, а выход - к одному из входов счетчика 9, другой вход которого связан со схемой останова 12.

Устройство работает следующим образом. Схема пуска 1 совместно с накопителем 15,

регистром числа 2, счетчиком адресов 3 обеспечивает получение теста «дождь.

Переполнение счетчика адресов 3 означает прохождение одного малого цикла. Импульсы переполнения счетчика адресов подсчитываются счетчиком циклов 4. Переполнение счетчнка циклов означает прохождение одного большого цикла. Импульсы переполнения счетчика циклов 4 подсчитываются дополнительным счетчиком 8. На время последнего малого цикла в каждом большом цикле дешифратор циклов 6 дает разрешающий сигнал на схему «И 16, на которую через коммутатор разрядов 13 поступают считанные из выбранного разряда единицы.

Считанные за время последнего малого цикла единицы подсчитываются дополнительным счетчиком 9. Схема сравнения 10 сравнивает два кода - код счетчика 8 и код счетчика 9- после окончания каждого большого цикла.

Результат сравнения поступает в схему регистрации 11, которая в случае сравнения вырабатывает команду установки в нуль, необходимую для дальнейшей правильной работы счетчика 9.

В случае несравнения фиксируется непрохождение теста.

Таким образом, суть проверки ярохождения теста «дождь с помощью предложенного устройства заключается в том, что после прохождения большого цикла накопитель заполняется таким количеством единиц, которое точно соответствует номеру прошедшего большого цикла.

Хранение номера прошедшего большого

цикла и нодсчет единиц в выбранном разряде накопителя 15 во время прохождения каждого последнего малого цикла дают возможность судить о правильном прохождении теста, если выполняется равенство количества единиц Б разряде после прохождения последнего малого цикла номеру прошедшего большого цикла.

Предмет изобретения

Устройство для контроля оперативного накопителя информации, содержащее схему пуска, выход которой подключен к регистру числа, счетчику адресов и счетчику циклов, схему сравнения, выход которой соединен со схемой регистрации, подключенной к схеме останова, схему «И, отличающееся тем, что, с Целью увеличения быстродействия устройства и повышения надежности его работы, оно содержит коммутатор разрядов, вход которого подключен к входной шине устройства, а выход - к одному входу схемы «И, дешифратор цикла, вход которого подсоединен к первому выходу счетчика циклов, а выход - к другому входу схемы «И, дополнительные счетчики, входы которых подключены ко второму выходу счетчика циклов и выходу схемы «И соответственно, а выходы - ко входам схемы сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативной памяти | 1981 |

|

SU1001181A1 |

| Устройство для контроля накопителей информации | 1979 |

|

SU767846A2 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1014041A1 |

| УСТРОЙСТВО для КОНТРОЛЯ ОПЕРАТИВНЫХ НАКОПИТЕЛЕЙ | 1972 |

|

SU341087A1 |

| Устройство для регистрации цифровой информации | 1986 |

|

SU1386915A2 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для контроля полупроводниковой оперативной памяти | 1984 |

|

SU1244727A1 |

| Устройство для контроля оперативной памяти | 1978 |

|

SU744736A1 |

| Устройство для моделирования отказов | 1986 |

|

SU1363231A1 |

16

W

Н

12

Авторы

Даты

1974-09-15—Публикация

1972-11-24—Подача