Изобретение относится к вычисли- тельной технике и может быть исполь--зовано для функционального контроля микросхем оперативных запоминающих устройств (ОЗУ),

. Цель изобретения - :повышенйе. дос- .товерности контроля.

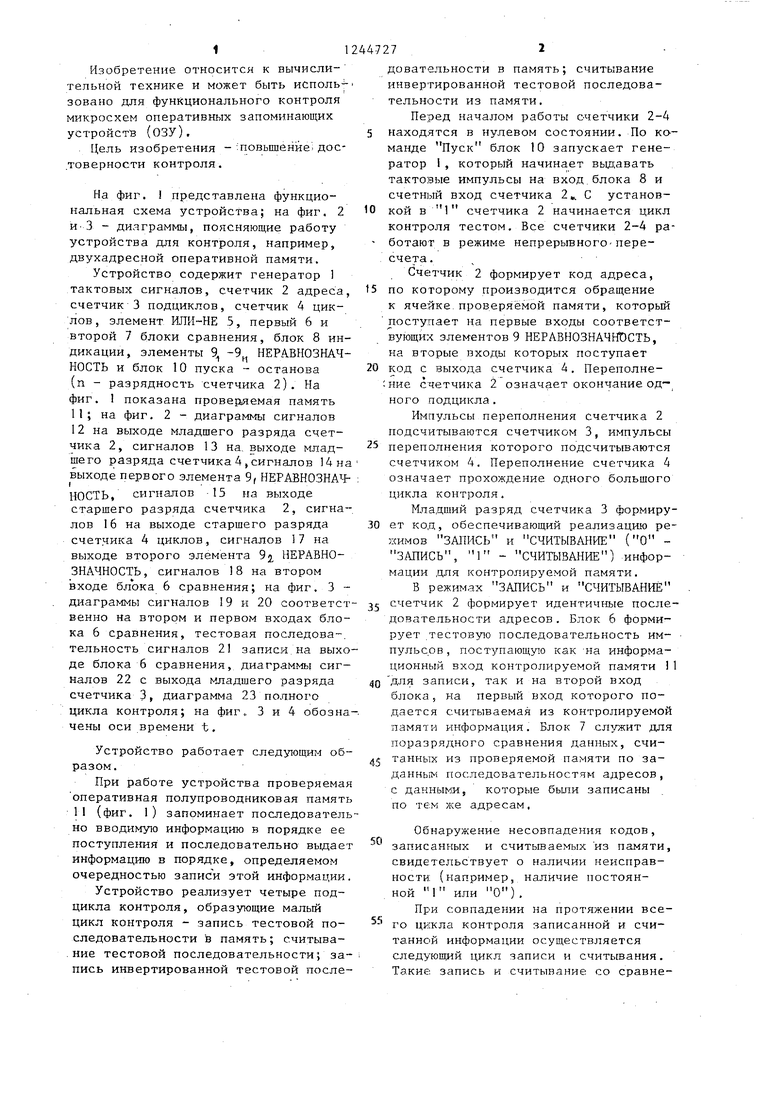

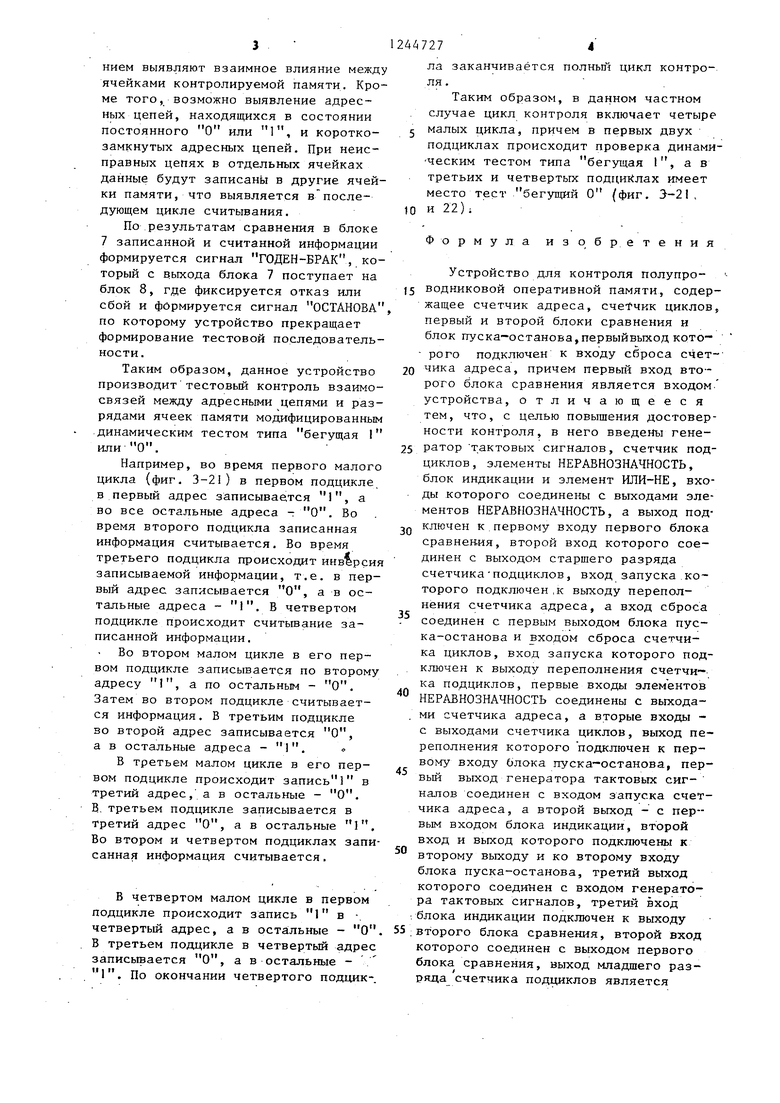

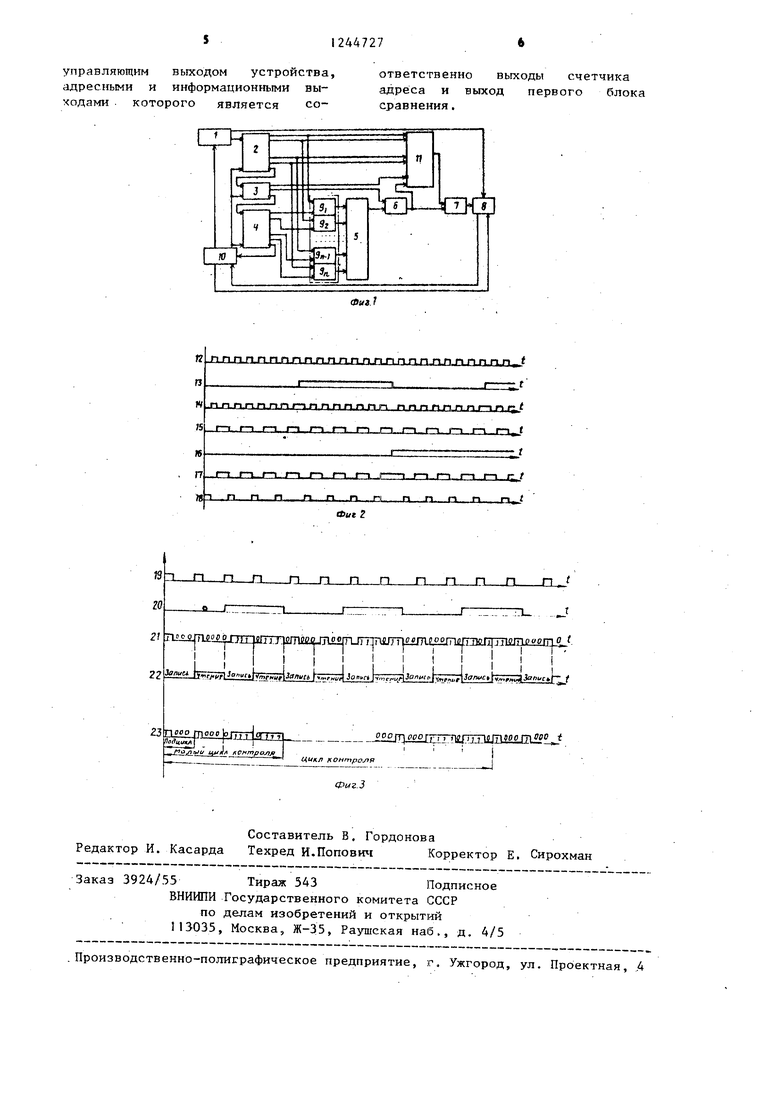

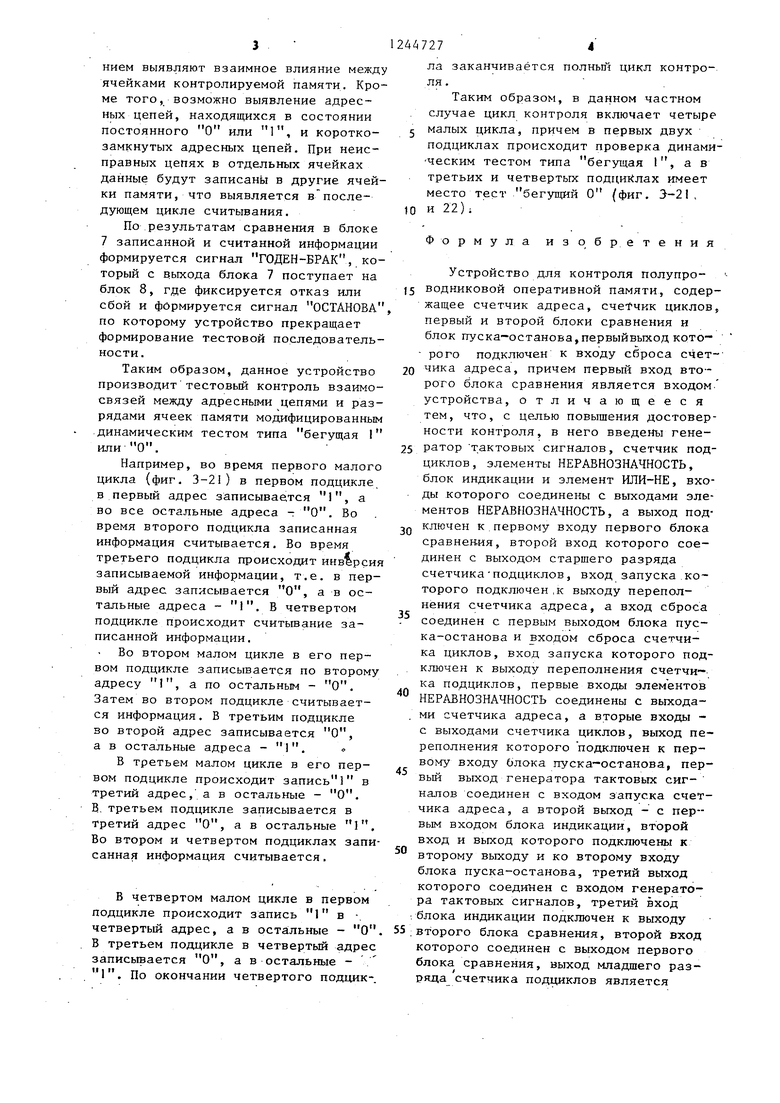

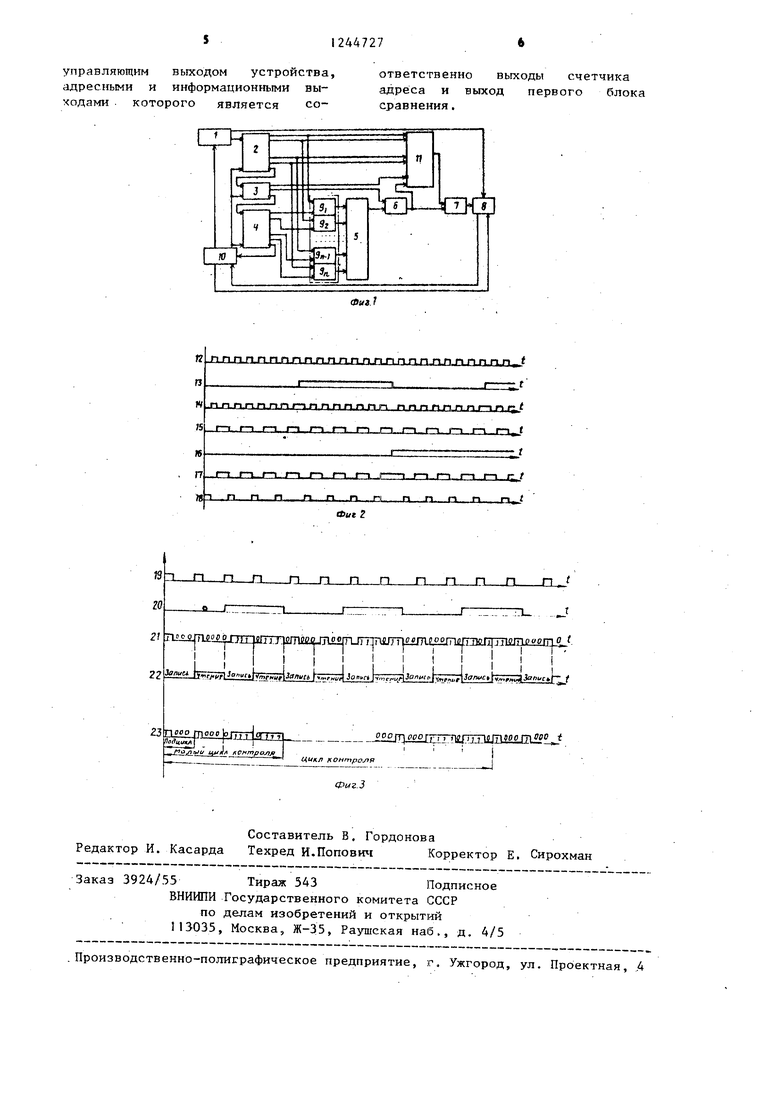

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 и-З - диаграммы, поясняющие работу устройства для контроля, например, двухадресной оперативной памяти.

Устройство содержит генератор 1 тактовых сигналов, счетчик 2 адреса, счетчик 3 подциклов, счетчик 4 циклов, элемент ИЛИ-НЕ 5, первый 6 и второй 7 блоки сравнения, блок 8 индикации, элементы 9, -9, НЕРАВНОЗНАЧНОСТЬ и блок 10 пуска - останова (п - разрядность счетчика 2). На фиг. 1 показана проверяемая память 11; на фиг. 2 - диаграммы сигналов 12 на выходе младщего разряда счетчика 2, сигналов 13 на, выходе младшего разряда счетчика 4 , сигналов 14 на выходе первого элемента 9, HEPABHOBHAi НОСТЬ, сигналов -15 на выходе старшего разряда счетчика 2, сигналов 16 на выходе старшего разряда счетчика 4 циклов, сигналов 17 на выходе второго элемента 9у НЕРАВНОЗНАЧНОСТЬ, сигналов 8 на втором входе блока 6 сравнения; на фиг. 3 - диаграммы сигналов 19 и 20 соответст венно на втором и первом входах блока 6 сравнения, тестовая последова-. тельность сигналов 21 записи.на выходе блока 6 сравнения, диаграммы сигналов 22 с выхода младшего разряда счетчика 3, диаграмма 23 полного цикла контроля; на фиг,. 3 и 4 обозна чены оси времени t.

Устройство работает следующим образом.

При работе устройства проверяемая оперативная полупроводниковая память 11 (фиг. 1) запоминает последовательно вводимую информацию в порядке ее поступле1Шя и последовательно выдает информацию в порядке, определяемом очередностью записи этой информации.

Устройство реализует четыре под- цикла контроля, образующие малый цикоТ контроля - запись тестовой последовательности в память; считыва- ,ние тестовой последовательности; запись инвертированной тестовой последовательности в память; считывание инвертированной тестовой последовательности из памяти.

Перед началом работы счетчики 2-4 находятся в нулевом состоянии. По команде Пуск блок 10 запускает генератор 1, который начинает вьщавать тактовые импульсы на вход,блока 8 и счетН1з1Й вход счетчика 2 С установкой в I счетчика 2 начинается цикл

контроля тестом. Все счетчики 2-4 ра- ботают в режиме непрерывного-пересчета.

Счетчик 2 формирует код адреса, по которому производится обращение к ячейке,проверяемой памяти, который поступает на первые входы соответствующих элементов 9 НЕРАВНОЗНАЧНОСТЬ, на вторые входы которых поступает код. с выхода счетчика 4. Переполне- ние счетчика 2 означает окончание одного подцикла.

Импульсы переполнения счетчика 2 подсчитываются счетчиком 3, импульсы переполнения которого подсчитываются счетчиком 4. Переполнение счетчика 4 означает прохождение одного большого цикла контроля.

Младший разряд счетчика 3 формирует код, обеспечивающий реализацию режимов ЗАПИСЬ и СЧИТЫВАНИЕ (О - ЗАПИСЬ, 1 - СЧИТЫВАНИЕ) информации для контролируемой памяти.

В режимах ЗАПИСЬ и СЧИТЫВАНИЕ счетчик 2 формирует идентичные последовательности адресов. Блок 6 формирует тестовуто последовательность им- - пульсов, поступающую как на информационный вход контролируемой памяти 11 для записи, так и на второй вход блока, на первый вход которого подается считываемая из контролируемой памяти информация. Блок 7 служит для поразрядного сравнения данных, счи- танных из проверяемой памяти по заданным последовательностям адресов, с данныки, которые были записаны по тем же адресам.

Обнаружение несовпадения кодов, записанных и считываемых из памяти, свидетельствует о наличии неисправности (например, наличие постоянной 1 или О).

При совпадении на протяжении все- го цикла контроля записанной и считанной информации осуществляется следующий цикл записи и считывания. Такие; запись и считывание со сравнением выявляют взаимное влияние между ячейками контролируемой памяти. Кроме того, возможно выявление адресных цепей, находящихся в состоянии постоянного О или I, и коротко- замкнутых адресных цепей. При неисправных цепях в отдельных ячейках данные будут записаны в другие ячейки памяти, что выявляется в последующем цикле считывания.

По результатам сравнения в блоке 7 записанной и считанной информации формируется сигнал ГОДЕН-БРАК, который с выхода блока 7 поступает на блок 8, где фиксируется отказ или сбой и формируется сигнал ОСТАНОВА по которому устройство прекращает формирование тестовой последовательности.

Таким образом, данное устройство производит тестовый контроль взаимосвязей между адресными цепями и разрядами ячеек памяти модифицированным динамическим тестом типа бегущая I или О.

Например, во время первого малого цикла (фиг. 3-21) в первом подцикле, в первый адрес записывается 1, а во все остальные адреса - О, Во время второго подцикла записанная информация считывается. Во время третьего подцикла происходит инверси записываемой информации, т.е. в первый адрес записывается О, а в остальные адреса - Г. В четвертом подцикле происходит считьгоание записанной информации.

Во втором малом цикле в его первом подцикле записывается по второму адресу 1, а по остальным - О. Затем во втором подцикле считывается информация. В третьим подцикле во второй адрес записывается О, а в остальные адреса - 1. о

В третьем малом цикле в его первом подцикле происходит запись в третий адрес, а в остальные - О. В. третьем подцикле записывается в

Ui tl

третий адрес О, а в остальные

I

Во втором и четвертом подциклах записанная информация считывается.

В четвертом малом цикле в первом подцикле происходит запись 1 в -, четвертый адрес, а в оста;льные - О. В третьем подцикле в четвертый адрес записывается О, а в остальные - 1. По окончании четвертого поддик-.

,

.

10

15

20

25

30

35

40

45

50

55

ла заканчивается полньпЧ цикл контроля.

Таким образом, в данном частном случае цикл контроля включает четыре малых цикла, причем в первых двух подциклах происходит проверка динами- -ческим тестом типа бегутцая 1, а в третьих и четвертых подциКлах имеет место тест бегущий О (фиг. 3-21, и 22);

Формула изобретения

Устройство для контроля полупроводниковой оперативной памяти, содержащее счетчик адреса, счетчик циклов, первый и второй блоки сравнения и блок пуска-останова,первыйвыход КОТО - рого подключен к входу сброса счетчика адреса, причем первый вход второго блока сравнения является входом устройства, отличающееся тем, что, с целью повьшения достоверности контроля, в него введены генератор тактовых сигналов, счетчик под- циклов, элементы НЕРАВНОЗНАЧНОСТЬ, блок индикации и элемент ИЛИ-НЕ, входы которого соединены с выходами элементов НЕРАВНОЗНАЧНОСТЬ, а выход подключен к первому входу первого блока сравнения, второй вход которого соединен с выходом старшего разряда счетчика подциклов, вход запуска которого подключен ,к выходу переполнения счетчика адреса, а вход сброса соединен с первым выходом блока пуска-останова и входом сброса счетчика циклов, вход запуска которого подключен к выходу переполнения счетчи - ка подциклов, первые входы элементов НЕРАВНОЗНАЧНОСТЬ соединены с выходами счетчика адреса, а вторые входы - с выходами счетчика циклов, выход переполнения которого подключен к первому входу блока пуска-останова, первый выход генератора тактовых сиг- налов соединен с входом запуска счетчика адреса, а второй выход - с первым входом блока индикации, второй вход и выход которого подключены к второму выходу и ко второму входу блока пуска-останова, третий выход которого соединен с входом генератора тактовых сигналов, третий вход блока индикации подключен к выходу второго блока сравнения, второй вход которого соединен с выходом первого блока сравнения, выход младшего разряда счетчика подциклов является

512447276

управляющим выходом устройства, ответственно выходы счетчика адресными и информационными вы- адреса и выход первого блока ходами которого является со- сравнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативных запоминающих устройств | 1986 |

|

SU1441457A1 |

| Устройство для контроля блоков оперативной памяти | 1983 |

|

SU1161993A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1001182A1 |

| Логический анализатор | 1988 |

|

SU1654822A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1014041A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для контроля многоразрядных блоков памяти | 1987 |

|

SU1536444A1 |

| Устройство для контроля блоков памяти | 1985 |

|

SU1317486A1 |

| Устройство для контроля ЦВМ | 1987 |

|

SU1509908A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

Изобретение относится к вычислительной технике и может быть, использовано для функционального контроля микросхем оперативных запоминающих устройств. Целью изобретения является повышение достоверности контроля. Устройство содержит генератор тактовых сигналов, счетчик адреса, счетчик циклов, счетчик под- циклов, блоки сравнения, блок пуска- останова, элемент ИЛИ-НЕ и элементы НЕРАВНОЗНАЧНОСТЬ. В устройстве реализуются четыре подцикла контроля, образующие полный цикл: запись тестовой последовательности в память, ее считывание из памяти, запись инвертированной тестовой последовательности в память, считывание последней из памяти, 3 ил. с (Л С Н fe 4;а 4 1С

-ППП ПП Л ПП J1 , П Р J

-а-Г.

./Щ 1ЦГПШПи11Ш П1.

i

Цик/f г онтроля

Фиг.З

Составитель В, Гордонова Редактор И. Касарда Техред И.Попович Корректор Е. Сирохман

Заказ 3924/55 Тираж 543Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, .4

| Устройство для контроля накопителя информации оперативного запоминающего устройства | 1976 |

|

SU622174A1 |

| Солесос | 1922 |

|

SU29A1 |

| 0 |

|

SU407398A1 | |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-07-15—Публикация

1984-12-25—Подача