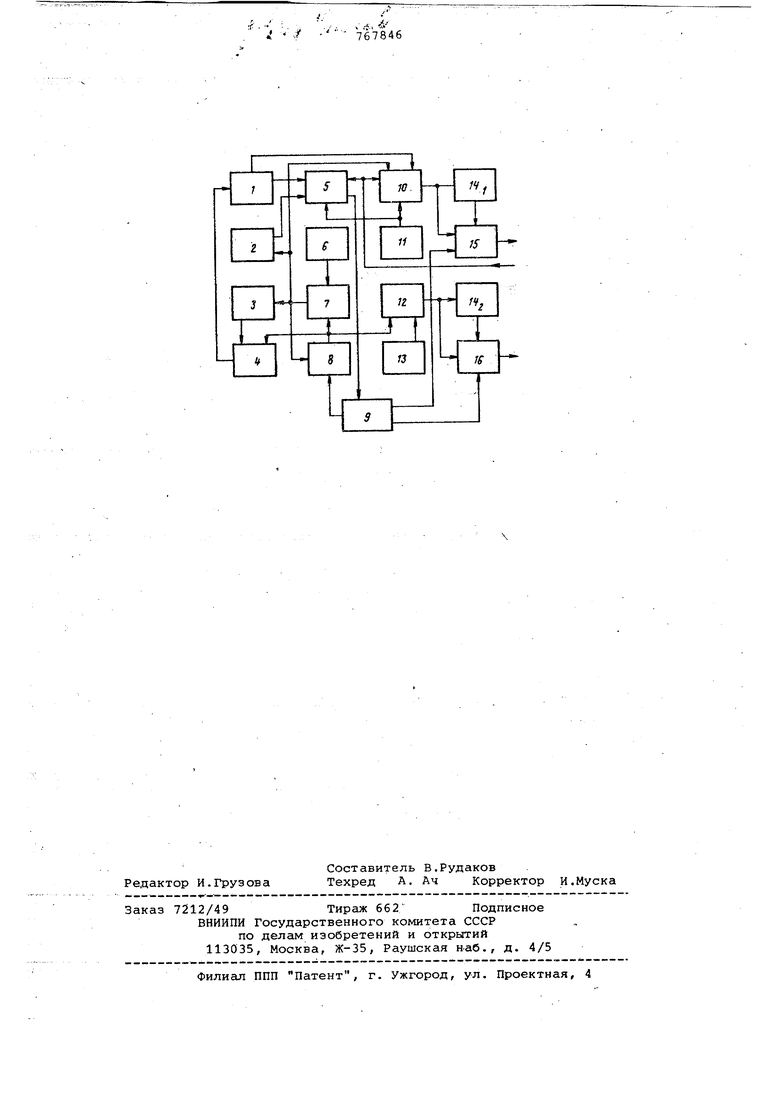

Изобретение относится к запоминаю щим устройствам. Известно устройство по авт.св. 407398, содержащее схему пуска-останова, вход которой подключен к вы ходу схемы сравнения чисел, а выход к счетчику адреса, схему сравнения адреса, один из входов которой подсоединен к выходу счетчика адреса, а выход - к схеме формирования кода чисел/ контрольный регистр числа, счетчик циклов, вход которого подключен к выходу схемы сравнения адреса и ко входу контрольного регист ра чисел, схему сравнения циклов, один вход которой подсоединен к выходу счетчика циклов, другой - к вых ду счетчика адреса, схему управления кодом чисел, вход которой соединен с выходом схемы сравнения циклов, а выходы - со входами схемы формирова ния кода чисел и схемы сравнения чисел соответственно ij. Это устройство не обладает доста точной достоверностью .контроля из-з отсутствия перебора адресов от стар ших к младшим при проверке влияния формации, записанной в одном разряде различных адресов, и отсутствии проверки вида бегущая 1. Целью изобретения является повышение достоверности контроля. Поставленная цель достигается тем, что устройство содержит коммутаторы числа и адреса и элементы НЕ, причем один из выходов схемы пуска-останова подключен к первому входу коммутатора числа, второй и третий входы которого соединены соответственно с выходами схемы формирования кода числа и одного из элементов НЕ, вход которого соединен с выходом схемы формирования кода числа, другой выход схеNBJ пуска-останова подключен к первому входу коммутатора адреса, второй и третий входы которого соединены соответственно с выходами схемы формирования кода адреса и другого элемента КЕ, вход которого соединен с выходом схемы формирования кода адреса, выходы коммутаторов числа и адреса являются выходами устройства. На чертеже представлена структурная схема устройства. Устройство содержит схему 1 управления кодом чисел, .контрольный регистр 2 числа, счетчик 3 циклов, схему 4 сравнения циклов, схему 5 сравнения чисел, имитатор 6 ввода количества адресов, схему 7 сравнения адреса, счетчик 8 адреса, схему 9 п ка-останова, схему 10 формирования кода числа, имитатор 11 ввода кода числа, схему 12 формирования кода адреса, имитатор 13 ввода начальног адреса, элементы НЕ 14 и 147, , ком | утаторы числа 15 и адреса 16 . Один из выходов схемы 9 подключён к первому входу коммутатора 15 числа, второй и третий входы которого соединены соответственно с выходами схемы 10 и элемента НЕ 14-,, входом связанного с выходом схемы 1 Другой выход схемы 9 подключен к первому входу коммутатора 16, второ и третий входы которого соединены соответственно с выходами схемы 12 и элемента НЕ 14 , вход которого соединен с выходом схемы 12. Выходы коммутаторов 15 и 16 являются выходами устройства, к которым под клйча отся входы контролируемого опе ративного запоминающего устройст-ва (ОЗУ). Работает устройство следующим об разом. Устройство проверяют ОЗУ в два э па. На первом этапе производится пр вёрКа влияния различных кодовых комбинаций в числе. По сйг ГШту; поступающему со схемы 9 пуска-останов й, устанавливается в нулевое соетояние счетчик 8 адреса, счетчик 3 циклов, контрольный регистр 2 чис ла, код с имитатора 13 ввода началь ного адреса (например, 00...00). поступает на -схему 12- формирования аадреса, коммутаторы числа и адреса устанавливаются для трансляции в ОЗУ соответственно информации схемы iO фо змирования кода числа и схемы 12 формирования кода адреса Производится запись нулевой информации по нулевому адресу, счи тиванне и сравнение записанной информации с информацией, которая хранится в контрольном регистре 2 числа. При совпадении записанной и считанной информации происходит изменение адреса на +1 в счетчике 8 адреса и измененный адрес поступае:т в ОЗУ. Нулевая информация записывается по первому адресу. Изменение кода адреса +1 происходит в каждом цикле записи информации в ОЗУ и по всему информационному об екту/ определяемому И1 1итатором 6 вв дж количества адресов, производится запись нулевой информации. После записи нулевой информации по послед му адресу схема 7 сравнения адреса формирует сигнал, разрешающий изменение информации на +1 в контроль ном регистре 2 числа и схемы 10 фор мирования кода числа. Измененный ко числа (00...00) записывается и счи тйвается со сравнением по всему информационному объекту ОЗУ, и по Сигналу, поступающему со схемы 7 cp

767846 нения адреса, происходит изменение кода числа на +1. Такая операция повторяется автоматически до запи.си по всему информационному объему кода 11...11. В случае неисправности ОЗУ считанная и записанная информация не совпадает и схема 5 сравнения чисел выдает сигнал, прерывающий работу устройства. . На втором этапе производится проверка влияния информации, записанной в одном разряде различных адресов. Проверка производится по алгоритмам тестов бегущий О и бегущая. Выполнение алгоритма бегущий О осуществляется с,Тедующим образом. Сигналы со схемы 9 пуска-останова устанавливают коммутаторы числа 15 и адреса 16 для трансляции информации в ОЗУ соответственно со схемы 10 формирования кода числа и схемы 12 формирования кода адреса. Затем код числа с имитатора 11 поступает на схему 10 формирования кода числа. В первом цикле проверки информационного объема происходит сравнение нулевой информации, поступающей со счетчика 8 адреса и счетчика 3 циклов. В результате сравнения схема 1 управления кодом чисел зайрещает запись кода числа, поступающего с имитатора 11 в ОЗУ. Таким .образом, в первом цикле по нулевОму адресу в ОЗУ записывается код 00...00, а по остальным адресам - код, установленный на имитаторе 11 (наприN p, 11. . .11). В такте считывания по сигналу, поступающему со схемы 4 сравнения циклов , схема 1 управления кодом чисел запрещает прохождение кода числа с имитатора 11 на; схему 5 сравнения чисел Информация, считанная по нулевому адресу, сравнивается с кодом 00...00, а информация, считанная по другим. Остал&Ным адресам, сравнивается с кодом, поступающим с имитатора 11 ввода кода числа. После считыва- . НИН информации по последнему адресу, определяемому имитатором 6, схема 7 сравнения адреса вырабатывает сигнал, riO которому происходит изменение содержимого счетчика 3 циклов на . Схема 4 сравнения циклов вырабаТйВает - с 1гнал, по которому схема 1 управления кодом чисел запрещает запись кода числа (производит запись кода 00...00) по первому адресу и обеспечивает сравнение информации, записанной по первому адресу, с кодом 00...00, а информации, записанной по остальным адресам, в том числе и по нулевому, - с информацией, поступающей с имитатора 11. В пОйлёдующих циклах происходит запись кода 00...00 по второму, третьему и т.д. адресам при записи кода числа, поступающего с имитатора 1 по остальным адресам информационного объема. Таким образом обеспечивается выпо нение алгоритма бегущий О с перебором адресов от младшего к старшему Для выполнения алгоритма бегущий О с перебором адресов от старшего к младшему схема 9 пуска-останова подает сигнал для переключения комму татора 16 адреса для трансляции информации в ОЗУ из схемы 12 формирования кода адреса через элемент НЕ 14 . При этом через элемент НЕ 142 информация со схемы 12 формирования кода адреса транслируется таким обpasofvi, что на первом цикле в ОЗУ поступает последний адрес проверяемо го объема адресов, затем предпоследний и т.д. Остальная работа устройства аналогична проверке при переборе адресов от младшего к старшему. В случае несовпадения записанной и считанной информации схема 5 сравнения чисел выдаёт сигнал, прерывающий работу устройства. Выполнение алгоритма бегущая 1 производится следующим образом. В начале проверки при переборе адресов от младшего к старшему со схемы 9 пуска-останова поступают сигналы о переключении коммутатора 1 числа для трансляции в ОЗУ информации, поступающей со схемы 10 формирования кода числа через элемент НЕ 14, и переключении коммутатора 16 адреса для тра нсляции в ОЗУ информации, поступающей со схемы 12 форми рования кода адреса. Остальная работа схемы аналогична проверке при пер .боре адресов от млаДшего к старшему при выполнении алгоритма бегущий О однако схема 5 сравнения чисел выдае сигнал, прерывакядий работу устройства, в случае совпадения информации хотя бы в одном разряде. Б начале проверки при переборе адресов от старшего к младшему со схемы 9 пуска-останова поступают сигналы о переключении коммутаторов числа 15 и адреса 16 для трансляции в ОЗУ информации соответственно со схемы 10 формирования кода числа fi схемы 12 формирования кода адреса через элементы НЕ 14-, и 142, причем информация со схемы 12 формирования кода адреса транслируется таким образом, что на первом цикле в ОЗУ поступает последний адрес проверяемого объема адресов, затем предпоследний и т.д. Остсшьная работа устройства аналогичная проверке при переборе адресов от младшего к старшему. В описанном устройстве повышена достоверность контроля ОЗУ за счет обеспечения выполнения алгоритма бегущая 1 и перебора адресов при контроле от младшего к старшему. Формула изобретения Устройство для контроля накопителей информации по авт.св.№407398, отличающееся тем, что, с целью повышения достоверности контроля, оно содержит коммутаторы числа и адреса и элементы НЕ, причем один из выходов схемы пуска-останова подключен к первому входу коммутатора числа, второй и третий входы которого соединены соответственно с выходами схемы формирования кода числа и одного из элементов НЕ, вход которого соединен с выходом схемы формирования кода числа, другой выход схемы пуска-останова подключен к первому входу коммутатора адреса, второй и третий входы которого соединены соответственно с выходами схемы формирования кода адреса и другого элемента НЕ, вход которого соединен с выходом схемы формирования кода адреса, выходы коммутаторов числа и адреса являются выходами устройства. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 407398, кл., G 11 С 29/00, 1972 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля памяти | 1979 |

|

SU769642A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Имитатор канала | 1987 |

|

SU1467556A1 |

| Система автоматического контроля параметров электронных схем | 1989 |

|

SU1700538A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU980166A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Устройство для контроля памяти | 1979 |

|

SU783855A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1003150A1 |

| Устройство для контроля цифровыхОб'ЕКТОВ | 1978 |

|

SU798844A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

Авторы

Даты

1980-09-30—Публикация

1979-01-08—Подача