I

Изобретение относится к области вычислительной техники и может быть использовано, например, в цифровых вычислительных машинах (ЦВМ), построенных на основе больших интегральных схем.

Известно устройство шщ вычисления выражении вида j AiX , содержащее блок управленшг, регистры операндов и результата, сушяаторы.

Однако для вычисления выражений вида f Aiх требуется многократное выполнение операций сложения и умножения и многократное обращение к запоминащему устройству, что требует больших затрат времени.

Цель изобретения - повышение быстродействия устройства.

Это достигается тем, что устройство содержит коммутатор и блок сравнения, причем выходы регистра первого операнда соединены со входом первого сушатора и с

первым входом блока сравнения, вход которого через комвяутатор соединен двусторонними связями с сумматорами и с регистрами второго 5 операнда, сдвиговые входы которых и сдвиговый вход регистра результата соединены с одним выходом блон ка управления, другой выход которо го соединен с управляющим входом

10 коммутатора, запускающий вход второго сумматора соединен с первым выходом блока сравнения, второй выход которого соединен со входом блока управления, а выход старпего

15 разряда самого старпего регистра второго операнда соединен со входом младшего разряда регистра результата.

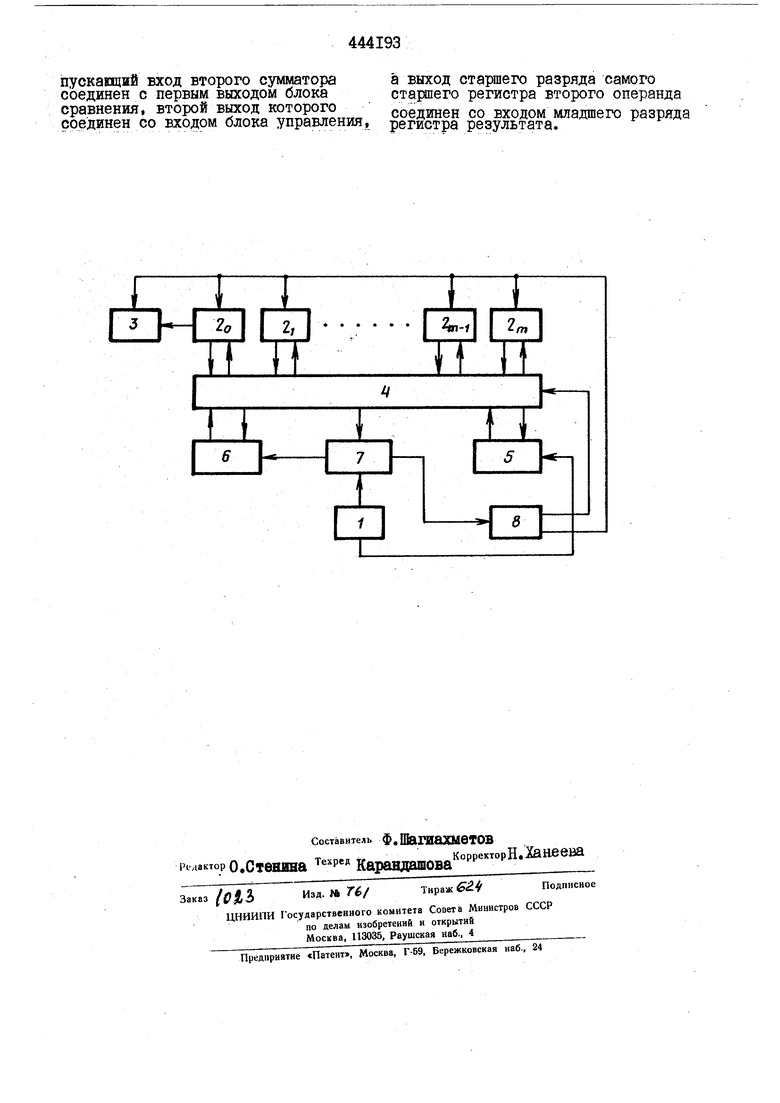

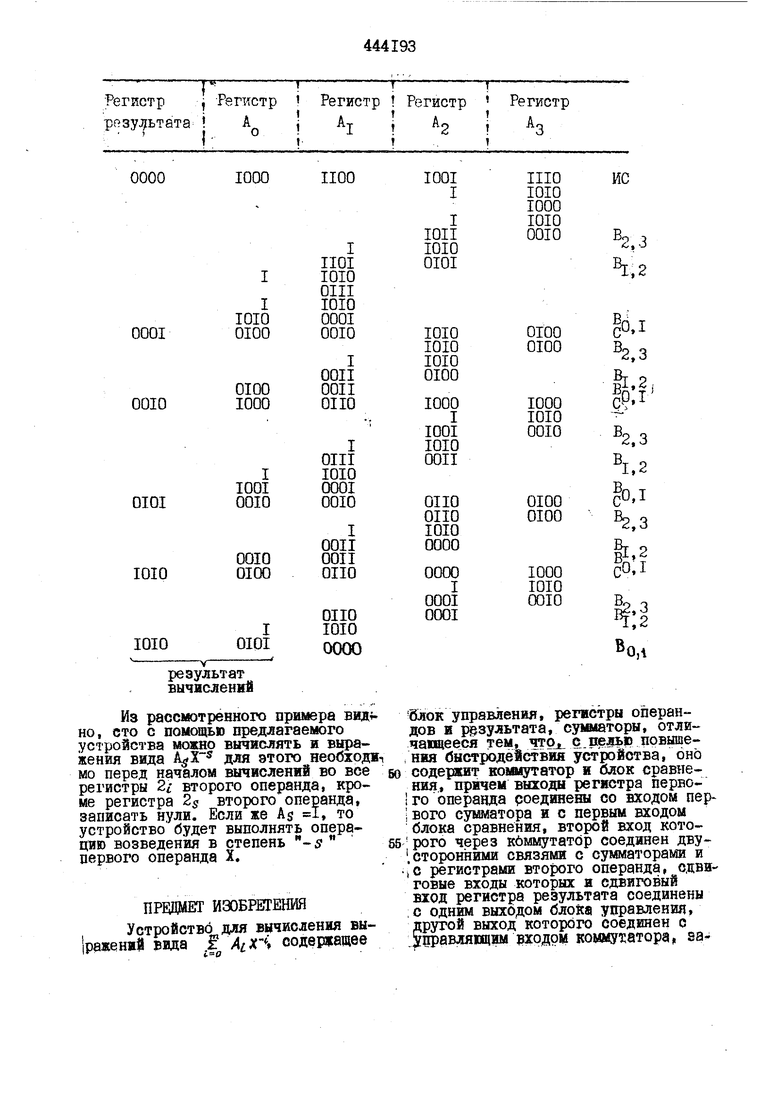

На чертеже приведена блок-схема предлагаемого устройства.

Устройство для вычисления выражений вида AiX содержит регистр I первого операнда, регист ры 2от2„ второго операнда, регистр

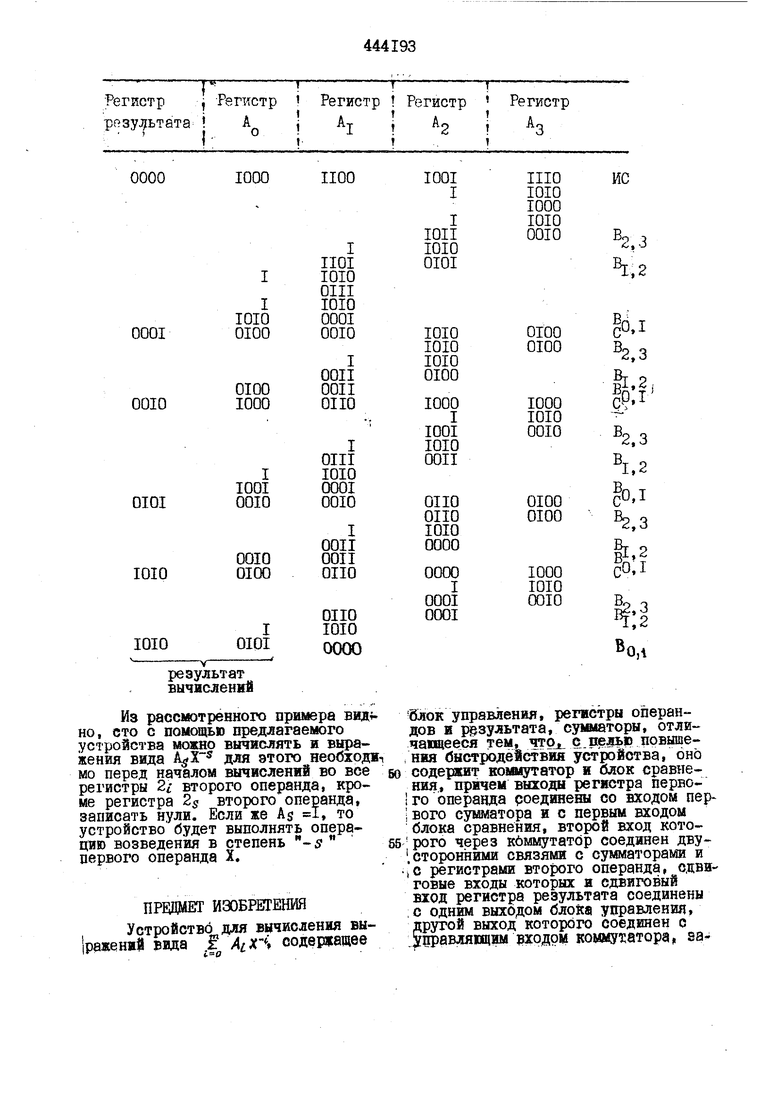

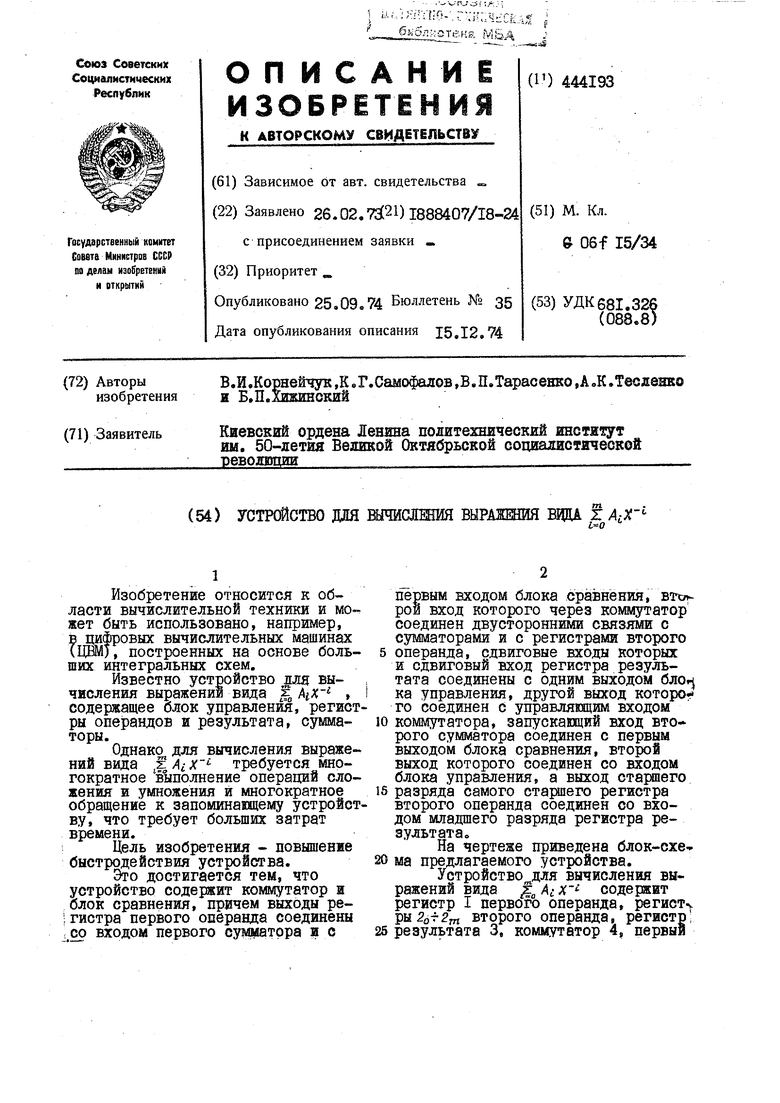

25 результата 3, коммутатор 4, первый сумматор 5, второй сумматор 6, блок сравнения 7, блок управления 8. В регистр I первого операнда помещается операнд Х, в регистры 2 второго операнда - операнды AL ( (L o,.. ,гп) , причем число регистров 2 второго операнда должно быть т JT 1. В результате вычислений целая часть результата будет находиться в регистре результата 3 а дробная, вычисленная с точностьго до п двоичных знаков (. п. разрядность регистров I и 2), будет находиться в самом старшем из регистров 2 второго операнда. Работа предлагаемого устройства состоит в следующем. С началом операции блок управления 8 вырабатывает сигнал, устанавливающий коммутатор 4 в состояние, при котором на его выходах появляется содержимое/4 -7 и Am регистров 2«-7 и 2дг второго операнда. Код операнда / поступает на блок сравнения кодов 7, где сравнивается с кодом операнда X. Если , то по сигналу с выхода блока сравнения 7 на первый сумматор 5 передается код . .. „ .., ,, и дополнительный код X, Вследствие этого на выходах первого сумматора 5 формируется разность Атп-х которая через коммутатор 4, записывается в регистр 2т второго операнда. Одновременно к младшему разряду содержимого регистра 2т-1 второго операнда с помощью второго сумматора 6 прибавляется единица. После этого опять происходот сравнение содержимого . регистра 2т второго операнда и со.держимого X регистра I первого операнда, и описанный процесс повторяется до тех пор, пока содержимое Pi т регистра 2тп второго операнда не станет меньше содержимого X ре.гистра I первого операнда. Если же A..t то по сигналу с блока сравнения 7 блок упраЕления 8 переводит коммутатор 4 в следущее состояние, при котором на его выходах появляются коды вторых оперен-, дов и Аттг-г- С ЭТИМИ кодами выполняются аналогичные операции и т.д. Когда комм7/татор 4 переключается в последнее состояние, соответствующее появлению кодов второго операнда АО и Af на его выходах, и .содержимое регистра 2i второго операнда становится меньше операнда X, то блок управления 8 вырабатывает сигнал, по которому содержимое всех регистров 2 второго операнда и регистра результата 3 сдвигается влево на один разряд. При этом старший разряд регистра 2о второго oneранда переписывается в регистр результата 3. После этого блок управления 8 возвращает коммутатор 4 в исходное состояние, соответствущее выполнению операций над содержимым kfrzrj и Am регистров 2т-1 И 2тп второго операнда. Далее работа устройства происходит аналогично. Процесс вычисления результата заканчивается после выполнения сех операций, предшествукшшх п, сдвигу. П Р И М Е Р. Пустьтп 3, , АО 8, А 12, Аг 9, АЗ 14. Для этих значений X и At процесс вычтлслекк можно проиллюстрировать следушцеЙ таблицей состояний регистров 2i. второго операнда устройства, где ИС -исходное состояние; Щ-1, результат выполнения описанных выше операций над содержимым регистров и 2j (/ 1,2,3) второго операнда; С-результат операщга сдвига. Разности А;, -X формируются путем сложения прямого кода Aj и дополнительного кода X (в данном случае дополнительный код X равен. шЮ)....

Из рассмотренного примера ввд4но, сто с помощью предлагаелюго устройства можно вычислять и выражения вида для этого необжоджМО перед началом вычислении во все регистры 2i второго операнда, кроме регистра 2 второго операнда, записать нули. Если же Ag 1, то устройство будет выполнять операцию возведения в степень -s- первого операнда X.

ПРЕдаЕТ ИЗОБРЕТЕНИЯ Устройство для вычисления выIpaxeHHfl вида Д ХгХЧ содержащее

блок управления, регистры операндов и результата, сушюторы, отличающееся тем, vfOjL с релью повышения быстродейстзвия устройства, оно 60 содержит комугутатор и блок сравнения, причем выходы регистра перво го операнда роединены со входом пер вого сумматора и с первым входом блока сравнения, второй вход кото55рого через кбммутатор соединен двусторонними связями с сумматорами и .с регистрами второго операнда, сдвиговые входы которых и СДВИГОВЫЙ

вход регистра результата соединены с одним выходом блока управления, другой выход которого соединен о 5правляпцр1 входом коммутатора, sa

пускающий вход второго сумляатора соединен с первым вьосодом блока сравнения, второй выход которого соединен со входом блока управления.

а выход старшего разряда самого старпего регистра второго операнда

соединен со входом младшего разряда регистра результата.

| название | год | авторы | номер документа |

|---|---|---|---|

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Вычислительное устройство | 1988 |

|

SU1532917A1 |

| Дифференцирующее устройство | 1974 |

|

SU516041A1 |

| Вычислительное устройство | 1983 |

|

SU1164696A1 |

| Устройство для реализации алгоритма Волдера | 1983 |

|

SU1115049A1 |

| Устройство для одновременного вычисления двух многочленов | 1980 |

|

SU926650A1 |

| Устройство для извлечения корня -ой степени | 1973 |

|

SU491946A1 |

| Устройство для вычисления функций в модулярном коде | 1985 |

|

SU1278839A1 |

| Конвейерное устройство для вычисления функции Y=е @ | 1981 |

|

SU962927A1 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

Авторы

Даты

1974-09-25—Публикация

1973-02-26—Подача