матора 2n-i связан со входом коммутатора 5, выходы которого подключены ко входам регистра 4 результата.

Выходы регистра 4 через коммутатор 6 подсоединены ко входам всех сумматоров к ко входам сдвигового регистра 8 начального коэффициента. Выходы регистра 3 аргумента подключены ко входам сумматора 2n-i. Выход младшего разряда сдвигового регистра 8 начального коэффициента подключен к цепи приема кода сумматора 2i из коммутатора, 6 и к цепи выдачи кода сдвигового регистра 8. Выходы блока управления 7 связаны со входами цепи выдачи обратного кода регистра 3 аргумента, со входами коммутаторов 5 и 6, с цепями сдвига всех сдвиговых регистров и со входами цепи выдачи кода сдвигового регистра 1„-1.

Работу устройства рассмотрим на примере

5

вычисления z/ )/0,235.

Перед началом работы аргумент 0,235 заносится в регистр 3 аргумента. Количество разрядов т в регистрах и сумматорах предлагаемого устройства выбирают, исходя из требуемой точности вычисления искомого значения корня. В данном примере положим для

определенности т 5. Вычисление У 0,235

длится т циклов. В начале первого цикла схема управления

7через коммутатор 6 записывает единицу в первый справа после запятой разряд регистра

8начального коэффициента, т. е. заносит код 0,10000. Такой же код будет на выходе коммутатора 6 в течение всего первого цикла. В первом такте первого цикла происходит одновременное суммирование на всех сумматорах таким образом, что на сумматоре 2 складывается содержимое сдвигового регистра Ij с кодом на выходе коммутатора 6 (если на выходе младшего разряда сумматора единица или с нулем, когда на выходе младшего разряда сумматора 2i-i - онуль).

Сумматор 2i и регистр h управляются выходом младшего разряда сдвигового регистра 8 начального коэффициента.

Первый такт заканчивается сдвигом вправо на один разряд содержимого всех сдвиговых регистров. Последующие такты аналогичны описанному.

После окончания всех тактов (в обшем случае т(п-1) тактов) на сумматор 2„-1 подается содержимое регистра 3 аргумента в дополнительном коде и содержимое сдвигового регистра ITI-I. Если результат при этом отрицательный, то в первый справа после запятой разряд регистра 4 результата через коммутатор 5 записывается единица, если же результат положительный - то записывается нуль. В данном примере на регистре 4 будет записан код 0,10000. Содержимое регистра устанавливается на нуль. Этим заканчивается первый цикл вычислений.

Во втором цикле на сдвиговый регистр 8 через коммутатор 6 подается содержимое регистра 4 результата. Во второй (в /и-м цикле в т-й, где , 2, ...5) справа после запятой разряд сдвигового регистра 8 записывается единица, в данном примере будет записан код 0,11000).

После этого следуют такты (в обш,ем случае т(п-1) тактов), аналогичные описанным выше. После окончания второго цикла содержимое регистра 4 имеет вид 0,10000 и т. д. до окончания пятого цикла, когда в регистре 4 результата будет записан результат вычисле5

ния К0,235.

На предлагаемом устройстве можно вычислять корень из чисел, больших единицы. В

/I

этом случае производят вычисления ,CKS.

Х Х-2- 1, аналогичным способом, что и

при , а запятую в регистре 4 результата

по окончании вычислений сдвигают вправо на

-разрядов, где k выбирают кратным числу п. Содержимое регистров в пятом цикле при

5

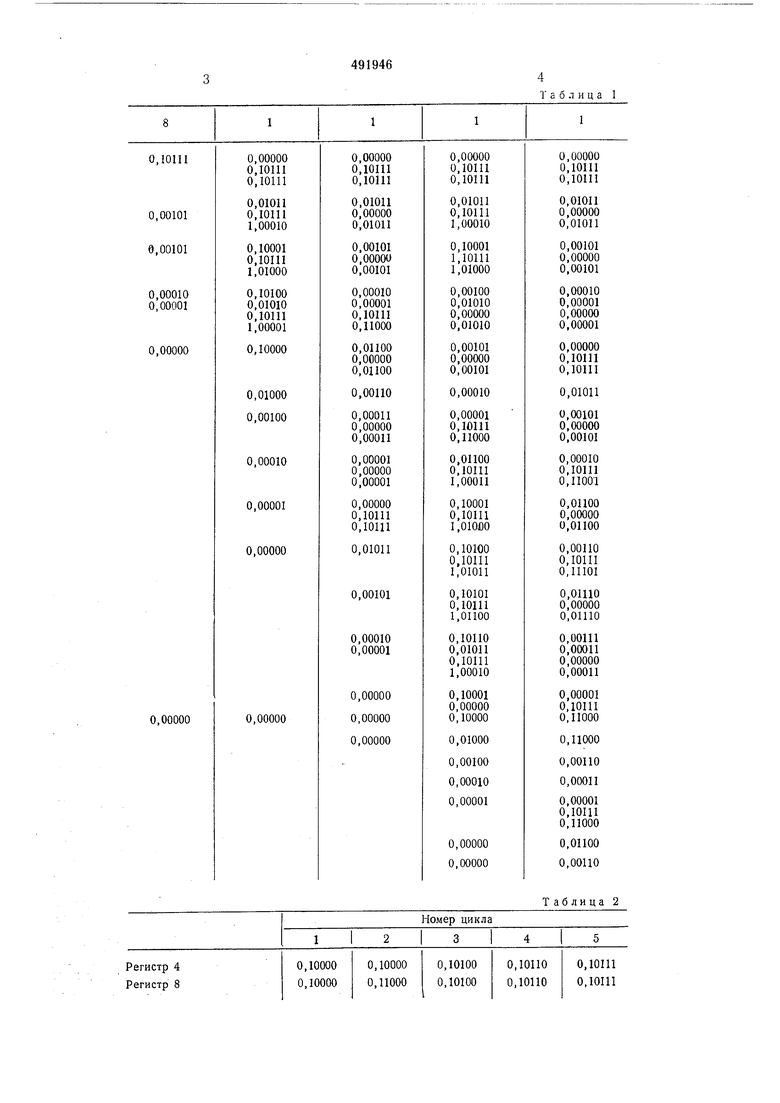

вычислении |/0,235 иллюстрирует таблица 1, где обозначены состояния сдвиговых регистров и коды, подаваемые на сумматоры 2, в каждом такте вычислений.

В таблице 2 записаны состояния регистра 4 результата в конце каждого цикла и состояния сдвигового регистра 8 начального коэффициента в начале каждого цикла.

После выполнения всех тактов 5-го цикла

выполняется операция 1,11001.

+0,00110 1,11111

Результат отрицательный и поэтому в пятой справа после запятой разряд регистра 4 результата записываем единицу.

Код в регистре 4 есть результат выполне5

ния операции у0,,101 и 0,719.

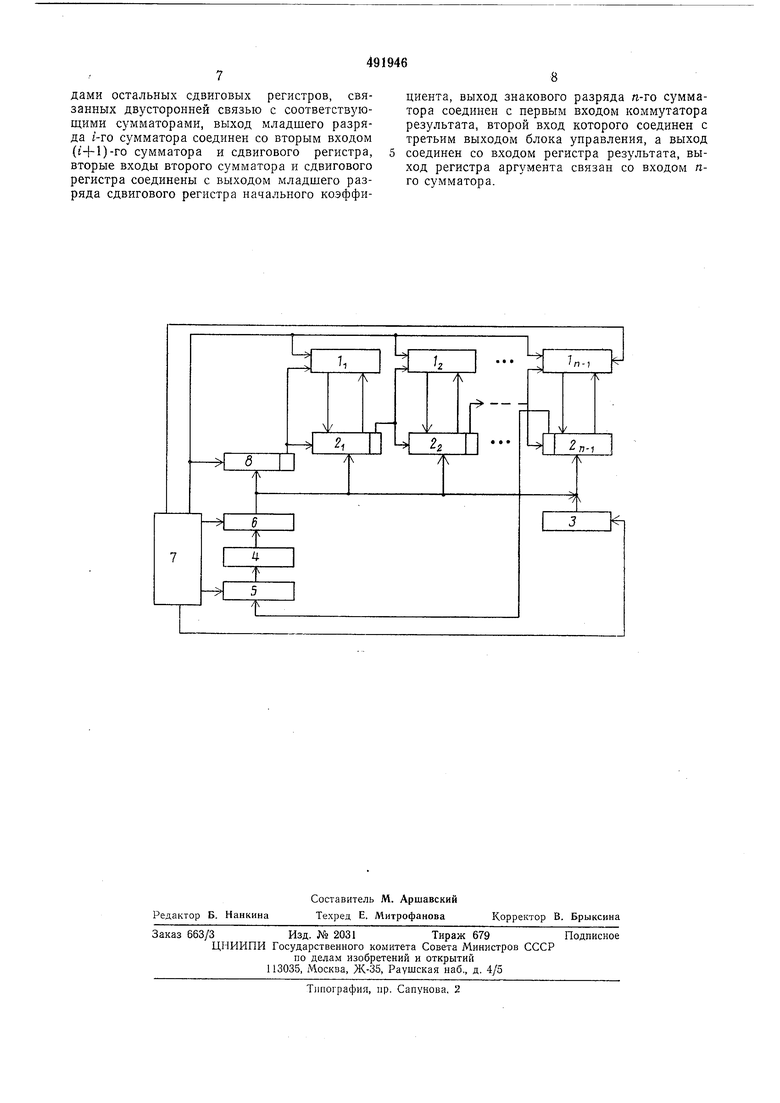

Формула изобретения Устройство для извлечения корня «-и степени, содержаш,ее сдвиговые регистры, сумматор, регистр аргумента, регистр результата и блок управления, связанный с регистрами и сумматором, отличающееся тем, что, с целью расширения сдвиговых функциональных возможностей, оно содержит (п-1) сдвиговых

регистров, (п-1) сумматоров, сдвиговый регистр начального коэффициента, коммутатор результата и коммутатор младшего коэффициента, первый вход которого соединен с первым выходом блока управления, второй

вход - с выходом регистра результата, а выход соединен с первым входом сдвигового регистра начального коэффициента и всех сумматоров, второй вход сдвигового регистра начального коэффициента соединен со вторым

выходом блока управления и с первыми входами остальных сдвиговых регистров, связанных двусторонней связью с соответств ющими сумматорами, выход младшего разряда г-го сумматора соединен со вторым входом ()-го сумматора и сдвигового регистра, вторые входы второго сумматора и сдвигового регистра соединены с выходом младшего разряда сдвигового регистра начального коэффициента, выход знакового разряда л-го сумматора соединен с первым входом коммутатора результата, второй вход которого соединен с третьим выходом блока унравления, а выход соединен со входом регистра результата, выход регистра аргумента связан со входом пго сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения корня п-й степени | 1979 |

|

SU883898A1 |

| Устройство для решения дифференциальных уравлений | 1974 |

|

SU526905A1 |

| Устройство для деления чисел с фиксированной запятой | 1982 |

|

SU1059570A1 |

| Устройство для вычисления обратной величины | 1976 |

|

SU732861A1 |

| Устройство для извлечения корня @ -й степени | 1984 |

|

SU1223225A2 |

| Устройство для вычисления квадратного корня | 1987 |

|

SU1481753A1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1287175A1 |

| Устройство для быстрого преобразования Фурье | 1988 |

|

SU1524066A1 |

| Устройство для деления | 1986 |

|

SU1425657A1 |

| Устройство для вычисления функций в модулярном коде | 1985 |

|

SU1278839A1 |

Авторы

Даты

1975-11-15—Публикация

1973-10-15—Подача