(54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ДВОИЧНЫХ ЧИСЕЛ

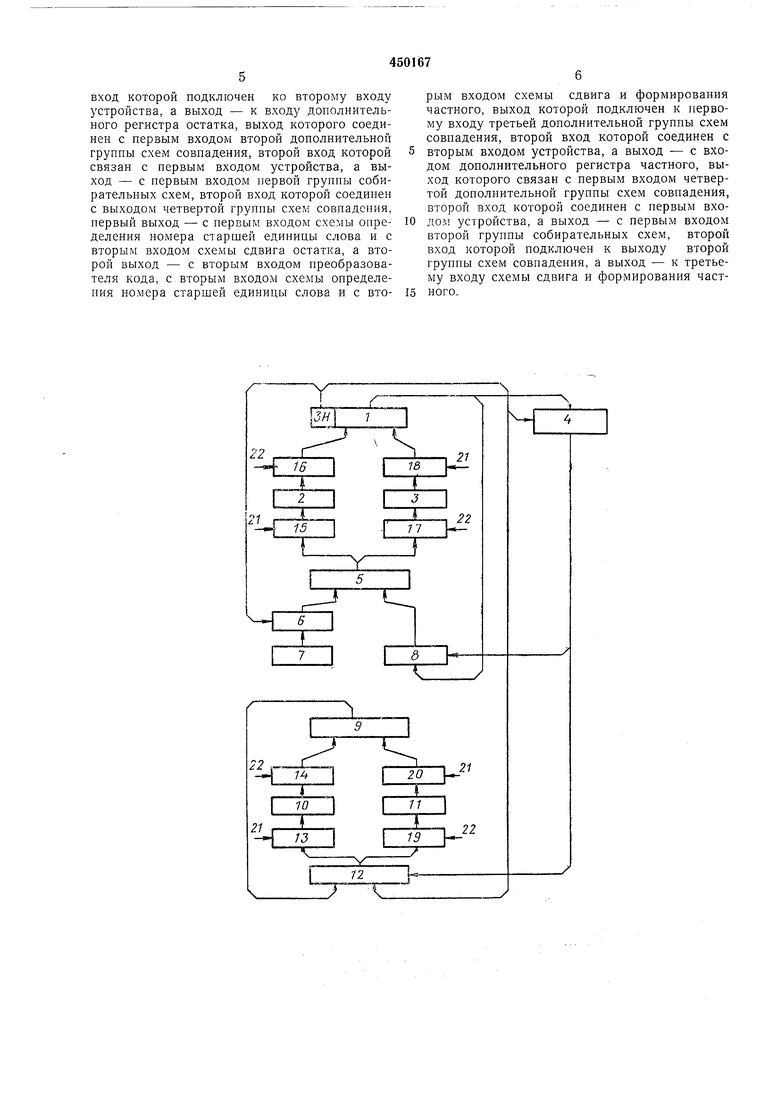

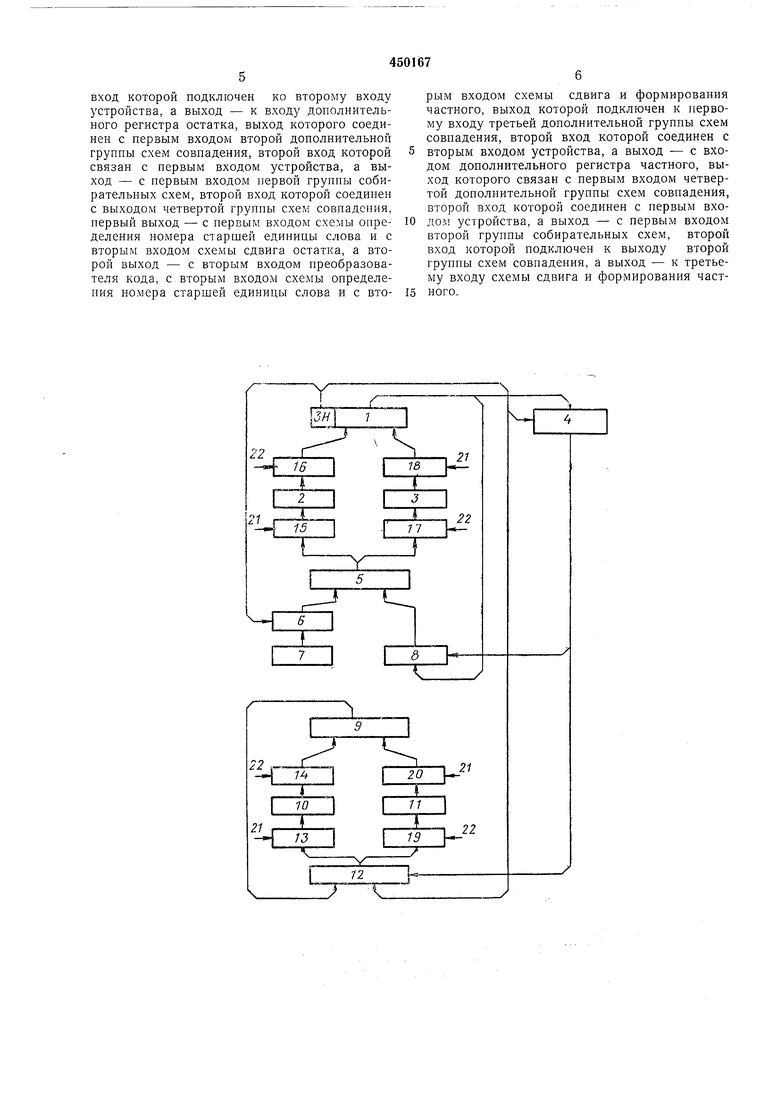

падения 15, четвертую группу схем совпадения 16, первую дополнительную группу схем совпадения 17, вторую дополнительную группу схем совпадения 18, третью дополнительную группу схем совпадения 19, четвертую дополнительную группу схем совпадения 20. Первый вход устройства 21 и второй вход устройства 22.

Устройство работает следующим образом.

Исходными числами для деления в устройстве являются нормализованный делитель и делимое либо в нормальной форме, либо с одним нулем между разрядом знака и старшей значащей единицей.

После выполнения (t-1)-го цикла работы устройство находится в следующем состоянии: регистр остатка 2 содержит обратный или дополнительный код последнего остатка (или делимое), регистр частного 10 содержит частное, которое предшествует остатку, находящемуся на регистре остатка 2 (в начале операции нули) . Состояние остальных элементов не существенно. По сигналу выполнения f-ro цикла, который подается на второй вход устройства 22, остаток с регистра остатка 2 через четвертую группу схем совпадения 16 и первую группу собирательных схем 1 передается на вход схемы определения номера старшей единицы слова 4 и схему сдвига остатка 8. Одновременно разряд знака остатка с выхода знакового разряда первой группы собирательных схем 1 поступает на управление преобразователем кода 6, управление схемой определения номера старшей единицы слова 4 и на вход схемы сдвига и формирования частного 12. Схема 4 определения номера старшей единицы слова, в зависимости от знака, преобразует остаток в прямой код и подсчитывает номер старшей единицы в коде остатка, т. е. количество нулей между знаковым разрядом и старшей значащей единицей. Результат подсчета, равный количеству нулей, поступает на управление схемой сдвига остатка 8 и схемой сдвига и формирования частного 12. Остаток, поступивший на схему сдвига остатка 8, сдвигается влево на количество нулей в нем, т. е. нормализуется, и поступает на второй вход сумматора 5. На первый вход сумматора 5 через преобразователь кода 6 с регистра делителя 7, в соответствии со знаком остатка, поступает код делителя. Для положительного остатка код делителя-инверсный, а для отрицательного остатка код делителя-прямой. Результат сложения есть i-ый остаток, который с выхода сумматора 5 через первую дополнительную группу схем совпадения 17 фиксируется на дополнительном регистре остатка 3.

Одновременно последнее частное с выхода регистра частного 10 через вторую группу схем совпадения 14, открытую по сигналу на втором входе устройства 22, и через вторую группу собирательных схем 9 поступает на вход схемы сдвига и формирования частного 12. На этой схеме выполняется сдвиг частного влево на количество нулей в остатке, а освободившиеся позиции частного заполняются либо числом 100... О, если знак (i-1)-го ос15 татка «плюс, либо 011... О, если знак

(t-1)-го остатка «минус. Здесь k - количество нулей, вычисленное схемой 4 определения

номера старшей единицы слова. Результат - частное, соответствующее i-ому остатку, через третью: дополнительную группу схем совпадения 19 фиксируется на дополнительном регистре частного 11.

По сигналу выполнения (г+1)-го цикла, который поступает на первый вход устройства 21, выполняются действия, аналогичные описанным выше, с той лишь разницей, что исходный остаток для работы есть г-ый остаток,

находящийся на дополнительном регистре остатка 3 частное, соответствующее f-ому остатку, находится на дополнительном регистре частного 11. Результат (1-{-)-Ъ1т остаток будет фиксироваться на регистре остатка 2, а частное, соответствующее (t+l)-My остатку, - на регистре частного 10.

Таким образом, благодаря предлагаемым соединениям узлов, каждый такт используется в качестве рабочего, и этот же такт является подготовительным для следующего. Кроме того, принятый алгоритм позволяет определить по данному остатку в среднем несколько разрядов частного. Вследствие этого скорость работы устройства значительно увеличивается.

Предмет изобретения

Устройство для деления двоичных чисел,

содержащее регистр делителя, выход которого соединен с первым входом нреобразователя кода, выход которого подключен к первому входу сумматора, второй вход которого соединен с выходом схемы сдвига остатка, первый

вход которого связан с выходом схемы определения номера старщей единицы слова и с первым входом схемы сдвига и формирования частного, выход которой соединен с первым входом первой группы схем совпадения, второй вход которой подключен к первому входу устройства, а выход - к входу регистра частного, выход которого связан с первым входом второй группы схем совпадения, второй вход которой соединен с вторым входом устройства, причем выход сумматора соединен с первым входом третьей группы схем совпадения, второй вход которой подключен к первому; входу устройства, а выход - к входу регистра остатка, выход которого связан с первым

входом четвертой группы схем совпадения, второй вход которой соединен с вторым входом устройства, отличающееся тем, что, с целью повышения быстродействия, выход сумматора соединен с первым входом первой дополнительной группы схем совпадения, второй

вход которой подключен ко второму входу устройства, а выход - к входу дополнительного регистра остатка, выход которого соединен с первым входом второй дополнительной группы схем совпадения, второй вход которой связан с первым входом устройства, а выход - с первым входом первой группы собирательных схем, второй вход которой соединен с выходом четвертой группы схем совпадспия, первый выход - с первым входом схемы определения номера старшей единипы слова и с вторым входом схемы сдвига остатка, а второй выход - с вторым входом преобразователя кода, с вторым входом схемы определения номера старшей единицы слова и с вторым входом схемы сдвига и формирования частного, выход которой подключен к первому входу третьей дополнительной группы схем совпадения, второй вход которой соединен с вторым входом устройства, а выход - с входом дополнительного регистра частного, выход которого связан с первым входом четвертой дополнительной группы схем совпадения, второй вход которой соединен с первым входом устройства, а выход - с первым входом второй группы собирательных схем, второй вход которой подключен к выходу второй группы схем совпадения, а выход - к третьему входу схемы сдвига и формирования частного.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления двоичных чисел | 1976 |

|

SU660046A2 |

| Устройство для деления двоичных чисел | 1987 |

|

SU1432508A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1992 |

|

RU2035064C1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Устройство для деления двоичных чисел | 1988 |

|

SU1617437A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКТИРОВКИ ДВОИЧНЫХ АРИФМЕТИЧЕСКИХ КОДОВ | 1972 |

|

SU328464A1 |

| БКБЛЙОТЕК.Д | 1970 |

|

SU273520A1 |

| Устройство для деления десятичных чисел | 1982 |

|

SU1048473A1 |

| Устройство для деления двоичных чисел | 1980 |

|

SU1048472A1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

Т

i 7/7

22 -,

ЧИ

11Г

-

21

18

21 ,

15

22

77

Авторы

Даты

1974-11-15—Публикация

1972-11-30—Подача