Изобретение относится к автоматике и вычислительной технике и может использоваться для счета электрических имнульсов.

Известен счетный триггер, содержании двустабильную схему на туннельном диоде, транзистор сброса с токозадающим резистором в цепи базы.

Цель изобретения-повышение быстроде ствия и надежности триггера.

Эта цель достигается тем, что предлагаемый счетный триггер содержит развязываюндий диод, диод с накоплением заряда, малоннерцнонный диод и дополнительный туннельный диод, цри этом вход триггера через диод с накоплеиием заряда нодключен к базе транзнстора сброса и через развязывающий диод - к его коллектору, к базе транзистора сброса подключен анодом дополнительный туннельный диод, и между базой и коллектором транзистора сброса включен малоинерциоппый диод, например диод Шоттки.

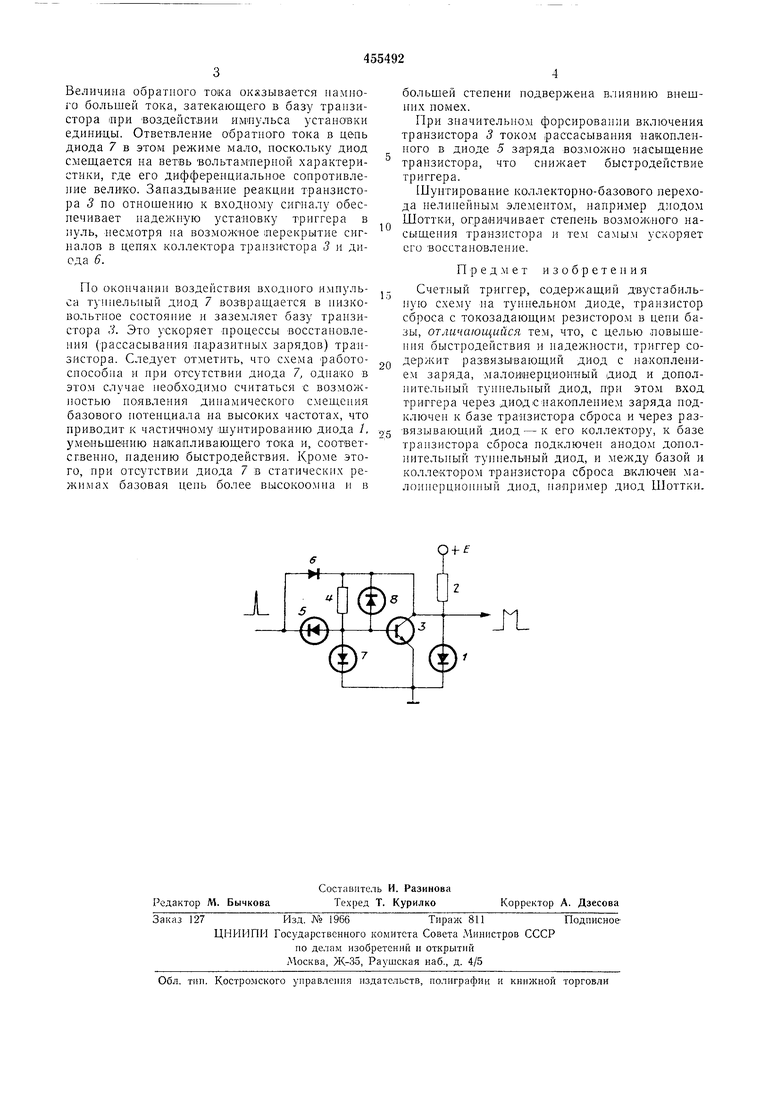

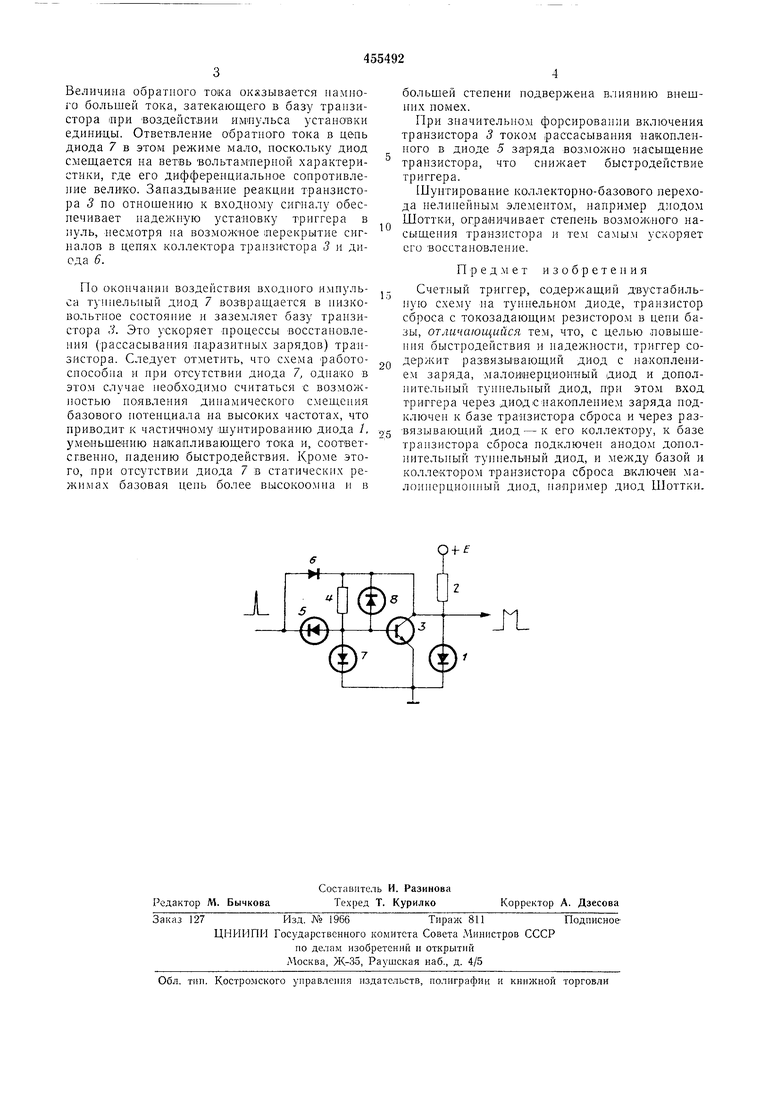

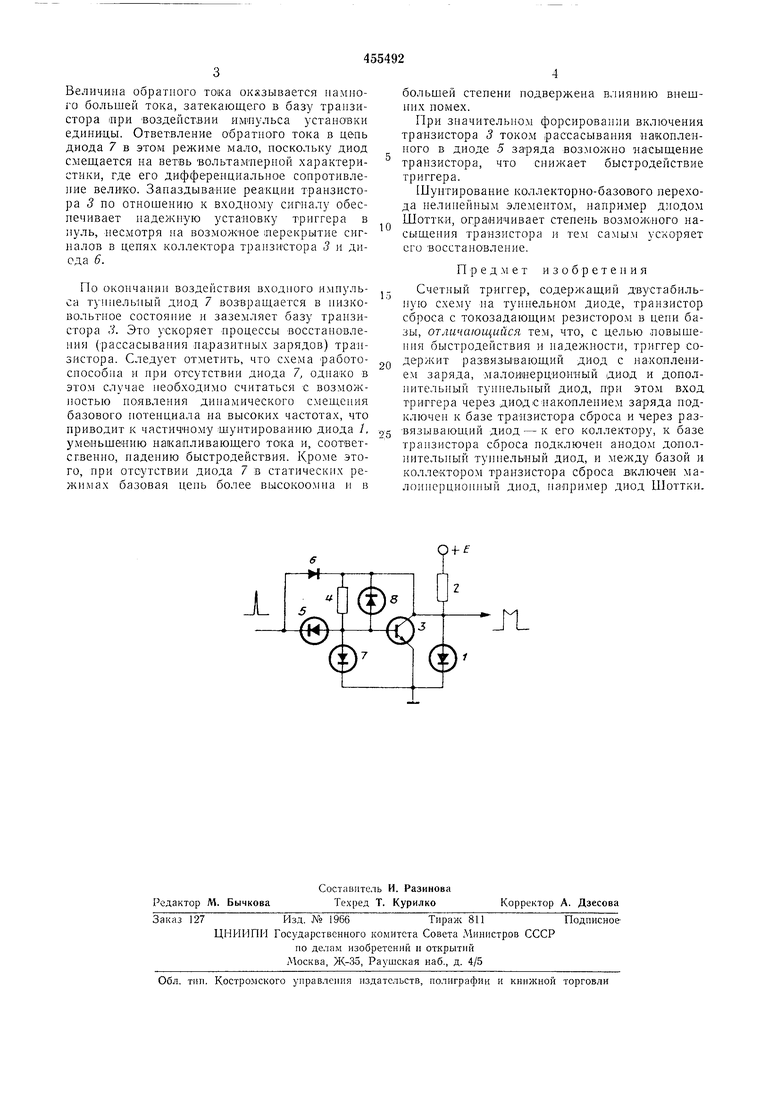

Иа чертеже приведена принципнальная схема счетного триггера.

Иривцвпиальная схема триггера содержит двустабильную схему на туциельном диоде / и резисторе 2, транзистор 3 сброса, токозадающий резистор 4 и диод 5 с накоплением заряда. Установка схемы в единичное состояние осуществляется через развязывающий диод 6. К базе транзистора 3 сброса подключен дополнительный диод 7, а между базой и коллектором подключен малопнерционный дпод S (обращенный, либо диод Шотткн).

Предположим, что начальное состояние 5 триггера - нулевое, т. е. диод / находится в низковольтном режиме. Вследствие включения дополнительного туннельного диода 7 перед воздействием входного сигнала база транзистора 3 заземлена через низкоомное сопротивление ветви диода 7. Воздействующий по входу имнульс положительной полярности через развязывающий дпод 6 переводит туннельный диод / в высоковольтное состояние. Затекающий при этом в базу управляющего

5 тра 1зистора 3 ток ограничен резнстором и з сравнительно широком диапазоне амплитуд входных импульсов не вызывает включение транзистора. В фазе хра-нення единичного состояния (диод / в высоковольтном режиме)

0 через резистор 4 -протекает ток. Белнчина тока резистора 4 выбирается большей пикового тока диода 7, и осиовная часть тока ответ1вляется в цепь диода 5. В базе диода 5 накаллиаается заряд неосновных носителей, величина

5 которого определяется протекаемым током и параметрами диода.

При повторном воздействии входного импульса накопленный заряд рассасывается, обратным токсм диода 5 включается транзистор

0 3 и устанавливает диод / в нулевое состояние.

Величина обратного тока оклзывается намного большей тока, затекающего в базу транзистора при воздействии им пульса установки единицы. Ответвление обратного тока в день диода 7 в этом режиме мало, поскольку диод смещается на ветвь вольтамперной характеристики, где его дифференциальное сонротивлелие велико. Запаздывание реакции транзистора 3 по отношению к входному сигналу обеспечивает надежную установку триггера в пуль, несмотря на возмолсное иерекрытие сигпалов в цепях коллектора транзистора 3 и диода 6.

По окончании воздействия входного импульса туннельиый диод 7 возвращаегся в низковольтное состояние и заземляет базу транзистора 3. Это ускоряет нроцессы восстановления (рассасывания иа:разитных зарядов) траизистора. Следует отметить, что схема работоспособна и при отсутствии диода 7, одпако в этом случае необходимо считаться с возможностью нолБления динамического смещения базового потенциала на высоких частотах, что приводит к частичному шунтированию диода /, уменьшению накапливающего тока и, соответсгвеино, надению быстродействия. Кроме этого, ири отсутствии диода 7 в статических режимах базовая цеиь более высокоомна и в

большей степени подвержена влиянию внешних иомех.

При значительном форсировании включения транзистора 3 током рассасывания накоплениого в диоде 5 заряда возможно насыщение транзистора, что снижает быстродействие триггера.

Шунтирование коллекторно-базового перехода нелинейным элементом, например диодом Шоттки, ограничивает степень возмож1ного насыщения транзистора и тем самым ускоряет его восстаиовлеиие.

Предмет изобретения

Счетный триггер, содержащий двустабильную схему на туннельном диоде, транзистор сброса с токозадающим резистором в цепи базы, отличающийся тем, что, с целью повышения быстродействия и надежности, триггер содер 1сит развязывающий диод с иакопленцем заряда, .малоинерционный диод и дополнительный туннельный диод, при этом вход триггера через диодснакоилением заряда нодключен к базе транзистора сброса и через развязывающий диод - к его коллектору, к базе транзистора сброса подключеи анодом доиолнительный туннельный диод, и между базой и коллектором транзистора сброса включен малоинерциониый диод, например диод Шоттки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент | 1974 |

|

SU572930A2 |

| ТРИГГЕР СО СЧЕТНЫМ ВХОДОМ | 1968 |

|

SU219621A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «НЕ-ИЛИ» | 1971 |

|

SU305588A1 |

| Логическая схема "или-и-не" | 1974 |

|

SU510784A1 |

| Управляемый триггер | 1974 |

|

SU541290A1 |

| Логическая схема или-и-не | 1973 |

|

SU474109A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ «ИСКЛЮЧАЮЩЕЕ ИЛИ» | 2022 |

|

RU2795286C1 |

| УСТРОЙСТВО ЗАДЕРЖКИ ИМПУЛЬСОВ | 1972 |

|

SU432678A1 |

| Логический вентиль | 1980 |

|

SU940308A1 |

| РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА | 1973 |

|

SU389548A1 |

Авторы

Даты

1974-12-30—Публикация

1973-02-23—Подача