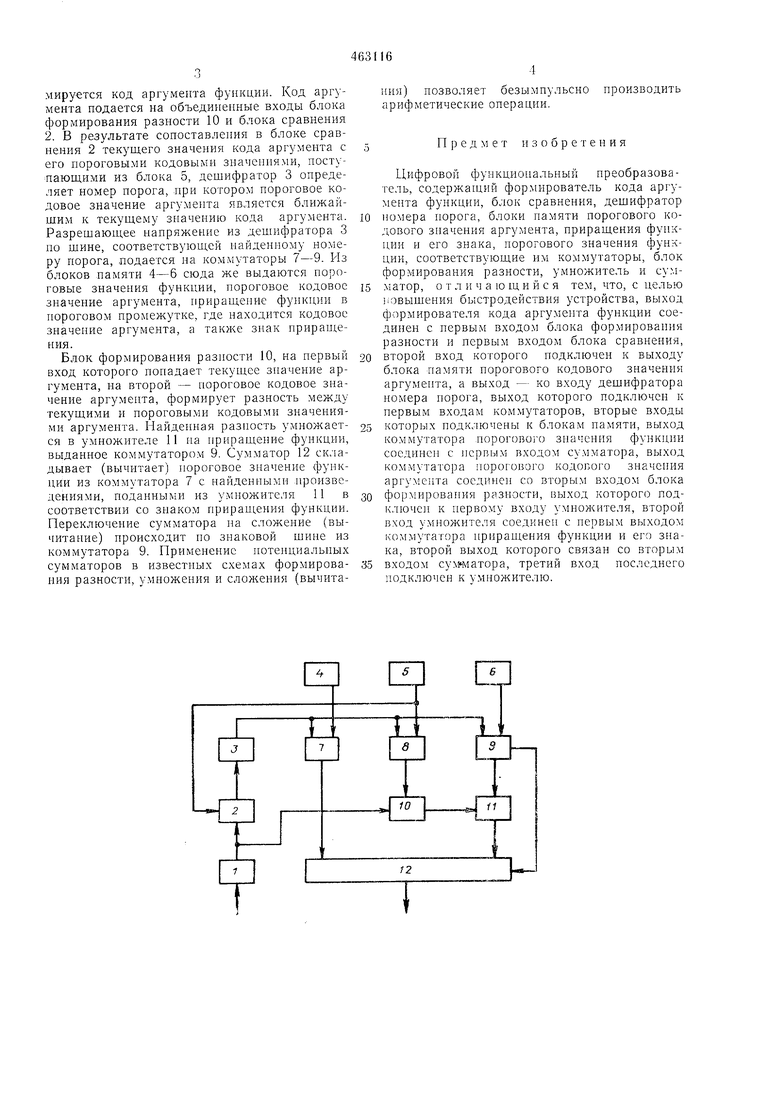

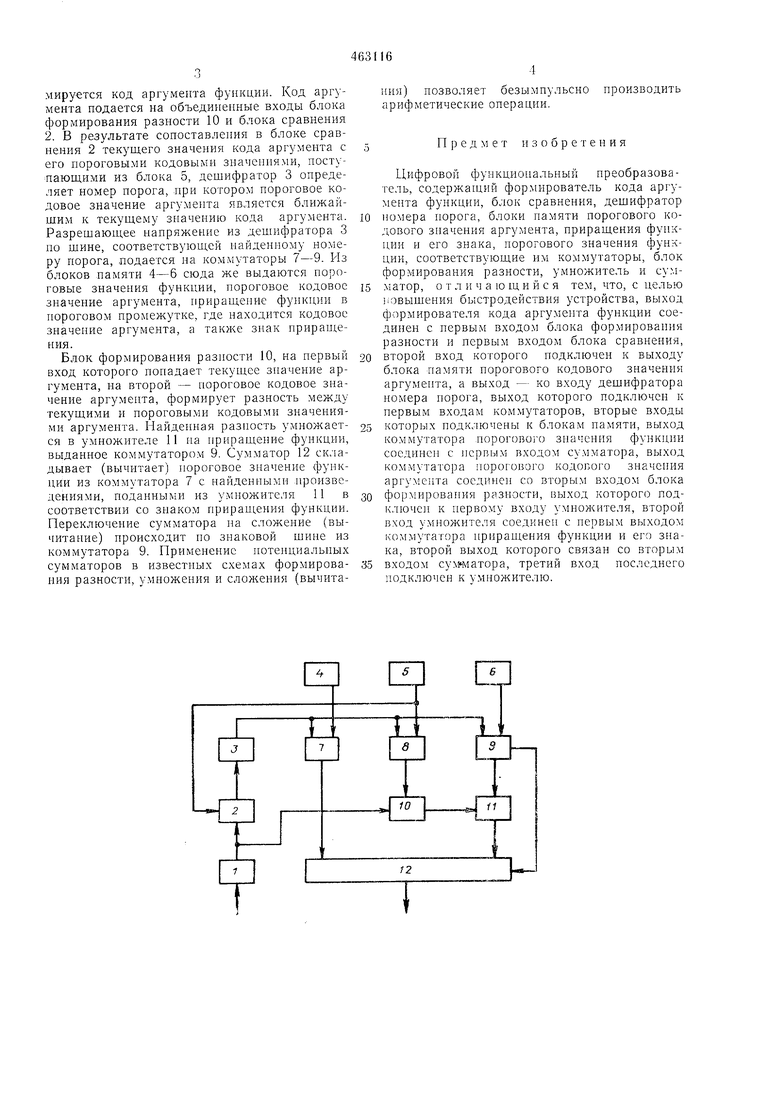

код аргумента функции. Код аргумента подается на объединенные входы блока формирования разности 10 и блока сравнения 2, В результате сопоставления в блоке сравнения 2 текущего значения кода аргумента с его пороговыми кодовыми значениями, посту пающими из блока 5, дешифратор 3 определяет номер порога, при котором пороговое кодовое значение аргумента является ближайшим к текуидему значению кода аргумента. Разрешающее напряжение из деши4)ратора 3 по шине, соответствующей найденному номеру порога, подается на коммутаторы 7-9. Из блоков памяти 4-6 сюда же выдаются пороговые значения функции, пороговое кодовое значение аргумента, приращеиие функции в пороговом промежутке, где находится кодовое значение аргумента, а также знак прирап ения.

Блок формирования разности 10, на первый вход которого попадает текущее значение аргумента, на второй - нороговое кодовое значение аргумента, формирует разность между текущими и пороговыми кодовыми значениями аргумента. Найденная разность умножается в умножителе 11 на нриращение функции, выданное коммутатором 9. Сумматор 12 складывает (вычнтает) пороговое значение функции из коммутатора 7 с найденными произведениями, поданными из умножителя 11 в соответствии со знаком приращения функции. Переключение сумматора на сложение (вычитание) происходит по знаковой шине из коммутатора 9. Применение потенциальных сумматоров в известных схемах формирования разности, у.множения и сложения (вычитания) позволяет безымпульсно производить арифметические операции.

Предмет и з о б р е т е н и я

Цифровой функциональный преобразователь, содержащий формирователь кода аргумента функции, блок сравнения, дешифратор

номера порога, блоки памяти порогового кодового значения аргумента, приращения функции н его знака, порогового значения функции, соответствующие им ко.ммутаторы, блок формирования разности, умножитель и су.мматор, отличающийся тем, что, с целью 1 повышения быстродействия устройства, выход формирователя кода аргумеита функции соединен с первым входом блока формировання разности и первым входом блока сравнения,

второй вход которого нодключен к выходу блока памяти порогового кодового значения аргумента, а выход - ко входу дешифратора номера норога, выход которого подключен к первым входам коммутаторов, вторые входы

которых подключены к блокам памятн, выход коммутатора норогового значения функции соединен с первым входом сумматора, выход коммутатора порогового кодового значения аргумента соединен со вторым входом блока

формирования разности, выход которого подключен к первому входу умножителя, второй вход умножителя соединен с первым выходом коммутатора приращения функции и его знака, второй выход которого связан со вторым

входом сумматора, третий вход последнего подключен к у.множителю.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой генератор спектра фурье | 1973 |

|

SU446063A1 |

| Цифровой кусочно-линейный аппроксиматор | 1973 |

|

SU549818A1 |

| Цифровой гармонический анализатор | 1973 |

|

SU474810A1 |

| Аналого-цифровое устройство для вычисления полиномиальной функции | 1985 |

|

SU1262530A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ ДЛЯ АДАПТИВНЫХ АДРЕСНЫХ СИСТЕМ | 1979 |

|

SU1840440A1 |

| Функциональный преобразователь | 1983 |

|

SU1107131A1 |

| Устройство корреляционной обработки широкополосных сигналов | 1989 |

|

SU1741274A2 |

| Демодулятор сигналов с фазоразностной модуляцией | 1980 |

|

SU949838A1 |

| Цифровой генератор функций | 1989 |

|

SU1663607A1 |

| Устройство для вычисления полиномиальной функции от аналогового аргумента | 1990 |

|

SU1737444A1 |

Авторы

Даты

1975-03-05—Публикация

1973-05-18—Подача