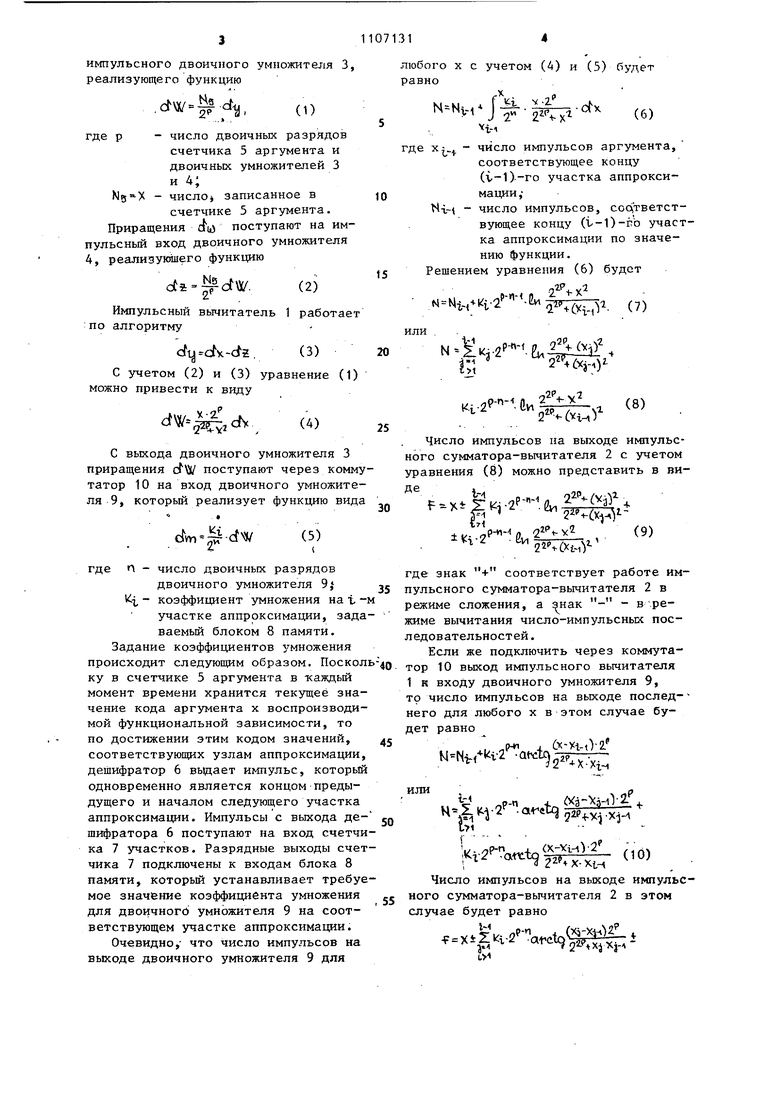

11 Изобретение относится к автоматике, вычислительной и измерительной технике и может использоваться для функционального преобразования измерительной информации. Известен цифровой функциональньй преобразователь, срдержащий схему умножения, которая состоит из двоичного счетчика, ключей, схемы свертки кода по нечетности и формирователя, схему преобразования кодов, состоящу из двоичного счетчика, запоминающего регистра, постоянного запоминающего устройства, схему пересчета, состоящую из двоично-десятичного счетчика с установочными входами и ключей выхода на магистраль, схему допусковог контроля, которая состоит из схемы сравнения кодов, логического преобра зователя, запоминающего регистра и ключей выхода на.магистраль С11. Недостатком такого преобразователя является чрезмерная сложность уст ройства при незначительном повьшени точности воспроизведения функциональ ных зависимостей. Наиболее близким по технической сущности к предлагаемому является функциональный преобразователь, содержащий три реверсивных счетчика, четыре число-импульсных двоичных умножителя, два комбинационны сумма тора-вьтчитателя кодов и две группы схем И С23. Цель изобретения - увеличение быстродействия и расширение класса решаемых задач путем обеспечения возможности вычисления разности межд линейной и кусочно-логарифмической дробно-рациональной либо кусочно-арк тангенсной дробно-рациональной, либо кусочно-арктангенсной и кусочно-линейной функциями. Поставленная цель достигается тем что в функциональный преобразователь содержащий первый, второй и третий двоичные умножители, дополнительно введены импульсные вычитатель и сумматор-вычитатель, счетчик аргумента, дешифратор участка аппроксимации, коммутатор, счетчик участков и блок памяти, причем тактовый вход преобра зователя соединен с первыми информационными входами импульсных суммато- ра-вычитателя и вычитателя, выход ко торого соединен с импульсным входом первого двоичного умножителя, выход которого подключен к импульсному вхсг 1. 2 ду второго двоичного умножителя и первому информационному входу коммутатора второй информационный вход которого соединен .с выходом второго двоичного умножителя и вторым информационным входом импульсного вычитателя, вьпсод которого соединен с третьим информационным входом коммутатора, управляющий вход и выход которого соединены соответственно с входом задания режима преобразователя и импульсным входом третьего двоичного умножителя, выход и второй вход которого соединены соответственно с вторым информационным входом импульсного сумматора-вычитателя и выходом блока памяти, вход которого соединен с выходом счетчика участков, вход которого подключен к выходу дешифратора участков аппроксимации, вход которого соединен с выходом счетчика аргумента и управляющими входами первого и второго двоичных умножи1елей, вход счетчика аргумента соединен с тактовьм входом преобразователя, вход задания режима которого соединен с управляющим входом импульсного сумматора-вычитателя. На чертеже представлена блок-схема преобразователя. Функциональный преобразователь содержит импульсный вычитатель 1, импульсный сумматор-вычитатель 2, двоичные умножители 3 и 4, счетчик 5 аргумента, дешифратор 6 участка аппроксимации, счетчик 7 участков, блок 8 памяти, двоичный умножитель 9 и коммутатор 10. Дешифратор 6 предназначен для выдачи сигнала достижения кода в счетчике 5 аргумента величины очередног© узла аппроксимации, поэтому конструктивно является вырожденным дешифратором, имеющим один выход. Преобразователь работает следующим образом. На вход умножителя 9 через коммутатор 10 подключен выход двоичного умножителя 3 (либо вход двоичного умножителя 4),-а на вход преобразователя поступает число импульсов х в виде последовательности приращений . Импульсная последовательность приращений ofu с выхода импульсного вычитателя 1 поступаем на вход числоимпульсного двоичного умножителя 3, реализующего функцию ,dW cf, (1) где р - число двоичных разрядов счетчика 5 аргумента и двоичных умножителей 3 X - число записанное в счетчике 5 аргумента. Приращения diio поступают на импульсный вход двоичного умножителя 4, реализующего функцию ota . Импульсный вычитатель 1 работае :по алгоритму oft -ofy-dz С учетом (2) и (3) уравнение (1 можно привести к виду .cfV (4) С выхода двоичного умножителя 3 приращения поступают через комм татор 10 на вход двоичного умножите ля 9, который реализует функцию вид cTml -cfW

где П - число двоичных разрядов

двоичного умножителя 9} - коэффициент умножения на t -м участке аппроксимации, задаваемый блоком 8 памяти. Задание коэффициентов умножения происходит следующим образом. Посколь ку в счетчике 5 аргумента в -каждый момент времени хранится текущее значение кода аргумента х воспроизводимой функциональной зависимости, то по достижении этим кодом значений, соответствующих узлам аппроксимации, дешифратор 6 вьщает импульс, который одновременно является концом предыдущего и началом следующего участка аппроксимации. Импульсы с выхода дешифратора 6 поступают на вход счетчика 7 участков. Разрядные выходы счетчика 7 подключены к входам блока 8 памяти, который устанавливает требуемое значение коэффициента умножения для двоичного умножителя 9 на соответствующем участке аппроксимации.

Очевидно,- что число импульсов на выходе двоичного умножителя 9 для

где знак + соответствует работе импульсного сумматора-вычитателя 2 в режиме сложения, а знак - - в .режиме вычитания число-импульсных последовательностей .

Если же подключить через коммутатор 10 выход импульсного вычитателя 1 к входу двоичного умножителя 9, то число импульсов на выходе последнего для любого х в этом случае будет равно

м.н..1,М

-ХЬ

или

.2- -«tqiS

i

bi

Ч-Хг-лУ2

(,0)

Число импульсов на выходе импульсного сумматора-вычитателя 2 в этом случае будет равно

..x.|4-2-Wt,

Ы го X с учетом (4) и (5) Рудет о (6) vt-, число импульсов аргумента, соответствующее концу (v-1)--ro участка аппроксимации , Ni- - число импульсов, ссо тветствующее концу (v-l)-rb участка аппроксимации по значению функции. ешением уравнения (6) будет ,-Ч-2---еи 1,. (7) N-.3-2- -- H tM 2 Тб«:Л222 4 ,исло импульсов па выходе импульссумматора-вычитателя 2 с учетом нения (8) можно представить в ви-x.l...-, :v-Xi-iV2 K:i-2 at :tg 22Vv (11) Для случая, когда к входу двоичного умножителя 9 окажется подключенным выход двоичного умножителя 4, соответствующие уравнения будут иметь вид N.iC|j(4-xt.1-4l- a.d9,J. - - (X-XnVSP (1 ..l-Kv2-,a,dqp Р «|асхи,.).|к, 1й.(,.,,)«,л«ъ,. (,з) Таким образом, дополнительное введение в состав преобразователя двух суммирующих счетчиков, импульсных вычитателя и сумматора-в.ычитателя, дешифратора, блока памяти коэффициентов умножения и коммутатора и одновре менное исключение из состава преобразователя трех реверсивных счетчиков, двух комбинационных сумматоров-вычитателей и одного число-импульсного двоичного умножителя позволило значительно расширить класс решаемых устройством задач за счет вычисленияфункции (9), (11) и,(13). Из этих 16 уравнений следует, что предлагаемьш преобразователь пригоден для кусочнонелинейной (разности между линейной и кусочно-логарифмической дробно-рациональной либо кусочно-арктангенсной дробно-рациоНальной, либо кусочно-арктангенсной и кусочно-линейной функциями) аппроксимации функций. Такой подход позволил реализовать известный алгоритм одного из наиболее точных методов аппроксимации нелинейных зависимостей, при котором осуществляется линеаризация кривой, представляющей собой разность между линеаризуемой кривой и желаемой линейной зависимостью. Применение этого метода наряду с повышением точности позволяет добиться значительного сокращения аппаратурных затрат за счет уменьшения количества участков аппроксимации. Кроме того, в предлагаемом преобразователе функциональное преобразование осуществляется в темпе поступления число-импульсной информации (т.е. в реальном времени), тогда как для прототипа характерен переходный процесс, по окончании которого схема приводится в состояние динамического равновесия.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1989 |

|

SU1691837A1 |

| Устройство для вычисления функций у=тGх и у=стGх | 1980 |

|

SU935950A1 |

| Устройство для вычисления функций у=aRcSINx и у=aRccoSx | 1980 |

|

SU935949A1 |

| Аппроксимирующий функциональный преобразователь | 1983 |

|

SU1160430A1 |

| Частотно-импульсный функциональный преобразователь | 1981 |

|

SU995095A1 |

| Цифровой аппроксиматор | 1981 |

|

SU1010619A1 |

| Устройство для вычисления логарифмических функций | 1978 |

|

SU771672A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU928347A1 |

| Цифровой преобразователь координат | 1980 |

|

SU942004A1 |

| Устройство для воспроизведения кардиоиды | 1981 |

|

SU1007102A1 |

ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий первый, второй и третий двоичные умножители, отличающийся тем, что, с целью увеличения быстродействия и расширения класса решаемых задач путем обеспечения возможности вычисления разности между линейной и кусочно-логарифмической дробно-рациональной либо кусочно-арктангенской дробно-рациональной, либо кусочно-арктангенсной и кусочно-линейной функциями, в него введены импульсные вычитатёль и сумматор-вычитатель, счетчик аргумента, дешифратор участка аппроксимации, коммутатор, счетчик участков и блок памяти, причем тактовый вход преобразователя соединен с первыми информационными входами импульсных сумматора-вычитателя и вычитателя, выход которого соединен с импульсным входом первого двоичного умножителя, вЫход которого подключен к импульсному входу второго двоичного умножителя и первому информационному входу коммутатора, второй информационный вход которого соединен с выходом второго двоичного умножителя и вторым информационным входом импульсного. г вычитателя, выход которого соединен с третьим информационным входом комхл мутатора, управляющий вход и выход которого соединены сс ответственно с входом задания режима преобразовате

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Гильман Г.Г., Иохельсон Е.Д., Лихтциндер Б.Я., Широков С.М, Цифровой функциональный преобразователь для многоканальных измерительных систем | |||

| - Приборы и системы управления, 1978, № 10 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Смолов В.Б | |||

| Функциональные преобразователи информации | |||

| Л., Энергоиздат, 1981, с | |||

| Переносный кухонный очаг | 1919 |

|

SU180A1 |

Авторы

Даты

1984-08-07—Публикация

1983-04-18—Подача