Изобретение относится к вычислительной технике и предназначено для формирования (2+п)-разрядного кода нормирующей функции по коду адреса, (1+п)-разрядного прямого кода синуса или косинуса по (2+п)- разрядному коду угла, изменяющегося от О до 2 п () радиан, и n-разрядного кода арктангенса по n-разрядному коду аргумента 6 0, (), где п - разрядность приведенного кода угла или аргумента арктангенса, и может быть использовано при построении специализированного микропроцессорного вычислителя (СМВ), например, для устройства отображения информации метеорадиолокатора.

Цель изобретения - повышение быстро- действия и сокращение аппаратурных затрат цифрового генератора фукнций.

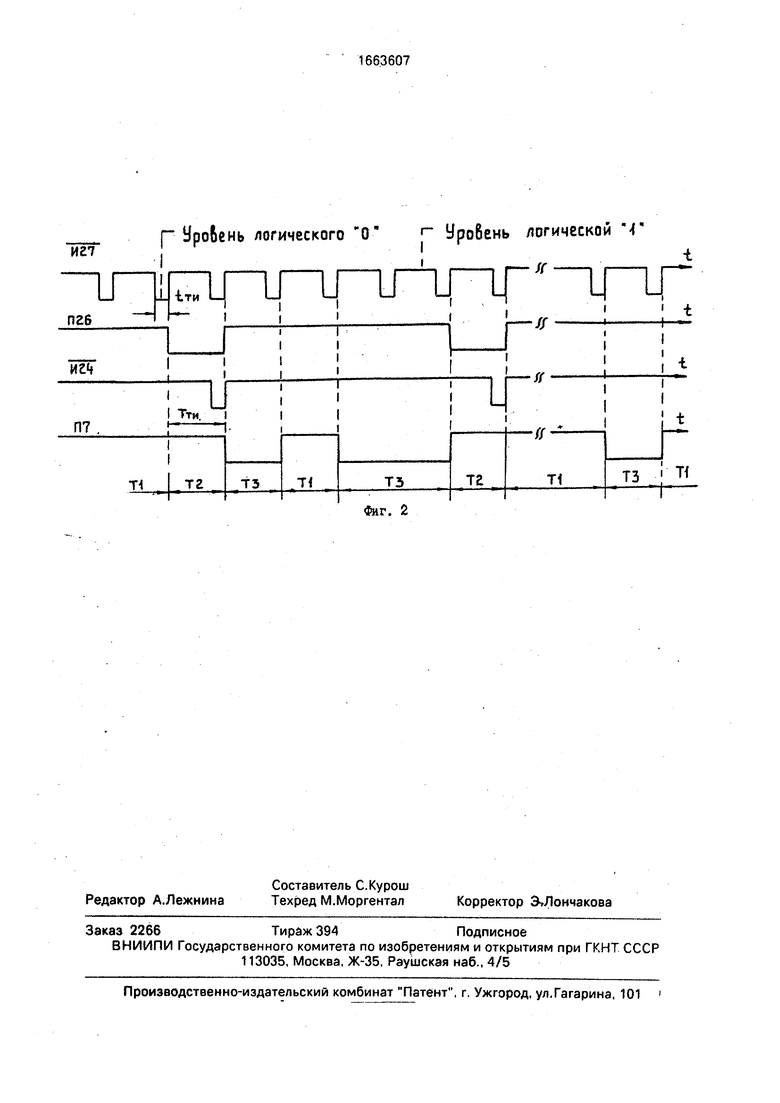

На фиг. 1 приведена структурная схема цифрового генератора функций; на фиг.2 - временные диаграммы сигналов на тактовом входе, на втором управляющем входе, на первом управляющем входе генератора и на выходе элемента ИЛИ.

Генерато (фиг, 1) содержит первый 1 и второй 2 сумматоры, умножитель 3, первый блок 4 памяти, блок5 элементов ИСКЛ ЮЧА- ЮЩЕЕ ИЛИ, элемент НЕ 6, первый управляющий вход 7, адресный кодовый вход 8 задания константы, первый коммутатор 9, кодовый вход-выход 10, первый 11, второй 12, третий 13, четвертый 14 и пятый 15 элементы И, второй блок 16 памяти, второй 17 и третий 18 коммутаторы, вход 19 первого и вход 20 второго разрядов кода операции, первый 21 и второй 22 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, регистр 23, элемент ИЛИ 24, блок 25 элементов ИЛИ, второй управляющий вход 26, тактовый вход 27, кодовые выходы 28 и 29, образованные разрядными выходами старших и младших разрядов сумматора 2 соответственно, и кодовый выход 30, первый 31, второй 32 и третий 33 выходы регистра 23.

Обозначим на входах и выходах генератора и его узлов через П, Ф и И соответственно потенциальные сигналы, коды и ин- верснче импульсы так, что после каждой из этих букв стоят номер входа генератора, например П7, Ф8 и И27 означают сигнал О

или 1 на входе 7, код на входе 8 и инверсные импульсы на входе 27 соответственно или номер узла генератора, например Ш, Ф9 и И24 означают потенциальные сигналы нз выходе переполнения сумматора 1, код

из кодовом выходе коммутатора 9 и инверсный импульс на выходе элемента 24 соответственно.

Кроме того, обозначим через Ф28 П19Ф28 код на втором кодовом входе коммутатора 9 и первом кодовом входе коммутатора 17, Ф17 П13Ф17-код на адресном кодовом входе блока 16 памяти, Ф30 П13ФЗО - код на адресном кодовом входе блока 4 памяти, ФНф Ф4Ф16 - код нормирующей функции на первом кодовом входе коммутатора 18 (где Ф1б означает код, образованный соответствующими двумя разрядами кода Ф16), ФТф П322П32Ф1 - код, тригонометрической функции на втором кодовом входе коммутатора 18, (Р1) и (Р2) - содержимое (код) первого и второго регистров Р1 и Р2 сомножителей ИС 1802ВРЗ умножителя 3, а инверсный код произведения на выходе умножителя 3 обозначим через

(Р1)(р2) 0)

где Фокр - оператор операции усечения с округлением до восьми разрядов 16-разрядногокода(Р1)(Р2).

Загрузка регистра 23 и регистров Р1 и Р2 умножителя 3 осуществляется по положительному фронту каждого И24, а временные программы поступления на генератор

управляющих сигналов П7, П19, П20 (Ф0п П19П20 - код операции), П26 и И27 определяют функционирование генератора во времени так, что в его работе можно выделить следующие три режима (фиг. 2):

1. Режим хранения при П7 П26 1 длительностью Т1 КМ™, где К1 0, 1, 2,

3, ...; Тти - длительность периода частоты следования тактовых импульсов И27;

2.Режим загрузки при П7 1, П26 0 длительностью Т2 Т™;

3.Режим выдачи результата при П7 О, П26 1 длительностью ТЗ КЗ Т™, где КЗ 1,2,3

Чередование режимов работы генера- тора (т.е. взаимосинхронизация его входных сигналов и кодов и выдача результата на вход-выход 10) обеспечивается микропроцессором и схемой синхронизации и начальной установки СМВ, в котором данный генератор используется.

Принципы чередования режимов работы генератора заключаются в том, что после режима загрузки может следовать режим выдачи результата или режим хранения, по- еле режима хранения может следовать режим загрузки или режим выдачи результата, а после режима выдачи результата может следовать любой из режимов (фиг. 2).

Генератор работает следующим обра- зом.

В течение Т1 П7 П26 1 в памяти генератора (т.е. в регистре 23 и регистрах Р1 и Р2 ИС 1802ВРЗ умножителя 3)содержится информация, обусловленная предысторией его работы, кодовый выход коммутатора 18 находится в третьем состоянии при П701, коммутатор 17 вырабатывает код Ф17 ФЗО при П26 1, а на адресном кодовом входе 8 (шине адреса) и кодовом входе-выходе 10 (шине данных) формируются коды в соответствии с программами функционирования СМВ.

В течение Т2 П7 1, П2б 0 кодовый выход коммутатора 18 находится в третьем состоянии, по отрицательному фронту сигнала П26 0 на входах 19 и 20 устанавливаются сигналы кода Фоп П19П20, элемент 11 вырабатывает сигнал П11 П19 П20, при П11 1 на входе 8 устанавливается код Ф8 адреса задания константы, а при П11 0 на входе-выходе 10 устанавливается код Ф10 аргумента тригонометрической функции (синуса при П19 О, П20 0, косинуса при П19 О, П20 0, арктангенса при П19 1, П20 0) в соответствии с выражением

л

а (я/2)-Ј (я/2)-У о|2

i -i

л п

Опр 2) 0| 2 ; i 1

Л Л Л

Одоп I Олр

где разрядная цифра (0 или 1) 1-го разряда кода а при i -1,0,1,2,п;

сспр- код, образованный п младшими разрядами кода а и определяющий прямой приведенный угол «Пр ( л/2 ) ЙПР ;

йдоп- код, определяющий дополнительной до я/2 приведенный угол адоп , т.е. Олр л/2 ;

I -(2+п)-разрядный код единицы в модифицированном дополнительном коде.

В такте Т2 по окончании переходных процессов элемент 13 вырабатывает сигнал П13 П26-П31 0, элементы 14 и 15 - сигналы:

П 14

Оопри П 19 0 , П20 0; йоприп 19 0,П20 1 ; (4) О при П 19 1 ;

П 15

S0 «-1 приП 19 0, С0 Ј2-1 + Ob при П 19 0,П20 1 О при П 19 1 .

а сумматор 2, блок 5 и коммутаторы 9 и 17 вырабатывают коды:

Ф2 Ф5 + О...ОП14 П2Ф28Ф29; Ф5 ГМ4 Ф 14 Ф 9 П 11 Ф 28 V П 11 Ф 8 ; Ф 17 Ф28

(6)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1990 |

|

SU1728860A1 |

| Цифровой преобразователь тригонометрических функций | 1986 |

|

SU1327094A1 |

| Цифровой преобразователь координат | 1983 |

|

SU1163322A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1257638A1 |

| Цифровой вычислитель функций | 1986 |

|

SU1354187A1 |

| Устройство для деления | 1990 |

|

SU1746378A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Синусно-косинусный преобразователь | 1986 |

|

SU1327095A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1290307A1 |

| Цифровой преобразователь координат | 1983 |

|

SU1141404A1 |

Изобретение относится к вычислительной технике и предназначено для формирования кода нормирующей функции и кодов синуса, косинуса и арктангенса. Цель изобретения - повышение быстродействия цифрового генератора функций. Цифровой генератор функций содержит первый 1 и второй 2 сумматоры, умножитель 3, первый блок 4 памяти, блок 5 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент НЕ 6, первый управляющий вход 7, кодовый вход 8 адреса задания константы, первый коммутатор 9, первый элемент И 11 и входы первого 19 и второго 20 разрядов кода операций, вход - выход 10 данных, элементы И 12 - 15, второй блок 16 памяти, второй 17 и третий 18 коммутаторы, первый 21 и второй 22 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, регистр 23, элемент ИЛИ 24, блок 25 элементов ИЛИ, второй управляющий вход 26 и тактовый вход 27. Цель достигается за счет введения элементов И 12 - 15, блока 16 памяти, коммутаторов 17 и 18, элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 21 и 22, регистра 23, элемента ИЛИ 24, блока 25 элементов ИЛИ. 2 ил.

Ф 10

-14

(4-2 приП19 0;

где So и Со - разрядные цифры знаковых разрядов прямых кодов синуса и косинуса 4Q угла а соответственно;

Ф10 - код, образованный п младшими разрядами кода Ф10.

При П11 0 код Ф2 является кодом аргумента арктангенса так что связь между кодом # и углом а 45 . Ф 2 tgp (tgp)yn +

+ ({д/3)ап Ф28+Ф29.

(l-2 |4)приП19 1, Л .

(2)

характеризуется выражениями:

а при П19 0 - кодом приведенного угла Ф 2 П 14 «пр v П 14 Одоп У

Ууп + Уап , (8)

при переполнении которого вырабатывается сигнал П2 1, а при П2 0 ууп Ф28, Ф29 (индексы уп и ап указывают на управляющую и аппроксимирующую части кодов аргументов tg/J и у соответственно).

В течение Т2 генератор активизируется при П11 1 на воспроизведение кода ФНф нормирующей функции, а при П11 0 - на воспроизведение тригонометрической функции

Фгф П 19 (П20 sin a v vn 20 cosa)vn 19 arctg/3..

Вычисление кода (9)осуществляется методом, кусочно-линейной аппроксимации так, что при П19 0 аппроксимация производится по синусной функции в угле от О доя/2 радиан, а при П19 1 - по функции арктангенса в области изменения аргумента от 0 до 1, причем в каждом случае число -участников аппроксимации равно 2 , величина каждого участка равна

Л (П 19 19) 2

-7

(Ю)

а угловая точка выбрана в начале каждого участка аппроксимации. Поэтому по окончании переходного процесса на входах умножителя 3 вырабатываются (при П11 0) код аппроксимирующей части аргумента

(11)

Ф29 П 19 19 (tgjS)an

и код приращения функции на участке аппроксимации

Ф 16 П 19 sin ууп + А) - sin ууп

-л

vni9-()yn-(tg/3)yn,

(12)

П

где (tg ft ) Уп ф 28 + 2 - значение аргумента в конце участка аппроксимации арктангенса.

По окончании переходных процессов на генератор приходит И27 и формируется И24 П26 vi/127 0, по положительному фронту которого в регистры Р1 и Р2 умножителя 3 заносятся коды Ф1би Ф29, а в регистр 23 - код Ф9 и сигналы П11, П15иП2(при П2 1

отмечается вычисление кода синуса для у я/2 ). На этом режим загрузки заканчивается и начинается режим выдачи.

В течение ТЗ через время задержки Таз 30 не регистра 23 на выходах регистра 23 формируется код ФЗО и сигналы в соответствии с выражениями:

ГфЗОтз Ф9т2; 1п31тз П11т2; )П32тз П15т2; (ПЗЗтз П2-Г2,

(13)

20

где в правых частях стоят код Ф9 и сигналы 15 П11, П15 и П2 с индексом Т2. т.е, сформированные в режиме загрузки.

С помощью сигналов и кода элемент 13 вырабатывает сигнал П13 П31, блок 25 - код

Ф25 ПЗЗ ФЗ ПЗЗ (1...1), (14)

5

0

0

5

0

блок 4 при П13 0 - код значения тригонометрической функции в узле аппроксимации, сумматор 1 при П13 0 - код модуля тригонометрической функции (знак этой функции определен сигналом П32, выработанным вТЗ по сигналу (5) периода Т2), а при П13 1 блоки 4 и 16 вырабатывают код ФНф нормирующей функции,

При П13 0 и ПЗЗ 1 сумматор 1 вырабатывает код Ф1 , соответствующий синусу угла я/2

В ТЗ по окончании переходных процес-. 5 сов на генератор поступает очередной И 27. по которому {т.е. по П27 v П7 0) результат функционирования генераторэ

Ф10 Ф18 П13- ФтфИПЗ- Фнф,(15) выдаваемый (при П7 0) коммутатором 18 на вход-выход 10, может быть загружен в память любого устройства СМВ. В дальнейшем работа генератора во времени определяетсятакжепрограммойфункционирования СМВ.

Формула изобретения

Цифровой генератор функций, содержащий два сумматора, умножитель,- блок памяти, блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент НЕ, первый коммутатор, элемент И, причем вход переноса первого сумматора и вход первого слагаемого второго сумматора подключены к входу логического нуля генератора, вход второго слагаемого которого подключен к выходу блока элементов ЙСК- 5 ЛЮЧАЮЩЕЕ ИЛИ, первый информационный вход первого коммутатора подключен к входу адреса задания константы генератора, отличающийся тем, что, с целью повышения быстродействия, в него введены

четыре элемента И, блок памяти, два коммутатора, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. регистр, элемент ИЛИ, причем тактовых вход генератора подключен к первому входу элемента ИЛИ, выход которого подключен к входам синхронизации регистра и умножителя, вход перового разряда кода операции генератора подключен к входу элемента НЕ, первому входу первого элемента И и к старшим разрядам второго входа первого и первого входа второго коммутаторов, вход второго разряда кода операции генератора подключен к первым входам второго элемента И, первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и второму входу первого элемента И, выходы старших разрядов второго сумматора подключены к младшим разрядам второго входа первого и младшим разрядам первого входа второго коммутаторов, первый управляющий вход генератора подключен к входу выбора третьего коммутатора, выход которого подключен к информационному входу-выходу генератора, первый и второй старшие разряды которого подключены к первому входу второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и к вторым входам второго элемента И и первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соответственно, младшие разряды информационного входа-выхода генератора подключены к разрядному входу блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, второй управляющий вход генератора подключен к управляющему входу,второго коммутатора, второму входу элемента ИЛИ и первому входу третьего элемента И, выход которого подключен к старшим разрядам входов адреса первого и второго блоков памяти, выходы первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к первым входам четвертого и

пятого элементов И соответственно, вторые входы которых подключены к выходу элемента НЕ, выход четвертого элемента И подключен к входу переноса второго сумматора и управляющим входам блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выход первого коммутатора подключен к информвцинному входу регистра, выход которого подключен к второму входу второго регистра и к младшим разрядам входа адреса первого блока памяти, выход первого элемента И подключен к управляющему входу первого коммутатора и через регистр к второму входу третьего элемента И и управляющему входу

третьего коммутатора, выход второго коммутатора подключен к младшим разрядам входа адреса второго блока памяти, выход первого блока памяти подключен к первому входу третьего коммутатора и входу первого

слагаемого первого сумматора, выход второго блока памяти подключен к входу первого сомножителя умножителя и к соответствующим разрядам первого входа третьего коммутатора, выход пятого элемента И через регистр подключен к двум старшим разрядам второго входа третьего коммутатора, младшие разряды которого подключены к выходу первого сумматора, выход переполнения второго сумматора через регистр подключен к старшим разрядам входа второго слагаемого первого сумматора и управляющему входу блока элементов ИЛИ, выход которого подключен к младшим разрядам второго слагаемого первого сумматора, вход блока элементов ИЛИ подключен к выходу умножителя, вход второго сомножителя - к выходу младших разрядов второго сумматора, выход второго элемента И - к второму входу второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ.

Фиг. 2

| Генератор функций | 1986 |

|

SU1337895A1 |

| Авторское свидетельство СССР № 1374964, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-07-15—Публикация

1989-03-21—Подача