Изобретение относится к автоматике и вычислительной технике и может найти применение в управляющих системах и гибридных вычислительных устройствах, для вычисления в следящем 5 режиме полиномиальной функции вида у(х)..ао от аналогового сигнала X с представлением результата в цифровой форме.

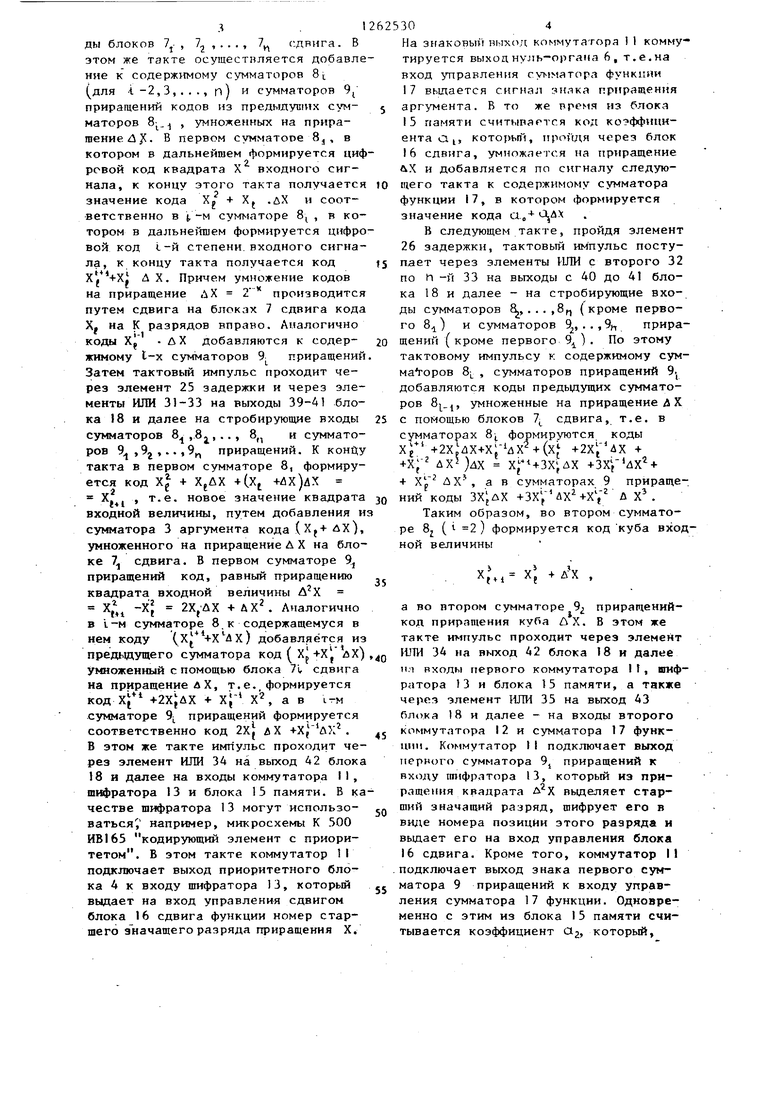

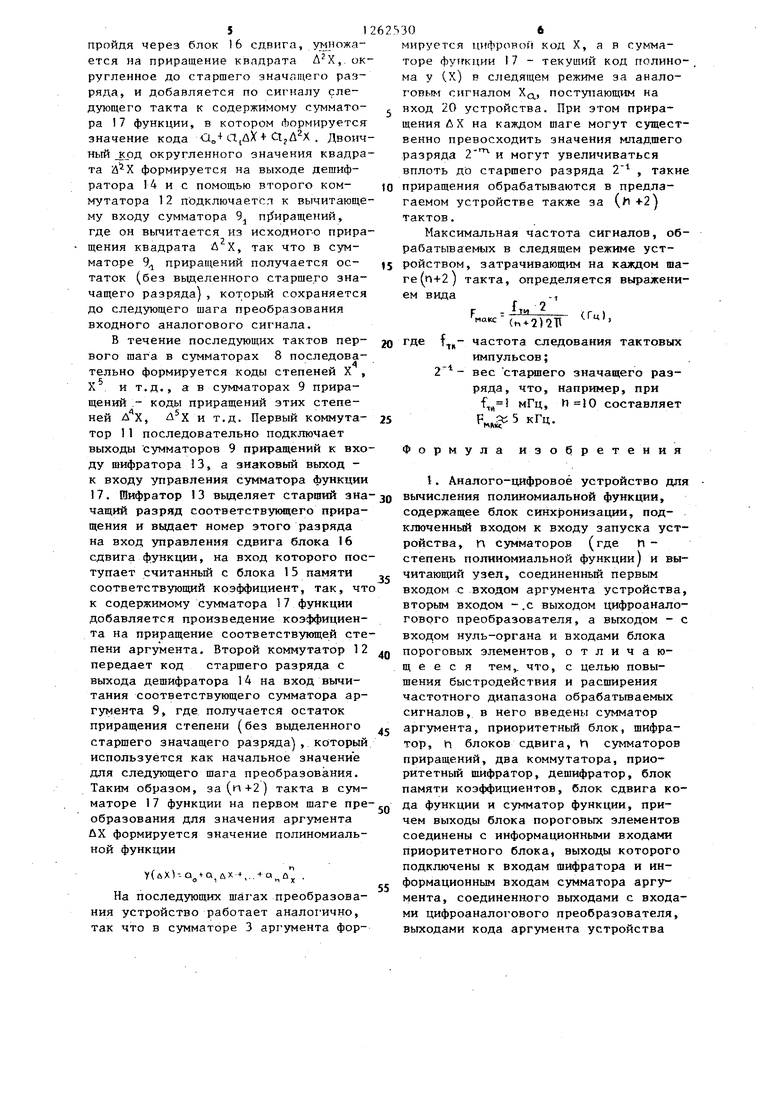

Цель изобретения - повышение бы- ю стродействия и расширение частотного диапазона обрабатываемых сигналов. На фиг, I изображена блок-схема аналого-цифрового устройства для вычисления полиноминальной функции; на 15 фиг. 2 - схема блока синхронизации. Устройство (фиг.1) содержит вычитающий узел 1, цифроаналоговый преобразователь 2, сумматор 3 аргумента, риоритетный блок 4, блок 5 порого- 20 вых элементов нуль-орган 6, п блоков 7j , Tj , ..., 7 сдвига, h сумматоров 8 , 8 ,.. . , .8, , п сумматоров 9 , 92 , . .., 9„ , приращений, шифратор 10, первый 11 и второй 12 коммутаторы, приоритетный шифратор 13, дешифратор 14, блок 15 памяти коэффициентов, блок 16 сдвига кода функции, сумматор 17 функции и блок 18 синхронизации выходы 19 кода аргумента, 30 вход 20 аргумента, выход 21 кода функции и вход 22 запуска устройства. Блок 18 синхронизации содержит (фиг.2) генератор 23 импульсов,первый 24, второй 25, третий 26, четвер- 35 тый 27,.,., (h +1)-й 28, ( п +2)-и 29,(+3)-й 30 элементы задержки, первый 31, второй 32,,,,, П -и 33, р+1)-й 34; (п +2)-и 35 элементы ИЛИ.

Устройство работает следующим об- 40 разом.

Для вычисления искомой полиномиа1|ьной функции у(х) ao-i-Cl,x +СЦх + + .. .+ о„х от входного аналогового с 11гнала X, который подается на вход 45 20 устройства, перед началом работы устройство устанавливается в исходное состояние, для которого обнуляются сумматор .3 аргумента, сумматоры 8 , 8j ,.. ., Bf, и сумматоры 9, 9 , 50 9 приращений, а в сумматор 17 функции заносится код коэффициента О-о , остальные коэффициенты Qj, са., ..., О. записьшаются в блок 15 памяти.

Вычитающий узел 1 определяет раз- 55 ность дЦ. между входным сигналом XQ на входе 20 и напряжением обратной связи с выхода цифроаналогового преобразователя 2, в которое преобразуется код сумматора 3 аргумента. Напряжение рассогласования прикладывается к входу нуль-органа 6, который определяет его знак, и входам блока 5 пороговых элементов, которые срабатывают при достижен 1и напряжением разности. I порогов, на которые настроены пороговые элементы по двоичному закону: 1,2,4,,.., ,..., условных единиц равных весу младшего разряда 2

где tTi - количество

элементов в блоке 5, П - количество ра:зрядов в сумматоре аргумента.

При подаче сихнала на вход 22 устройства в блоке 18 синхронизации по входу 36 запускается генератор 23 импульсов, который выдает импульсы на выходы блока 18 с соответствующей задержкой при прохождении через цепочку элементов 24,25,,.,, 30 задержки. По первому импульсу на тактирующем выходе 37 блока 18 нуль-орган 6 фиксирует знак напряжения рассогласования dU , а приоритетный блок 4 выделяет старший из сработавших пороговых элементов блока 5. В следующий момент времени тактовый импульс проходит через элемент 24 задержки на первый выход 38 блока 18 и далее на стробирующий вход сумматора 3 аргумента, зтот же тактовый импульс проходит через элементы ИЛИ 31, 32,..., 33 блока 18 на стробирующие входы сумматоров 8, 82,..., 8г и сумматоров 9,,, 92,,.,, 9 приращений, на входы управления которых поступает сигнал.с выхода нуль-органа 6, настраивая зти сумматоры на вьтолнение операций сложения или вычитания в зависимости от знака напряжения рассогласования д , Коды с выхода приоритетного блока 4 представляют собой приращения входного сигнала Ах округленные до значения кратного степени двойки, эти коды добавляются (в соответствии со знаком на выходе нуль-органа 6 с мматор аргумента 3 настраивается на сложение или вычитание по ВХОДУ управления) к содеряа; мому сумматора 3, в котором и формируется цифровой код X. Х +4Х входного сигнала Хд в режиме слежения за этим сигналом. Шифратор 10 осуществляет шифрацию позиционного двоичного кода приращения в код номера разряда (к), в котором находится единица. Этот код поступает на входы блоков 7j- , 7,, , . . . , 7 сдвига. В этом же такте осуществляется добавление к содержимому сумматоров 8 (для i-2,3,...,n) и сумматоров 9 приращений кодов из предндуп нх CN-Mматоров 8;, , умноженных на прирашение4(. В первом сумматоое 8., , в котором в дальнейшем формируется циф2

ревой код квадрата X входного си1- нала, к концу этого такта получается значение кода Х + Xj .дХ и соответственно в 1. -м сумматоре 8 , в котором в дальнейшем формируется цифровой код 1-й степени, входного сигнала, к концу такта получается код ДХ. Причем умножение кодов на приращение ДХ 2 производится путем сдвига на блоках 7 сдвига кода Х| иа К разрядов вправо. Аналогично коды Xj . дХ добавляются к содержимому 1-х сумматоров Э приращений Затем тактовый импульс проходит через элемент 25 задержки и через элементы ИЛИ 31-33 на выходы 39-41 блока 18 и далее на стробирующие входы сумматоров 8,8j,.., 8, и сумматоров 9,92,..,9 приращений. К конДу такта в первом сумматоре 8, формируется код Xg + XjAX +(Xj +ДХ)ЛХ Х,. , т.е. новое значение квадрата входной величины, путем добавления и сумматора 3 аргумента кода(), умноженного на приращение Л X на блоке 7j сдвига. В первом сумматоре 9j приращений код, равный приращению квадрата входной величины Лх ХД -Xj 2Х,ЛХ +АХ. Аналогично в 1-м сумматоре 8 к содержащемуся в нем коду () добавляется иэ предыдущего сумматора код(Хр+Х йХ) умноженный с помощью блока 71, сдвига на приращение дX, т.е., формируется код Xj +2Х|ДХ -ь Х{ X, а в L-M сумматоре 9 приращений формируется соответственно код 2х| лХ +Х, . В этом же такте импульс проходит через элемент ИЛИ 34 на выход 42 блока J8 и далее на входы коммутатора I1, шифратора 13 и блока 15 памяти. В качестве шифратора 13 могут использоваться например, микросхемы К 500 ИВ163 кодирующий элемент с приоритетом. В этом такте коммутатор II подключает выход приоритетного блока 4 к входу шифратора 13, который выдает на вход управления сдвигом блока 16 сдвига функции номер старшего значащего разряда приращения X.

На знаковьпг выход коммутатора I 1 коммутируется выход нуль-органа 6, т.е.на вход управления сумматора функции 17 выдается сигнал знака приращения аргумента. В то же время из блока

15памяти считывается код коэффициента о i, которьп, пройдя через блок

16сдвига, умножается на приращение йХ и добавляется по сигналу следующего такта к содержимому сумматора функции 17, в котором формируется значение кода а.„

В следующем такте, пройдя элемент 26 задержки, тактовый импульс поступает через элементы ИЛИ с второго 32 по h -и 33 на выходы с 40 до 41 блока 1 В и далее - на стробирующие входы сумматоров ,...,8 (кроме первого 8 ) и сумматоров 9, . . , 9 приращений ( кроме первого 9) . По этому тактовому импульсу к содержимому суммагоров 8 , сумматоров приращений 9j добавляются коды предыдущих сумматоров 8j, умноженные на приращение Д X с помощью блоков 7j сдвига, т.е. в сумматорах 8 формируются коды + (x + +Х; ДХ)дх Хр+ЗХЛХ +ЗХ{ ДХ + + Хр ДХ, а в сумматорах 9 приращений коды 3XjAX +зхрлх +х7 Д х

Таким образом, во втором сумматоре 8j ( i 2 ) формируется код куба входной величины

Х,, Xj + Д-Х

а во втором сумматоре 9 приращеннйкод приращения куба ДХ. В этом же такте кмпульс проходит через элемент ИЛИ 34 на выход 42 блока 18 н далее чл входы первого коммутатора I1, шифратора 13 и блока 15 памяти, а также через элемент ИЛИ 35 на выход 43 бЛ4гка 18 и далее - на входы второго коммутатора I2 и сумматора 17 функции. Коммутатор II подключает выход перного сумматора 9 приращений к входу пшфратора 13, который нэ приращения квадрата выделяет старший значащий разряд, шифрует его в внде номера позиции этого разряда и выдает его на вход управления блока 16 сдвига. Кроме того, коммутатор И подключает выход знака первого сумматора 9 приращений к входу управления сумматора 17 функции. Одновременно с этим из блока 15 памяти считывается коэффициент Qj, который. пройдя через блок 16 сдвига, умножается на приращение квадрата , округленное до старшего значащего разряда, и добавляется по сигналу следующего такта к содержимому сумматора 17 функции, в котором Формируется значение кода 0 +ajAX . Двоичный округленного значения квадрата ЙХ формируется на выходе дешифратора 14 и с помощью второго коммутатора 12 подключается к вычитаюп1ему входу сумматора 9 П15иращений, где он вычитается из исходного приращения квадрата Д X, так что в сумматоре 9 приращений получается остаток (без выделенного старшего значащего разряда), который сохраняется до следующего шага преобразования входного аналогового сигнала. В течение последующих тактов первого шага в сумматорах 8 последовательно формируется коды степеней X , и т.д., а в сумматорах 9 приращений коды приращений этих степеней АХ, и т.д. Первый коммутатор 11 последовательно подключает выходы сумматоров 9 приращений к входу шифратора 3, а знаковый вьпсод к входу управления сумматора функции 17. Шифратор 13 выделяет старший зна чащнй разряд соответствующего приращения и выдает номер этого разряда на вход управления сдвига блока 16 сдвига функции, на вход которого пос тупает считанный с блока 15 памяти соответствующий коэффициент, так, чт к содержимому сумматора 17 функции добавляется произведение коэффициента на приращение соответствующей сте пени аргумента. Второй коммутатор 12 передает код старшего разряда с выхода дешифратора 14 на вход вычитания соответствующего сумматора аргумента 9, где получается остаток приращения степени (без вьщеленного старшего значащего разряда), который используется как начальное значение для следующего шага преобразования. Таким образом, за (п+2) такта в сумматоре 17 функции на первом шаге пре образования для значения аргумента АХ формируется значение полиномиальной функции Y(uXl-Q +Q uX +,..-( . На последующих шагах преобразования устройство работает аналогично, так что в сумматоре 3 аргумента формируется цифровой код X, а в сумматоре фу гкции 17 - текущий код полино- , ма у (Х) в следящем режиме за аналоговым сигналом XQ., поступающим на вход 20 устройства. При этом приращения ДX на каждом шаге могут существенно превосходить значения младшего разряда 2 и могут увеличиваться вплоть до старшего разряда 2 , такие приращения обрабатываются в предлагаемом устройстве также за (1+2) тактов. Максимальная частота сигналов, обрабатываемых в следящем режиме устройством, затрачивающим на каждом шаге (п+2) такта, определяется выражением вида ( + 2)211 f,,- частота следования тактовых где импульсов; 2 - вес старшего значащего разряда, что, например, при f,j,} мГц, И 10 составляет кГц. Формула изобретения , Аналого-цифровое устройство для вычисления полиномиальной функции, содержащее блок синхронизации, подключенный входом к входу запуска устройства, п сумматоров (где П степень полиномиальной функции) и вычитающий узел, соединенный первым входом с входом аргумента устройства, вторым входом -.с выходом цифроаналогового преобразователя, а выходом - с входом нуль-органа и входами блока пороговых элементов, отличающееся тем,, что, с целью повышения быстродействия и расширения частотного диапазона обрабатьшаемых сигналов, в него введены сумматор аргумента, приоритетный блок, шифратор, h блоков сдвига, h сумматоров приращений, два коммутатора, приоритетный шифратор, дешифратор, блок памяти коэффициентов, блок сдвига кода функции и сумматор функции, причем выходы блока пороговых элементов соединены с информационными входами приоритетного блока, выходы которого подключены к входам шифратора и информационным входам сумматора аргумента, соединенного выходами с входами цифроаналогового преобразователя, выходами кода аргумента устройства и информационнь -ж входами первого блока сдвига, выходы каждого I -го (1 I h) блока сдвига подключены к суммирующим входам i-го сумматора приращений и к информационным входам i-ro сумматора, соединенного выходам с информационными входами ( блока сдвига, выход шифратора подклю чен к входам управления сдвигом блоков сдвига, выходы приоритетного бло ка и сумматоров приращений соединены с соответствующими информационными входами первого коммутатора, кодо вый выход которого подключен к информационному входу приоритетного шифратора, соединенного выходом с входом управления сдвигом блока сдви га кода функции и входом дешифратора подключенного выходом к информационному входу второго коммутатора, выходы которого соединены с вычитающими входами сумматоров приращений, выход нуль-органа подключен к знаковому разряду первого информационного входа первого коммутатора и к входам управления знаком суммирования сумматоров, сумматора аргумента и сумматоров приращений, выход блока памяти коэффициентов соединен с информационным входом блока сдвига кода функции подключенного выходом к информационному входу сумматора функции, соединенного входом управления знаком суммирования со знаковым выходом первого коммутатора, а выходом - с выходом кода функции устройства, причем блок синхронизации подключен тактирующим выходом к стробирующим входам приоритетного блока и нуль-органа, первым синхронизирующим выходом - к стробирующему входу сумматора аргу130 1-м( +1) мента, каждым синхронизирующим выходом - к стробирующим входам (i--l)-ro сумматора и (t-l)-ro сумматора приращений, (h+2)-M синхронизирующим выходом - к управляющему входу первого коммутатора, стробирующему входу приоритетного шифратора и адресному входу блока памяти коэффициентов, а(м+3)-м . синхронизирующим выходом - к управляющему входу второго коммутатора и стробирующему входу сумматора функции. 2. Устройство по п,1, о т л и ч аю щ е е с я тем, что блок синхронизации содержит (п+З) элементов задержки, (и +2) элементов ИЛИ и генератор импульсов, подключенный входом запуска к входу блока синхронизации, а выходом - к тактирующему выходу блока синхронизации и входу первого элемента задержки, выход которого соединен е первым синхронизирзтмцим выходом блока синхронизации и первыми входами первых М элементов ИЛИ, причем каждый L й (2 ) элемент задержки подключен входом к выходу (t-l)-ro элемента задержки, а выходом - к I-м входам с I -го по (и +1)-й элементов ИЛИ включительно, ( элемент задержки соединен входом с выходом h+l)-ro элемента задержки, а выходом - с первым входом (h+2)-ro элемента ИЛИ и входом (п+3)-го элемента .задержки, входы п+2-го элемен- та ИЛИ подключены к выходам с третьего по (1 +3)-и элементов задержки, выход каждого i-ro (l L$h+2) элемента ИЛИ соединен с (i +1)-м синхронизирующим выходом блока синхронизации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления полиномиальной функции от аналогового аргумента | 1990 |

|

SU1737444A1 |

| Аналого-цифровой вычислитель логарифмической функции | 1985 |

|

SU1247904A1 |

| Аналого-цифровой инкрементный вычислитель экспоненциальной функции | 1985 |

|

SU1254511A1 |

| Устройство для вычисления корней | 1990 |

|

SU1751777A1 |

| Аналого-цифровое устройство для возведения в куб | 1985 |

|

SU1251113A1 |

| Устройство для решения интегральных уравнений Фредгольма второго порядка | 1985 |

|

SU1295413A1 |

| Устройство для вычисления корней | 1987 |

|

SU1441417A1 |

| Устройство для вычисления полинома @ -й степени | 1987 |

|

SU1418708A1 |

| Устройство для вычисления тригонометрических функций | 1987 |

|

SU1427362A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

Изобретение относится к автоматике и вычислительной технике. Устройство содержит вычитающий узел, цифроаналоговый преобразователь, сумматор аргумента, приоритетный блок, блок пороговых элементов, нуль-орган, h (где И - степень полинома) бло- I ков сдвига, Л сумматоров, п сумматоров приращений, шифратор, два коммутатора, приоритетный шифратор, дешифратор, блок памяти коэффициентов, блок сдвига кода функции, сумматор функции и блок синхронизации. Повыше ние быстродействия и расширение частотного диапазона обрабатьшаемых сигналов в устройстве достигается на основе обработки на каждом шаге слежения за входным сигналом его приращений, кодированных по двоичному закоS ну, формирования кодов степеней аргу(Л мента путем сдвига на код номера старшего разряда приращения, содержащего с единицу, с одновременным формированием кодов приращений степеней аргумента. 1 з.п. ф-лы, 2 ил.

| Устройство для вычисления полиномов | 1975 |

|

SU556446A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аналого-цифровой функциональный преобразователь | 1981 |

|

SU970401A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровой функциональный преобразователь | 1976 |

|

SU744595A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-07—Публикация

1985-03-05—Подача