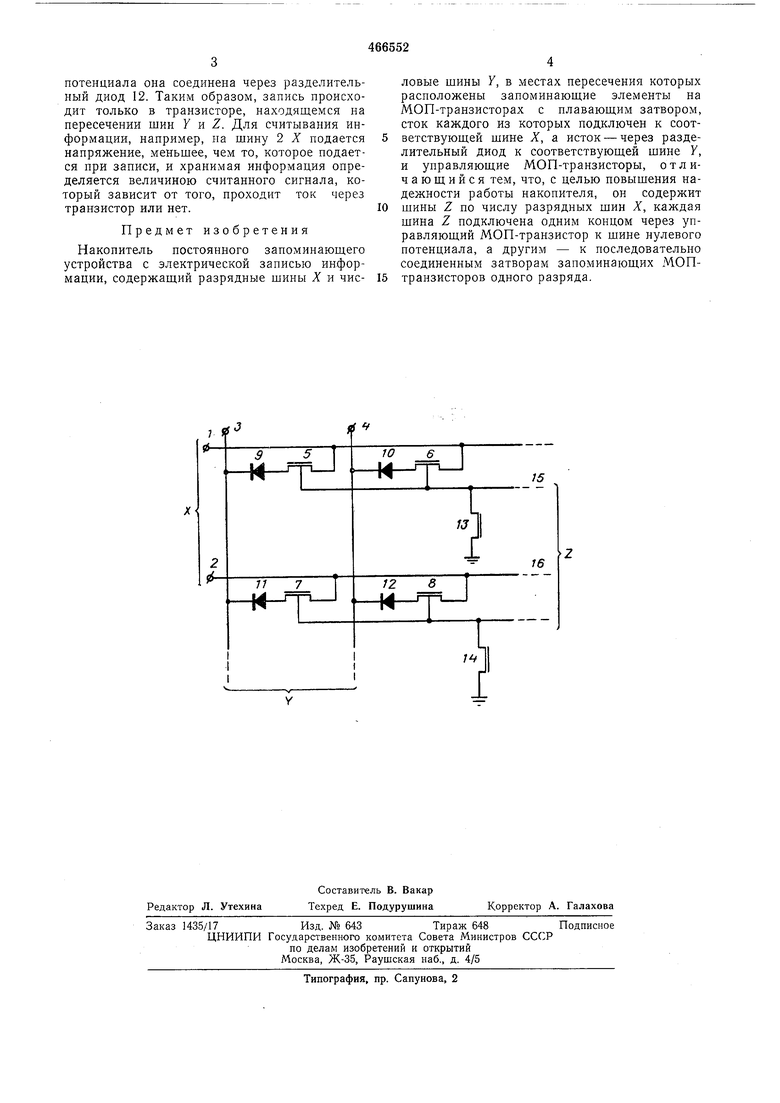

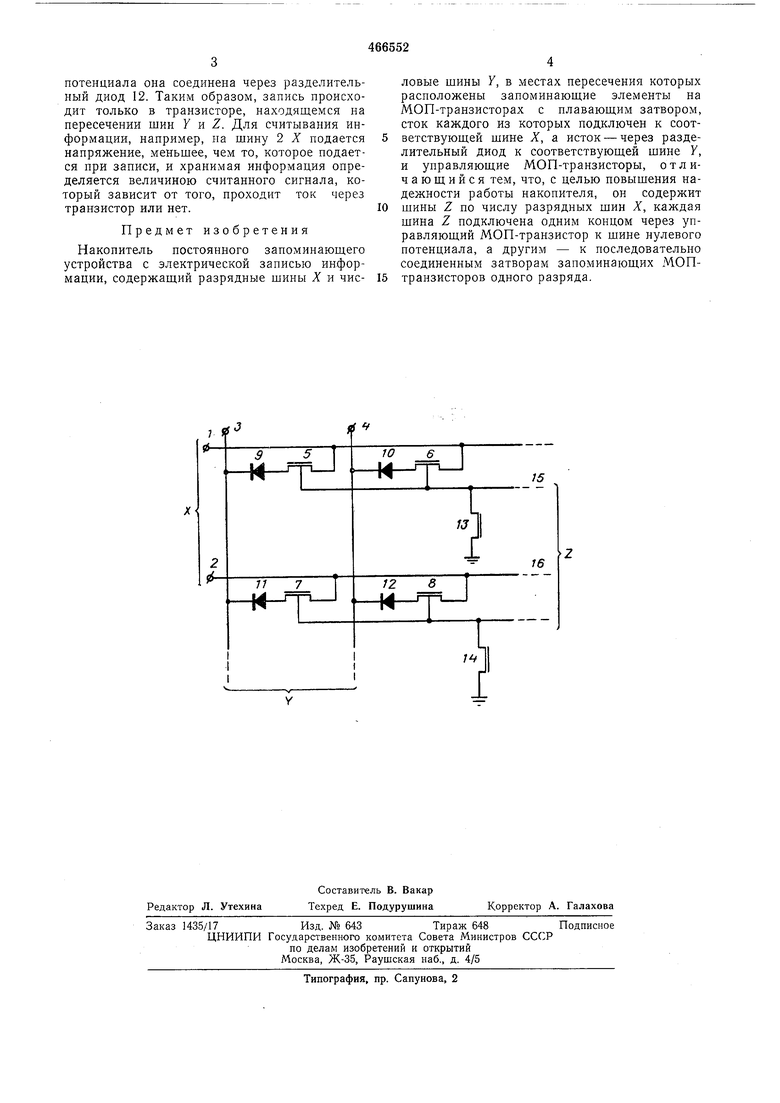

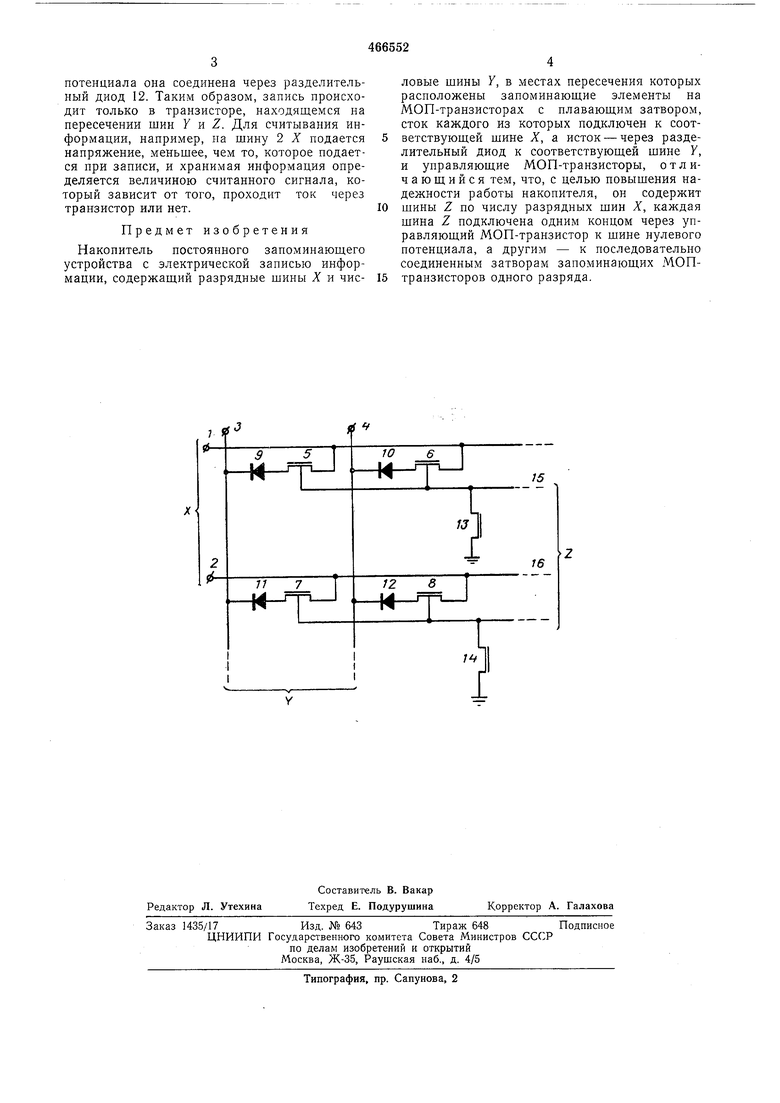

Изобретение относится к области вычислительной техники, в частности к постоянным запоминающим устройствам (ПЗУ) ЭВМ. Известны накопители ПЗУ с электрической записью информации, содержащие разрядные шины X и числовые щины У, в местах пересечения которых расположены запоминающие элементы на МОП-транзисторах с плавающим затвором, сток каждого из которых подключен к соответствующей щине X, а исток - через разделительный диод к соответствующей щине У, и управляющие МОП-транзисторы, число которых равно числу запоминающих МОПтранзисторов. Недостатком известных накопителей ПЗУ на МОП-транзисторах с плавающим затвором является наличие большого числа управляющих МОП-транзисторов (иа каждый запоминающий МОП-транзистор приходится свой управляющий МОП-транзистор), что снижает величину емкости ПЗУ, который можно достичь на одном кристалле микросхемы. Целью изобретения является повышение надежности работы накопителя, что достигается за счет введения в накопитель шии Z по числу разрядных щии X. Каждая шина Z подключена одним концом через управляющий ЛЮПтранзистор к шине нулевого потенциала, а другим - к последовательно соединенным затворам запоминающих МОП-транзисторов одного разряда. Накопитель представлен иа чертеже. Накопитель содержит разрядные 1, 2 и числовые 3, 4 шииы, в местах пересечения которых расположены МОП-транзисторы 5-8. Через разделительные диоды 9-12 исток запоминающего МОП-транзистора подключен к соответствующей числовой щине Y. Накопитель содержит управляющие МОП-транзисторы 13, 14 и координатные щины Z, каждая из которых подключена одним концом через управляющий МОП-транзистор к шине нулевого потенциала 15, 16 . В исходном состоянии затворы запоминающих транзисторов не заряжены, и во всех ячейках памяти хранится «О. Для записи «1 например, в транзистор 5 на числовую щину Y 3 подается напряжение записи, достаточное по величине для пробоя истокового диода транзистора 5. На затвор транзистора 13 подается напряжение, открывающее его. При этом на транзистор 14 подается напряжение, равное нулю. В транзисторе 5 происходит пробой истока, и записывается «1. В остальных транзисторах 6-8 накопителя запись не происходит. Хотя на исток транзистора 7 подано высокое напряжение, его пробой не возникает, поскольку цепь подложки транзистора 7 разорвана транзистором 14, а с шиной нулевого

потенциала она соединена через разделительный диод 12. Таким образом, запись происходит только в транзисторе, находящемся на пересечении шин У и Z. Для считывания информации, например, на шину 2 X подается напряжение, меньшее, чем то, которое подается при записи, и хранимая информация определяется величиною считанного сигнала, который зависит от того, проходит ток через транзистор или нет.

Предмет изобретения

Накопитель постоянного запоминающего устройства с электрической записью информации, содержащий разрядные шины X и числовые шины Y, в местах пересечения которых расположены запоминающие элементы на МОП-транзисторах с плавающим затвором, сток каждого из которых подключен к соответствующей шине X, а исток - через разделительный диод к соответствующей шине У, и управляющие МОП-транзисторы, отличающийся тем, что, с целью повышения надежности работы накопителя, он содержит

шины Z по числу разрядных шин X, каждая шина Z подключена одним концом через управляюший МОП-транзистор к шине нулевого потенциала, а другим - к последовательно соединенным затворам запоминающих МОПтранзисторов одного разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1973 |

|

SU444246A1 |

| ЯЧЕЙКА ПАМЯТИ ДЛЯ БЫСТРОДЕЙСТВУЮЩЕГО ЭСППЗУ С УПРАВЛЯЕМЫМ ПОТЕНЦИАЛОМ ПОДЗАТВОРНОЙ ОБЛАСТИ | 2011 |

|

RU2465659C1 |

| Матричный накопитель для постоянного запоминающего устройства | 1978 |

|

SU1444890A1 |

| Авторегулируемый формирователь напряжения записи для электрически программируемых постоянных запоминающих устройств на КМОП-транзисторах | 1988 |

|

SU1631606A1 |

| Усилитель считывания на моп-транзисторах /его варианты/ | 1980 |

|

SU883968A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1978 |

|

SU1444891A1 |

| ЯЧЕЙКА ПАМЯТИ ДЛЯ БЫСТРОДЕЙСТВУЮЩЕГО ЭСППЗУ И СПОСОБ ЕЕ ПРОГРАММИРОВАНИЯ | 2009 |

|

RU2481653C2 |

| Матричный накопитель для полупроводникового запоминающего устройства | 1983 |

|

SU1358001A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1977 |

|

SU734807A1 |

| ЗАПОМИНАЮЩИЙ ЭЛЕМЕНТ НА МОП-ТРАНЗИСТОРАХ | 1972 |

|

SU343308A1 |

Авторы

Даты

1975-04-05—Публикация

1973-01-02—Подача