Изобретение относится к вычислительной технике и может быть использовано для записи, хранения и считывания информации в вычислительном устройстве.

Целью изобретения является упрощение матричного накопителя.

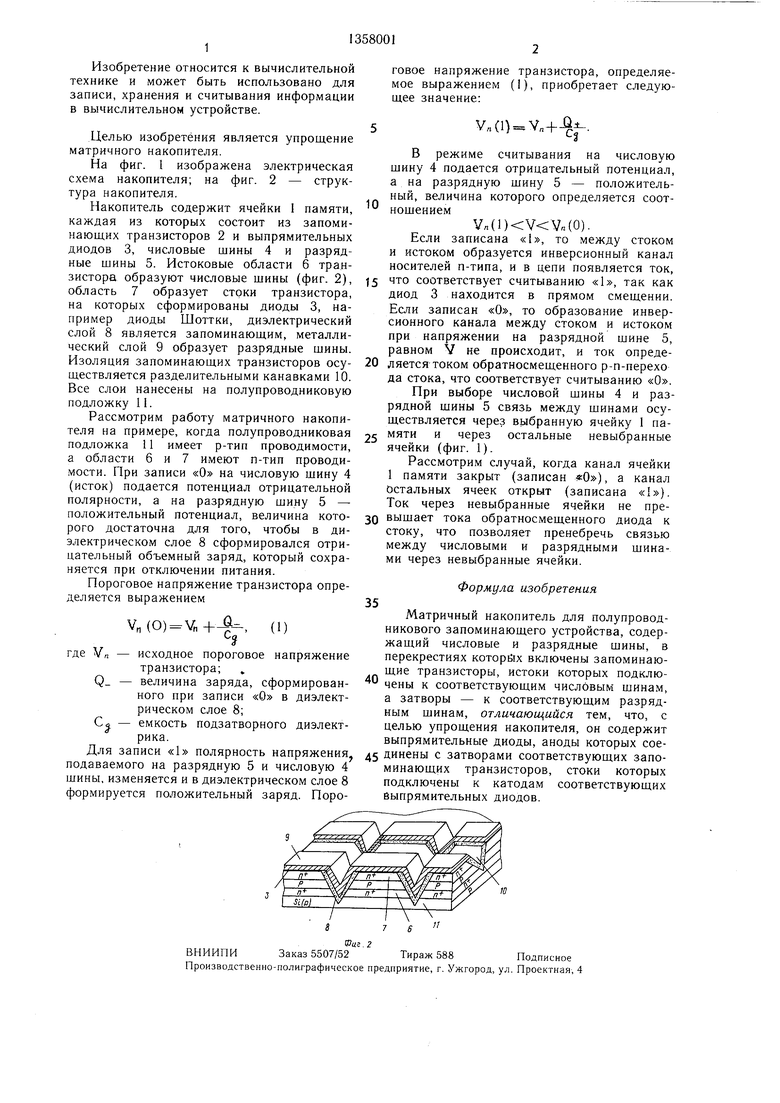

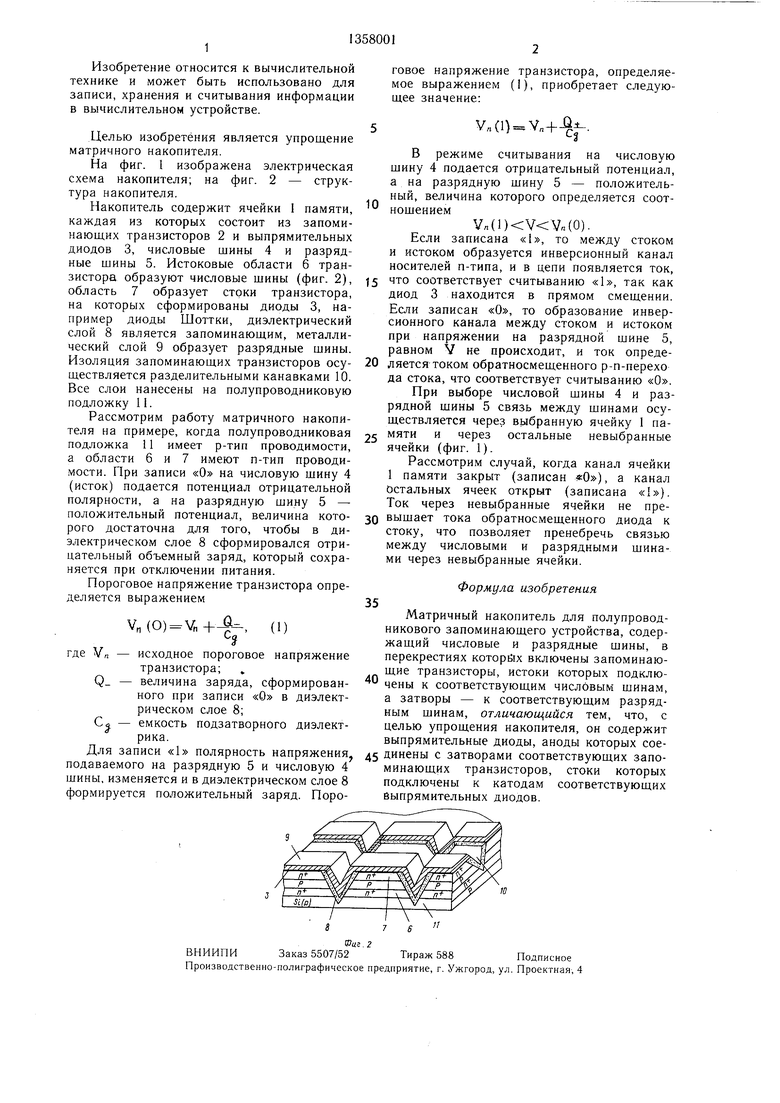

На фиг. 1 изображена электрическая схема накопителя; на фиг. 2 - структура накопителя.

Накопитель содержит ячейки 1 памяти, каждая из которых состоит из запоминающих транзисторов 2 и выпрямительных диодов 3, числовые щины 4 и разрядные щины 5. Истоковые области 6 транзистора образуют числовые щины (фиг. 2), область 7 образует стоки транзистора, на которых сформированы диоды 3, например диоды Шоттки, диэлектрический слой 8 является запоминающим, металлический слой 9 образует разрядные щины. Изоляция запоминающих транзисторов осуществляется разделительными канавками 10. Все слои нанесены на полупроводниковую подложку 11.

Рассмотрим работу матричного накопителя на примере, когда полупроводниковая подложка 11 имеет р-тип проводимости, а области 6 и 7 имеют п-тип проводимости. При записи «О на числовую щину 4 (исток) подается потенциал отрицательной полярности, а на разрядную шину 5 - положительный потенциал, величина которого достаточна для того, чтобы в диэлектрическом слое 8 сформировался отрицательный объемный заряд, который сохраняется при отключении питания.

Пороговое напряжение транзистора определяется выражением

VnO) Vn+-&- -, (1)

9

где Vn - исходное пороговое напряжение

транзистора;

Q - величина заряда, сформированного при записи «О в диэлектрическом слое 8;

Со - емкость подзатворного диэлектрика.

Для записи «1 полярность напряжения подаваемого на разрядную 5 и числовую 4 щины, изменяется и в диэлектрическом слое 8 формируется положительный заряд. Поро

говое напряжение транзистора, определяемое выражением (1), приобретает следующее значение:

У„(1).У„+-й -.

в режиме считывания на числовую щину 4 подается отрицательный потенциал, а на разрядную щину 5 - положительный, величина которого определяется соот- нощением

V«(1).(0).

Если записана «1, то между стоком и истоком образуется инверсионный канал носителей п-типа, и в цепи появляется ток,

5 что соответствует считыванию «1, так как диод 3 находится в прямом смещении. Если записан «О, то образование инверсионного канала между стоком и истоком при напряжении на разрядной щине 5, равном V не происходит, и ток опреде0 ляется током обратносмещенного р-п-перехо да стока, что соответствует считыванию «О. При выборе числовой шины 4 и разрядной щины 5 связь между щинами осуществляется через выбранную ячейку 1 па5 мяти и через остальные невыбранные ячейки (фиг. 1).

Рассмотрим случай, когда канал ячейки 1 памяти закрыт (записан «О), а канал остальных ячеек открыт (записана . Ток через невыбранные ячейки не пре0 вышает тока обратносмещенного диода к стоку, что позволяет пренебречь связью между числовыми и разрядными щинами через невыбранные ячейки.

Формула изобретения

35

40

Матричный накопитель для полупроводникового запоминающего устройства, содержащий числовые и разрядные щины, в перекрестиях которйх включены запоминающие транзисторы, истоки которых подключены к соответствующим числовым щинам, а затворы - к соответствующим разрядным щинам, отличающийся тем, что, с целью упрощения накопителя, он содержит выпрямительные диоды, аноды которых сое- 45 динены с затворами соответствующих запоминающих транзисторов, стоки которых подключены к катодам соответствующих выпрямительных диодов.

. 2

ВНИИПИЗаказ 5507/52Тираж 588Подписное

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный накопитель для постоянного запоминающего устройства | 1978 |

|

SU1444890A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1978 |

|

SU1444891A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ НА МДП-ТРАНЗИСТОРАХ С ИЗМЕНЯЕМЫМ ПОРОГОВЫМ ВКЛЮЧЕНИЕМ | 1985 |

|

RU1378681C |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1980 |

|

SU888731A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1982 |

|

SU1108915A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1986 |

|

SU1338688A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОНОП-ЯЧЕЙКИ ПАМЯТИ, ЯЧЕЙКА ПАМЯТИ И МАТРИЧНЫЙ НАКОПИТЕЛЬ НА ЕЕ ОСНОВЕ | 1996 |

|

RU2105383C1 |

| Адресный дешифратор для полупроводникового постоянного запоминающего устройства | 1980 |

|

SU960949A1 |

| Способ записи и считывания информации в МНОП-элементе памяти и матричный накопитель для запоминающего устройства | 1983 |

|

SU1405089A1 |

| Матричный накопитель | 1981 |

|

SU1015440A1 |

Изобретение относится к вычислительной технике и может быть использовано для записи, хранения и считывания информации в вычислительном устройстве. Целью изобретения является упрощение матричного накопителя. Поставленная цель достигается за счет введения выпрямительных диодов 3, аноды которых соединены с соответствующими затворами соответствующих запоминающих транзисторов, стоки которых подключены к катодам соответствующих диодов. 2 ил. РШ1 РШ2 (Л СО ел 00 Ш2 фив. 7

| ЭЛЕКТРОКОНТАКТНОЕ УСТРОЙСТВО ДЛЯ РУДНОТЕРМИЧЕСКОЙ ПЕЧИ С ГРАФИТИРОВАННЫМ ЭЛЕКТРОДОМ | 2020 |

|

RU2748222C1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Ржанов А | |||

| В., Синица С | |||

| П | |||

| Системы памяти на основе МДП и МНОП структур | |||

| - Микроэлектроника, 1977, т | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-07—Публикация

1983-08-03—Подача