(54) ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1968 |

|

SU217718A1 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

| Устройство для деления | 1976 |

|

SU662938A1 |

| Устройство для деления | 1973 |

|

SU456270A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ И ДЕЛЕНИЯ | 1973 |

|

SU385273A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Устройство для вычисления логарифмов | 1972 |

|

SU479110A1 |

| Устройство для деления чисел | 1981 |

|

SU1013948A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

1

Изобретение относится к вычислительной технике и может быть использовано в устройствах измерительной техники.

Известны устройства для деления чисел с преобразованием в число-импульсный код, построенные на счетчиках и схемах И. Однако при делении целочисленных кодов за счет отбрасывания остатка возникают большие ошибки, причем предварительное умножение делимого приводит к увеличению вре- :мени вычисления, особенно для случаев деления без остатка.

Цель изобретения - повышение точности : выполнения операции при сохранении минимального времени выполнения операции. : Сущность изобретения заключается в :том, что в делительное устройство включен .сдвигающий регистр и дополнительный счет чик, выходы разрядов которого соединены соответственно с первыми вxoдa ли трртьей группы схем. И, а выходы третьей группы }схем И соединены соответственно со вто|рой группой шин записи счетчика делимого; установочные входы дополнительного счетчика соединены соответственно с выходами

-четвертой группы схем И; первые входы четвертой группы схем И соеданены с соответствуюшими выходами разрядов сдвигающего регистра, а вторые входы соединены с выходом первой схемы ИЛИ; шина установки О дополнительного - счетчика соединена с единичным выходом старшего разряда счетчика - делителя; шина сдвига сдвигающего регистра соединена со всеми вторыми входами третьей группы схем И и выходом линии задержки; выход старшего разряда сдвигающего регистра соединен со вторым входом второй схемы ИЛИ.

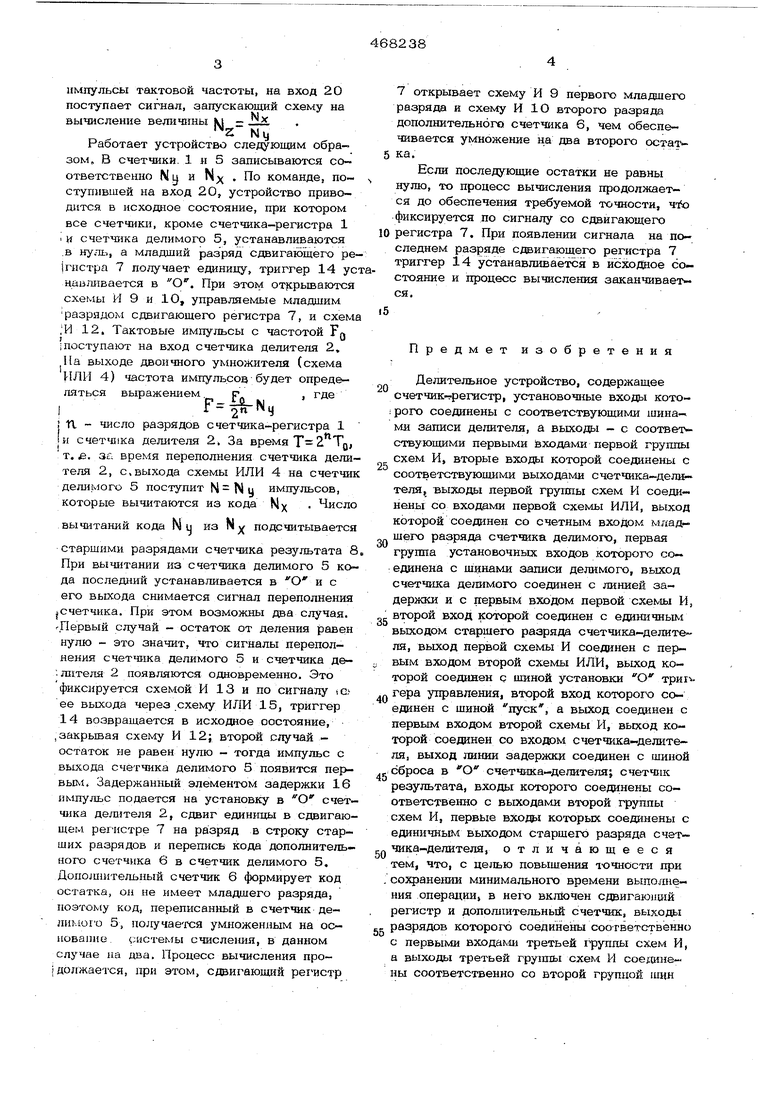

I На чертеже представлена схема устрой;ства.

i Делительное устройство содержит двоичный умножитель, состоящий из счетчика.регистра 1, счетчика делителя 2, схемы И 3 и схемы ИЛИ 4, счетчика делимо1х 5 дополнительного счетчика 6, сдвигающего регистра 7, счетчика результата 8, схем И 9-13, триггера 14, схемы ИЛИ 15 и

элемента задержки 16. На выходы 17 подается код делителя М ц i на входы 18код делимого NX вход 19 поступают импульсы тактовой частоты, на вход 20 поступает сигнал, запускающий схему на вычисление величины М ::: J22L rz Ni, Работает устройство следующим образом, В счетчики. 1 и 5 записываются соответственно Ny и NX По команде, по- ступившей на вход 20, устройство приводится, в исходное состояние, при котором все счетчики, кроме счетчика-регистра 1 i И счетчика делимого 5, устанавливаются .в нуль, а младший разряд сдвигающего ре |гистра 7 получает единицу, триггер 14 ус наалпвается в О . При этом от)к;рьтаются схемы И 9 и 1О, управляемые младшим разрядом сдвигающего регистра 7, и схем :И 12. Тактовые импульсы с частотой FQ i поступают на вход счетчика делителя 2, На выходе двоичного умножителя (схема ИЛИ 4) частота импульсов будет опредепяться Быражеш1ем р , где ,, tl ЧИСЛО разрядов счетчика-регистра 1 |и счетчика делителя 2, За время Т , т. а. з время переполнения счетчика дели теля 2, с,выхода схемы ИЛИ 4 на счетчик делимого 5 поступит N - N у импульсов, которые вычитаются из кода Nj . Число вычитаний кода N и из N подсчитывается старшими разрядами счетчика результата 8 При вычитании из счетчика делимого 5 кода последний устанавливается в О и с его выхода снимается сигнал переполнения счетчика. При этом возможны два случая. Первый случай - остаток от деления равен нулю - это значит, что сигналы переполнения счетчика делимого 5 и счетчика де. лителя 2 появляются одновременно. Это фиксируется схемой И 13 и по сигналу iC ее выхода через схему ИЛИ 15, триггер 14 возвращается в исходное состояние, ,закрывая схему И 12; второй случай остаток не равен нулю - тогда импульс с выхода счетчика делимого 5 появится первым Задержанный элементом задержки 16 импульс подается на установку в О счет чика делителя 2, сдвиг единицы в сдвигаю щем регистре 7 на разряд в строку старших разрядов и перепись кода дополнительного счетчика 6 в счетчик дегшмого 5. Ц.опошштепы1ы счетчик 6 формирует код остатка, он не имеет младшего разряда, поэтому код, переписанный в счетчик делиного 5, получаеГся умноженным на основание ристемы счисле1шя, в данном случае на два. Процесс вычисления про1должается, при этом, сдвигающий регистр 7 открывает схему И 9 первого младшего разряда и схему И 1О второго разряда дополнительного счетчика 6, чем обеспечивается умножение на два второго остатЕсли последующие остатки не равны нулю, то процесс вычисления продолжается до обеспечения требуемой точности, чт фиксируется по сигналу со сдвигающего регистра 7. При появлении сигнала на последнем разряде сдвигающего регистра 7 триггер 14 устанавливается в исходаое состояние и процесс вычисления заканчивается. Предмет изобретения Делительное устройство, содержащее счетчик-грешстр, установочные входы которого соединены с соо-геетствующими щина- ми записи делителя, а выходы - с соответствующими первыми входами первой группы схем И, вторые входы которой соединены с соответствующими выходами счетчика-делителя, выходы первой группы схем И соеди нены со входами первой схемы ИЛИ, выход которой соединен со счетным входом млад.щего разряда счетчика делимого, первая группа установочных входов которого со единена с щинами записи делимого, выход счетч1пса де;шмого соединен с линией задержки и с первым входом первой схемы И, второй вход которой соединен с единичным выходом старшего разряда счетчика-делителя, выход первой схемы И соединен с пер- вым входом второй схемы ИЛИ, выход которой соединен Q щиной установки О триг. гера управления, второй вход которого) соединен с щиной пуск, а выход соединен с первым входом второй схемы И, выход которой соединен со входом счетчика-делителя, выход линии задержки соединен с щиной сброса в О счетчика-делителя} счетчик результата, входы которого соединены соответственно с выходами второй группы схем И, первьш входы которых соединены с единичным выходом старщего разряда счетчика-делителя, отличающееся тем, что, с целью повыщения точности при сохране1ши минимального времени выпо.гп1еиия операции, в негх включен сдвигающий регистр и дополнительный счетчик, выходы разрядов которого соединены соответственно с первыми входакш третьей группы схем И, а выходы третьей гру1шы схем И соеданены соответственно со второй группой шин

записи счетшка депимо1Х ; ycl aнoвoчnыe входал дополнительного счетчика соединены соответствеино с выходами четвертой группы схем И; первые входы четвертой группы схем И соединены с соответствующими выходами разрядов- сдвигающего регистра, а вторые входы соединены с выходами первой схемы ИЛИ; шина установки О дополнительного счетчика соединена с единнчньм выходом старшего разряда сче тчика-дели- теля; шина сдаига сдвигающего регистра соединена со всеми вторыми входами третьей груш1Ы схем И и выходом линии задержки; выход 1 старшего разряда сдвигающего регистра соединен со вторым входом второй схемы ИЛИ.

Авторы

Даты

1975-04-25—Публикация

1972-10-23—Подача