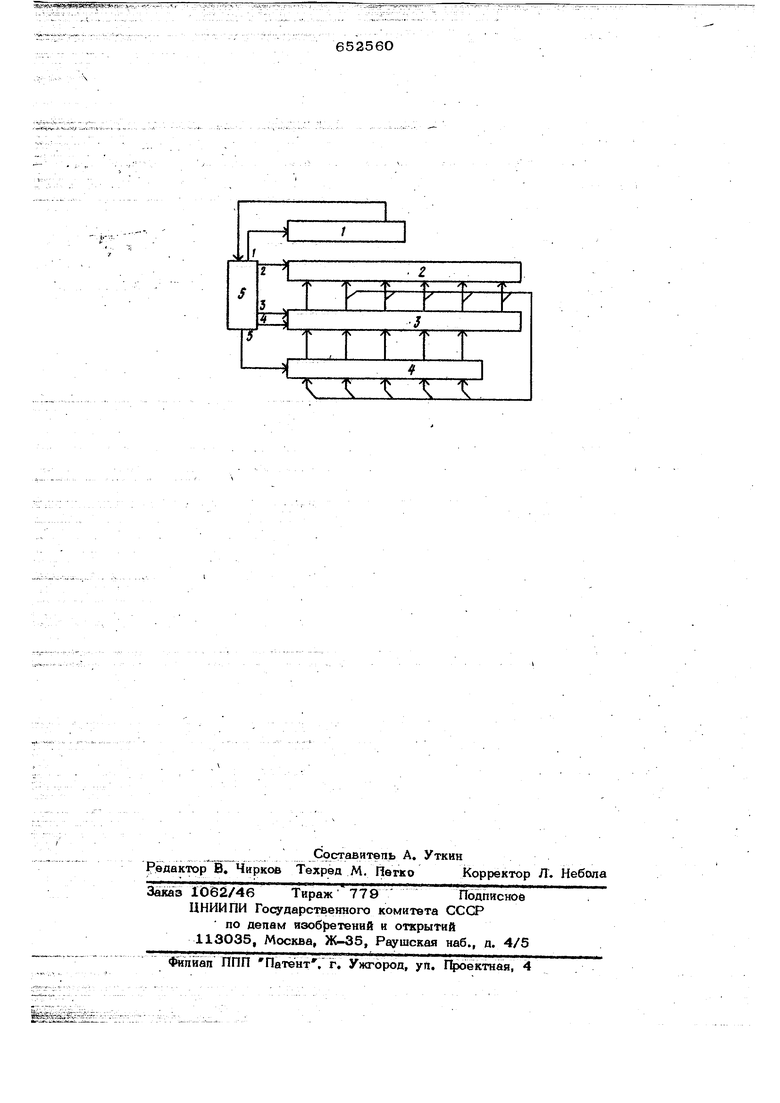

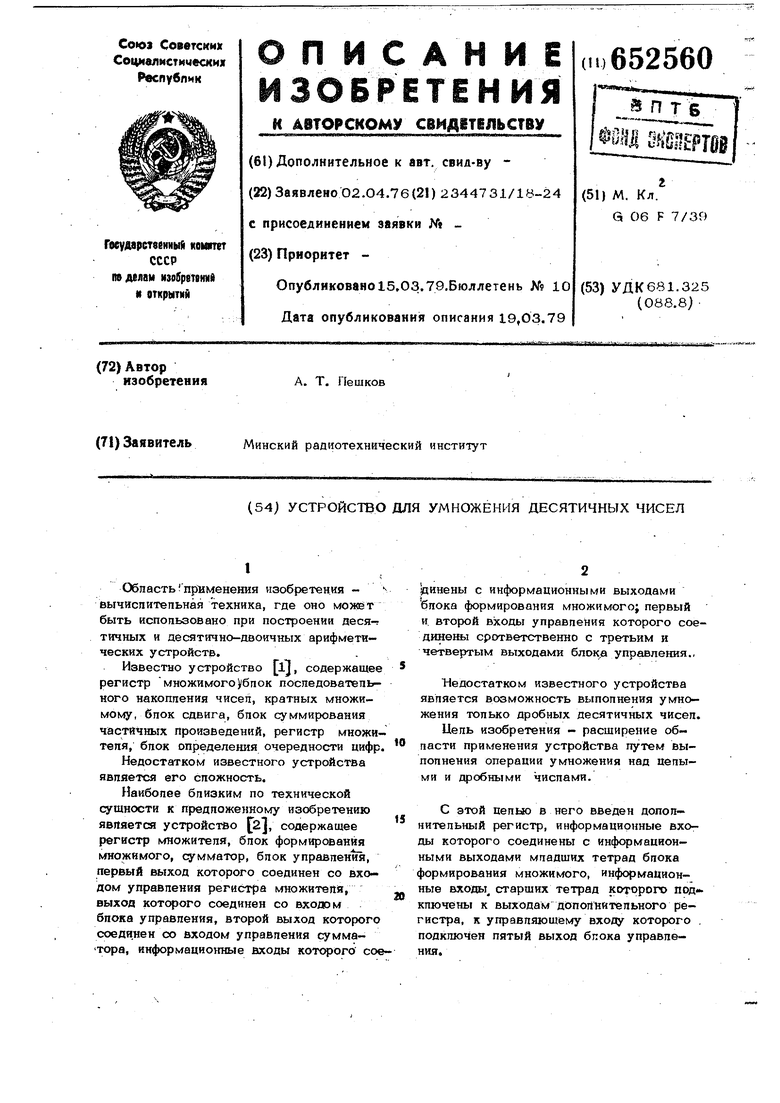

Областьпртаменения изобретения вычислительная техника, где оно может быть использовано при построении десятинных и десятично-двоичных арифметических устройств. Известно устройство p.J, содержащее регистр множимого блок последовательного накопления чисел, кратных множимому, блок сдвига, блок суммирования частичных произведений, регистр множи теля, блок определения очередности цифр Недостатком известного устройства является его сложность. Наиболее близким по технической сущности к предложенному изобретению является устройство , содержащее регистр множителя, блок формирования множимого, сумматор, блок управления, первый выход которого соединен со входом управления регистра множитейй, выход которого соединен со входом блока управления, второй выход которого соединен со входом управления сумматора, информационные входы которого со динены с информационными выходами блока формирования множимого; первый и второй входы управления которого соединены срответственно с третьим и четвертым выходами блока управления,, Недостатком известного устройства является возможность выполнения умножения только дробных десятичных чисел. Цель изобретения - расширение области применения устройства путем выполнения операции умножения над целыми и дробными числами. С этой целью в него введен дополнительный регистр, информационные входы которого соединены с информационными выходами младших тетрад блока формирования множимого, информационные входы старших тетрад которого под ключены к выходам дополнительного регистра, к управляющему входу которого , подключен пятый выход бпока управления. На чертеже приведена структурная схема устройства дпя умножения десятичных .чисел. Устройство содержит регистр множителя 1, сумматор 2, блок формирования мнbжи:vfoгo 3, дополнительный регистр 4)блок управления 5. Устройство работает следующим образом. Перед началом умножения в регистр множителя 1 заносится десятичный код: множителя, в младшие тетрады блока формирования множимого 3 заносится ко ЙНЬЖИМОГО. Умножение осуществляется за чиспо циклов, равное разрядности десятичных операндов, при этом в каждом цикле осу ществляется умножение множимого на один десятичный разряд множителя, начиная с младшего. Каждый цикл состоит из четырех тактов по числу разрядов, представления десятичных цифр в двоичн десятичной системе 8, 4, 2, 1. Начинается умножение с цикла обработки младшего разряда множителя. На первом Такте вырабатывается сигнал на пятом м 1ходе блока управления и код цифр, зафиксированный в младших тетрадах блока 5, заносится в регистр 4. Одновременно, если присутствует сигнал на входе блока управления Б вырабатывается сигнал на втором выходе этого же блока управления, обеспечиваюший десятичное сложение содержимого сумматора 2 с кодом блока 3, Если сигнал на входе блока управления отсутствует (младший разряд младшей тетрады регистра мно)кителя имеет нулевое значение) , то сигнал на втором выходе блока управления не появляется. С задержкой на время передачи кода из блока 3 в блок 2 относительно момента, в который формируется сигнал на втором выходе блока управления, этот же блок управления вырабатывает сиграпы на своих пер1 цикл . . 1,такт Бл2: ОООО 0000 ОООО ОООО 4- ОООО ОООО 10ОО 0101 2 такт Бл2: ОООО ОООО 100О О1О1 + ОООО ОООО ОООО ОООО 3такт Бл2: ОООО ОООО lOOO. 01О1 + ОООО ОООО ОООО ОООО 4такт Бл2: ОООО ОООО ЮОО 0101 ОООО 0110 1000 ОООО Bri2: ОООО 0111 ОНО 0101 60 вом и четвертом выходах, что обеспечивает сдвиг содержимого регистра множителя на один двоичный разряд вправо и умножение десятичного кода, нмеюи егося в это время в блоке 3 на два. На этом заканчивается первый такт первого шкла, на котором отрабатывается младший Двоичный разряд младшей десятичной цифры множителя. Второй и третий такты первого цикла вьшояняются так же, как и первый такт, но при этом в начале такта не вырабатывается сигнал на пятом выходе блокауправления и в регистре 4 в течение всего цикла сохраняется значение, принятое в него в начале первого такта этого UHKjja. Четвертый такт выпол1ияется так же, как и третий и второй с той лишь разницей, что на этом такте вместо сиг«ала на выходе четыре блока управления формируется сигнал на выходе 3 этого же блока управления. Этот сигнал1 поступая на первый вход блока 3 обеспечивает прием в его старшие тетрады (все тетрады, кроме младшей) кода из регистра 4, при этом в младшей тетраде блока 3 устанавливается нулевое значение. С завершением выполнения четвертого такта заканчивается первый цикл работы устройства. Все остальные циклы выполняются аналогично первому. Результат умножения будет сформирован в сумматоре после завершения четвертого такта цикла обработки старшей нифры множителя. Работу данного устройства можно пояснить на примере выполнения умножения двух конкретных десятичных чисел :Х 39 (множитель) и (множиMoej, В -этом .случае в системе 8, 4, 2, 1 имеем: ЗГ ООН lOOlj у ЮОО 0101} Действии на отдельных тактах двух циклов можно представить следующим образом: БлЗ: ОООО ОООО 1000 О101 Бл4: ОООО ЮОО 0101 МрБл БпЗ: ОООО OPOI 0111 ОООО МрБл БлЗ: ОООО ООН 01ОО ОООО Мр Бл1 0БлЗ: ОООО ОНО ЮОО ОООО МрБл1 1 БлЗ: ОООО ЮОО 01О1 ОООО

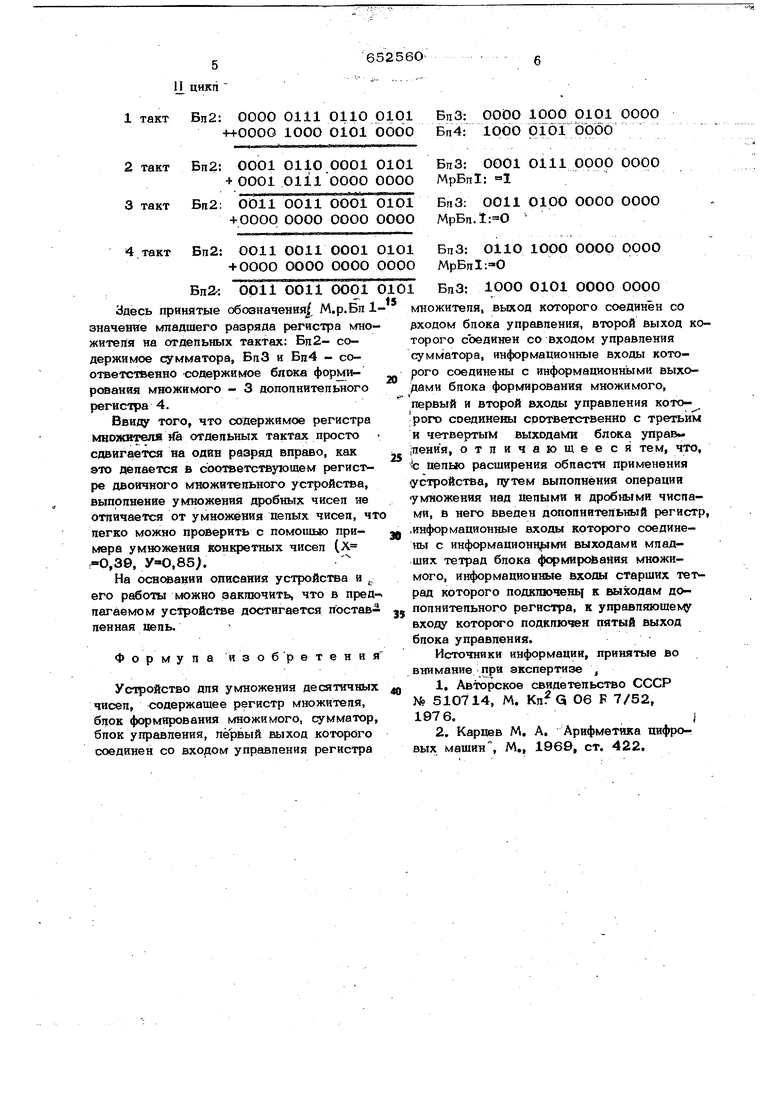

5 11 цикл Бл2: 0000 0111 0110 1 такт ++0000 10ОО 0101 Бп2: 0001 0110 0001 2 такт + 0001 0111 оООО Бп2: О011 ООН OOOl 3 такт + 0000 ОООО ОООО Бп2: ООН ООН 0001 fOOOO ОООО ОООО Бп2-. ООН ООН ОО01 Здесь принятые обозначения М.р.Бп 1 значение ктадшего разряда регистра множитепя на сугдепьных тактах: Бл2- содержимое сумматора, БдЗ и Бл4 - соответственно содержимое блока формирсшання множимого - 3 дополнительного регистра 4. Ввид/ того, что содержимое регистра множителя jfe отдельных тактах просто сдвигается на один разряд вправо, как это дапается в соответстрвующем регисгре двоичного множительного устройства, выполнение умножения дробных чисел не отличается от умножения целых чисел, чт легко можно проверить с помощью примера умножения конкретных чисел (Х -0,39, ,85;. На основании описания устройства и , его работы можно заключить, что в предлагаемом устройстве достигается поставленная цель. Формула йзобретения Устройство для умножения десятичных чисел, содержащее регистр множителя, блок формирования множимого, сумматор, блок управления, первый которого соединен со входом управления регистра

65256О БпЗ: ОООО 1000 0101 ОООО 1 Бп4: 1ООО 0101 ОрОО О БпЗ: 0001 0111 poop ООрО 1 МрБл1: «1 БпЗ: ООН О10О ОООО ОООО МрБп. О БлЗ: ОНО 1000 ОООО ОООО 1 МрБл1: 0 О БлЗ: ЮОО 0101 ОООО ОООО 1 множителя, выход которого соединен со эходом блока управления, второй выход которого соединен со входом управления сумматора, информационные входы которого соединены с информационными выходами блока формирования множимого, первый и второй входы управления которого соединены соответственно с третьим и четвертым выходами блока управ.ления, отличающееся тем, что, с цель« расширения области применения устройства, путем выполнения операции умножения над целыми и дробными числами, в него введен дополнительный регистр, .информационные входы которого соединены с информационными выходами младших тетрад блока формирования множимого, информационные входы старших тет рад которого подключень| к шлходам дополнительного регистра, к управляющек входу которого подключен пятый выход блока управления. Источники информации, принятые во внимание при экспертизе 1,Автчэрское свидетельство СССР № 510714, М. 06 F 7/52, 1976,i 2.Карцев М. А. Арифметика цифровых машин, М,, 1969, ст. 422.

65256O

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1985 |

|

SU1309019A1 |

| Устройство для умножения десятич-НыХ чиСЕл | 1979 |

|

SU817704A1 |

| Устройство для умножения десятичных чисел | 1981 |

|

SU1016780A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Устройство для умножения десятичных чисел | 1975 |

|

SU723571A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Устройство для умножения чисел | 1989 |

|

SU1817091A1 |

| Устройство для умножения | 1989 |

|

SU1668979A1 |

| Множительное устройство | 1982 |

|

SU1053104A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый КОд | 1979 |

|

SU809151A1 |

r-T

И

.л , лч/14

. z

Авторы

Даты

1979-03-15—Публикация

1976-04-02—Подача