1

Изобретение относится к вычислительной технике.

Известны устройства управления для цифровой вычислительной машины, содержащие регистр запросов, установочные входы которого подключены к входам запросов устройства, регистр маски, установочные входы которого подключены к входам масок устройства, схему предварительного преобразования, входы которой подключены к выходам регистров запросов и маски, последовательно соединенные шифратор, регистр номера запроса и блок формирования адресов и счетчик адреса команд, выходы которого соединены с адресными выходами устройства и соответствуюпцими входами блока формирования адресов, а входы подключены к адресным входам устройства.

Все известные устройства управления требуют значительного объема оборудования для организации процесса выделения приоритетных запросов.

Цель изобретения - упрощение устройства.

Предлагаемое устройство отличается от известных тем, что оно содержит элемент «НЕ, включенный между выходом старшего разряда схемы предварительного преобразования и соответствующим входом блока формирования адресов, выходы схемы предварительного преобразования соединены С одноименными входами счетчика адреса команд, выходы которого соединены со входами шифратора и одноименными сбросовыми входами регистра запросов.

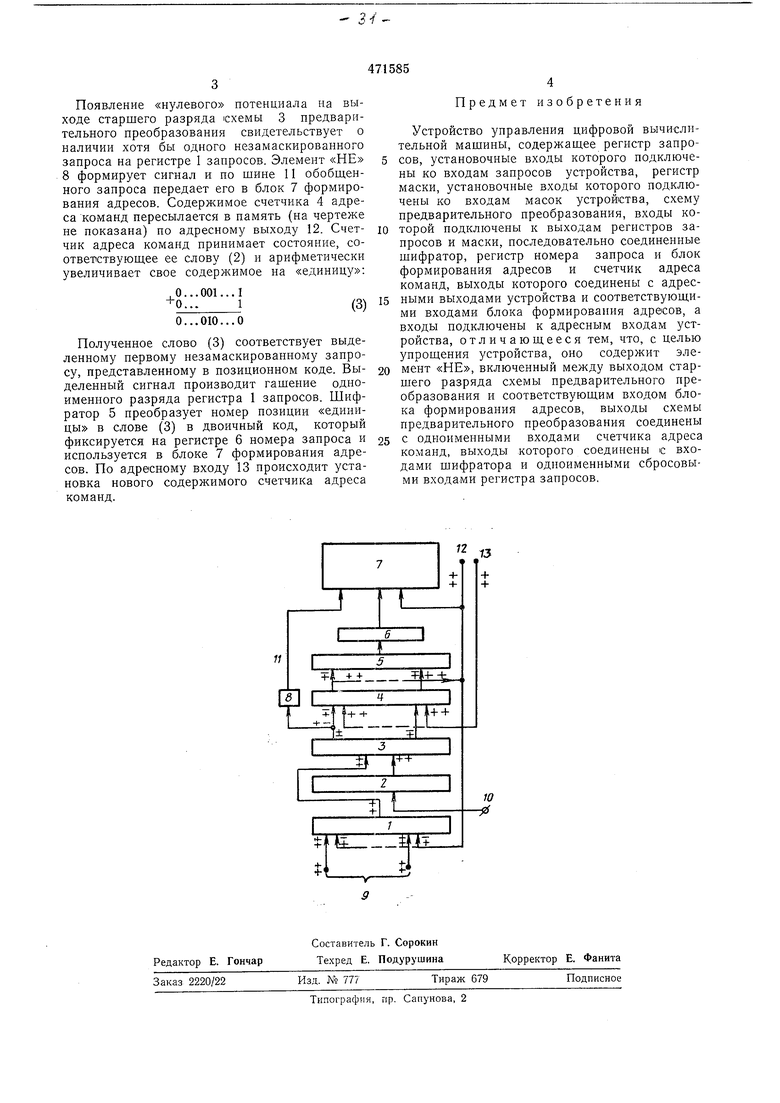

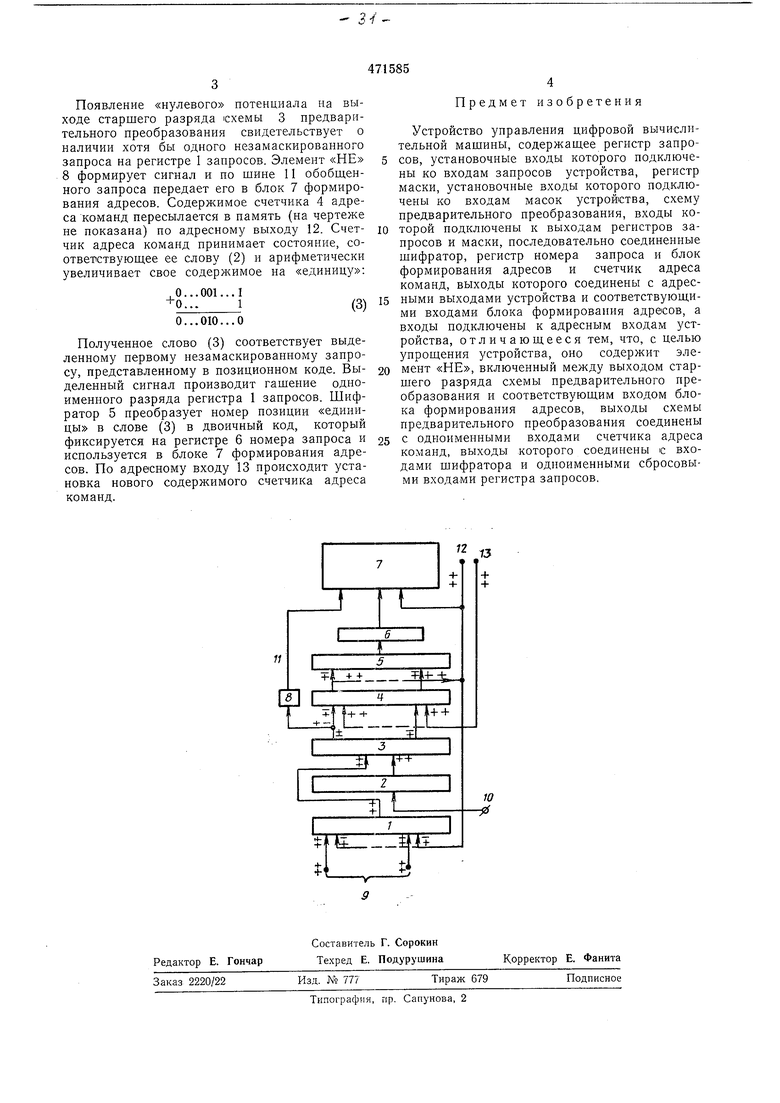

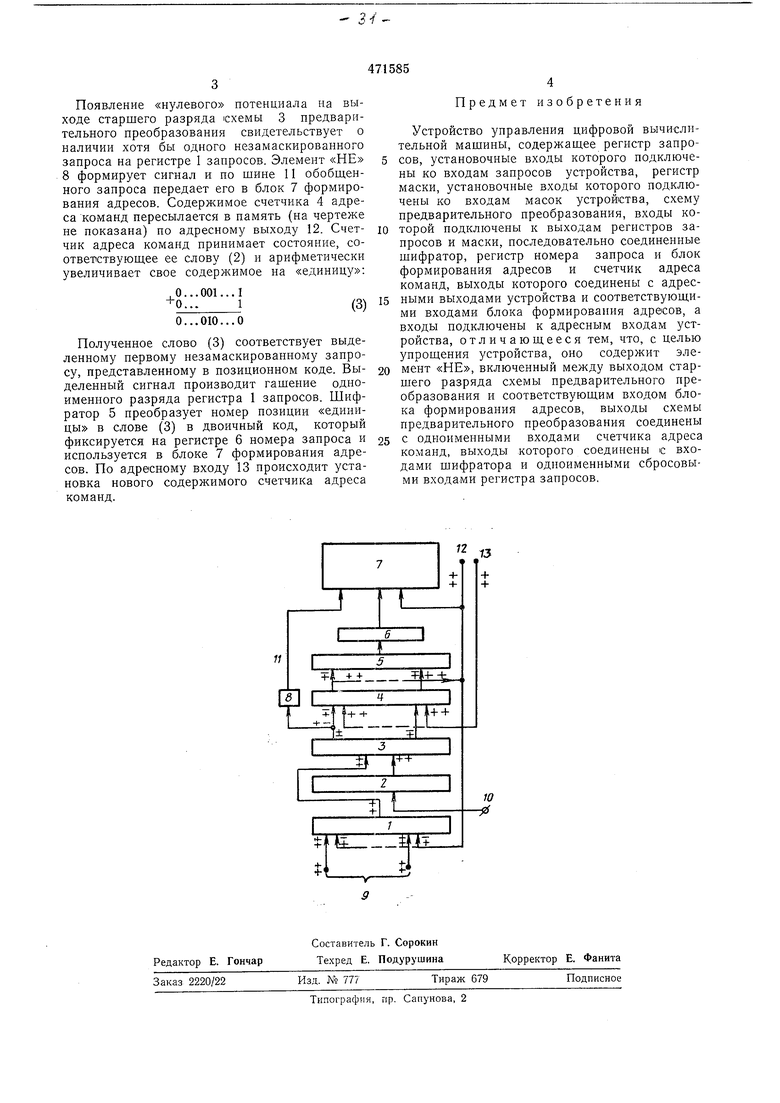

На чертеже приведена блок-схема устройства управления. Она содержит регистр 1 запросов, регистр 2 маски, схему 3 предварительного преобразования, счетчик 4 адреса команд, шифратор 5, регистр 6 номера запроса, блок 7 формирования адресов, элемент «НЕ 8, входы 9 запросов, входы 10 масок, шину 11 обобщенного запроса, адресные выходы 12 и адресные входы 13.

Устройство работает следующим образом. По входам 9 запросов и масок 10 происходит установка регистров запросов 1 и маски 2.

Схема 3 предварительного преобразования формирует слово разрешенных запросов, которое в общем случае может быть представлено следующим расположением значащих разрядов: X... Х10. . . 0. (1) и инвертирует непрерывную последовательность «нулей младших разрядов слова (1), а остальные разряды, вне зависимости от их значений,

t «обнуляет : О... 001 ... 1. (2) Появление «нулевого потенциала на выходе старшего разряда схемы 3 предварительного преобразования свидетельствует о наличии хотя бы одного незамаскированного запроса на регистре 1 запросов. Элемент «НЕ 8 формирует сигнал и по шине 11 обобшенного запроса передает его в блок 7 формирования адресов. Содержимое счетчика 4 адреса команд пересылается в память (на чертеже не показана) по адресному выходу 12. Счетчик адреса команд принимает состояние, соответствуюидее ее слову (2) и арифметически увеличивает свое содержимое на «единицу : О... 001... I 0...010...0 Полученное слово (3) соответствует выделенному первому незамаскированному запросу, представленному в позиционном коде. Выделенный сигнал производит гашение одноименного разряда регистра 1 запросов. Шифратор 5 преобразует номер позиции «единицы в слове (3) в двоичный код, который фиксируется на регистре 6 номера запроса и используется в блоке 7 формирования адресов. По адресному входу 13 происходит установка нового содержимого счетчика адреса команд. Предмет изобретения Устройство управления цифровой вычислительной машины, содержашее регистр запросов, установочные входы которого подключены ко входам запросов устройства, регистр маски, установочные входы которого подключены ко входам масок устройства, схему предварительного преобразования, входы которой подключены к выходам регистров запросов и маски, последовательно соединенные шифратор, регистр номера запроса и блок формирования адресов и счетчик адреса команд, выходы которого соединены с адресными выходами устройства и соответствующими входами блока формирования адресов, а входы подключены к адресным входам устройства, отличающееся тем, что, с целью упрощения устройства, оно содержит элемент «НЕ, включенный между выходом старшего разряда схемы предварительного преобразования и соответствующим входом блока формирования адресов, выходы схемы предварительного преобразования соединены с одноименными входами счетчика адреса команд, выходы которого соединены с входами шифратора и одноименными сбросовыми входами регистра запросов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поиска информации в памяти | 1985 |

|

SU1309041A1 |

| Устройство для обработки прерываний | 1985 |

|

SU1282124A1 |

| Микропрограммное устройство для обработки прерываний | 1983 |

|

SU1126956A1 |

| Запоминающее устройство | 1980 |

|

SU942141A2 |

| Устройство для сопряжения каналов ввода-вывода с оперативной памятью | 1986 |

|

SU1322298A2 |

| Устройство для сопряжения каналов ввода-вывода с оперативной памятью | 1985 |

|

SU1267427A1 |

| Устройство для поиска информации в ассоциативной памяти | 1988 |

|

SU1617460A1 |

| Устройство для контроля операций ввода-вывода | 1989 |

|

SU1686450A1 |

| Устройство для предварительной обработки операндов переменной длины | 1984 |

|

SU1269147A1 |

| Приоритетное устройство | 1984 |

|

SU1260956A1 |

Авторы

Даты

1975-05-25—Публикация

1972-02-24—Подача