,

Изобретение относится к вычислительной технике,в частности к устройствам, состоящим из некоторого числа каналов ввода-вывода и устройства управления, обслуживающего в режиме разделения времени эти каналы, причем каналы могут быть автономными либо встроенными, и является усовершенствованием известного устройства по авт. св. 129961.

Целью изобретения является повышение достоверности передачи информации .

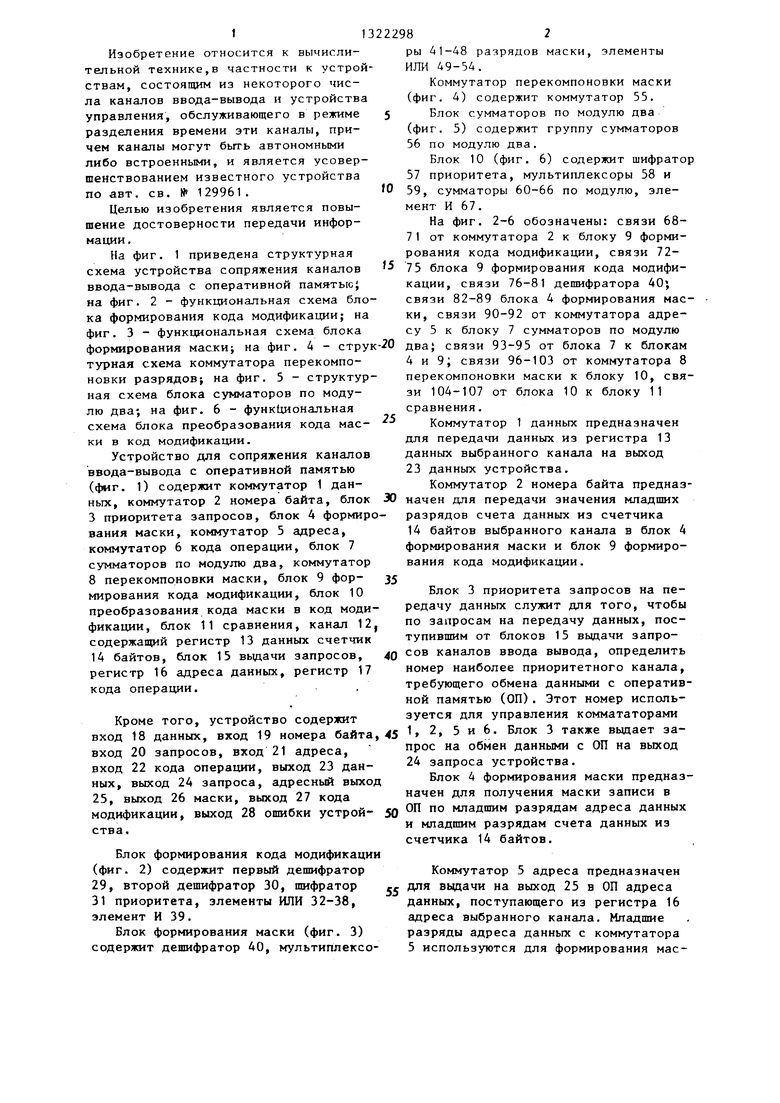

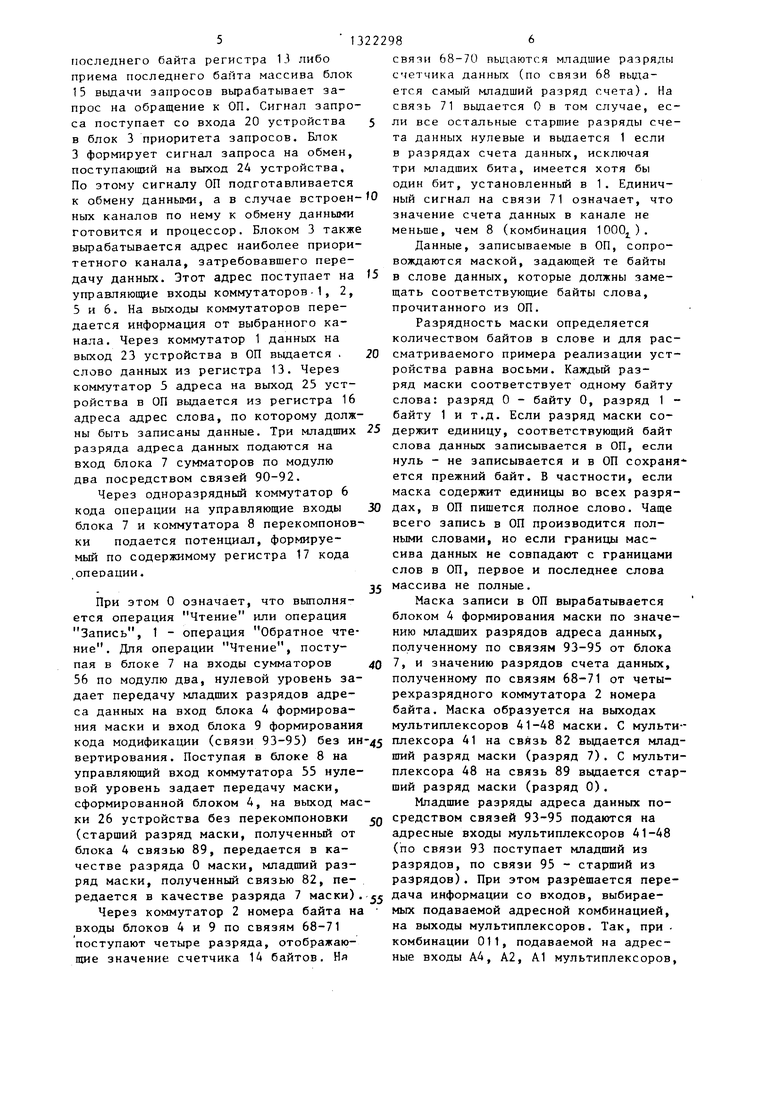

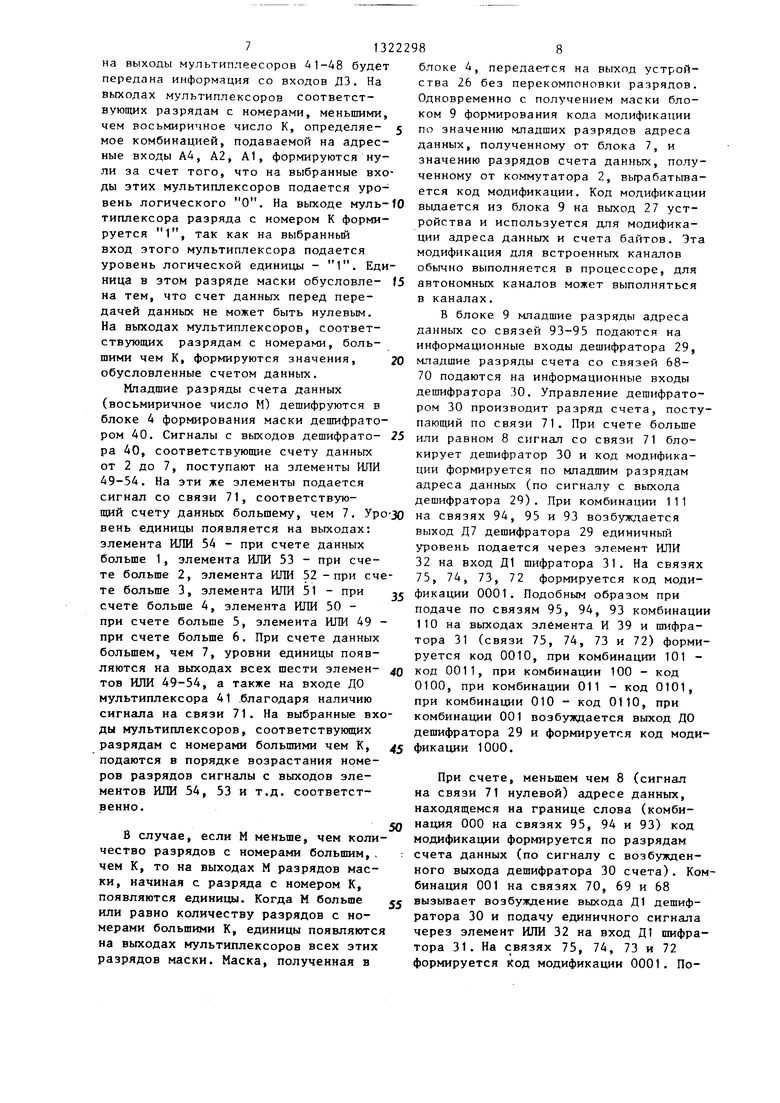

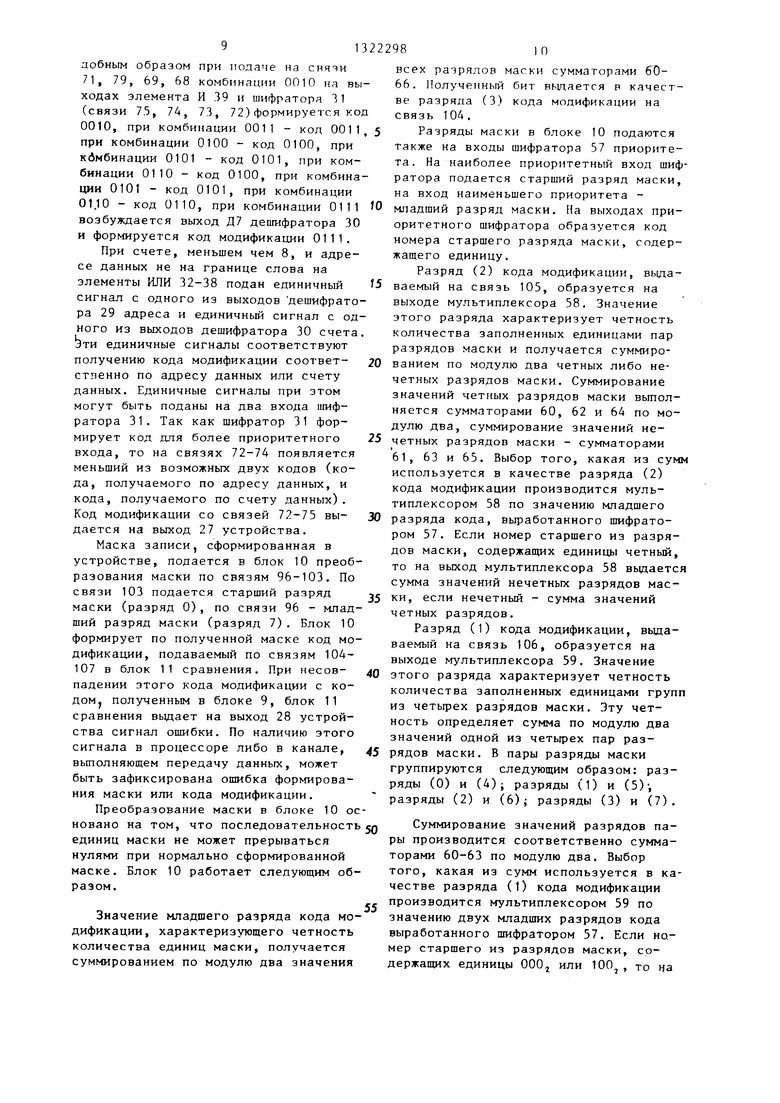

На фиг. 1 приведена структурная схема устройства сопряжения каналов ввода-вывода с оперативной памятьюJ на фиг. 2 - функциональная схема блока формирования кода модификации; на фиг. 3 - функциональная схема блока формирования маски; на фиг. 4 - струк турная схема коммутатора перекомпоновки разрядов-, на фиг. 5 - структурная схема блока сумматоров по модулю два; на фиг. 6 - функциональная схема блока преобразования кода мае ки в код модификации.

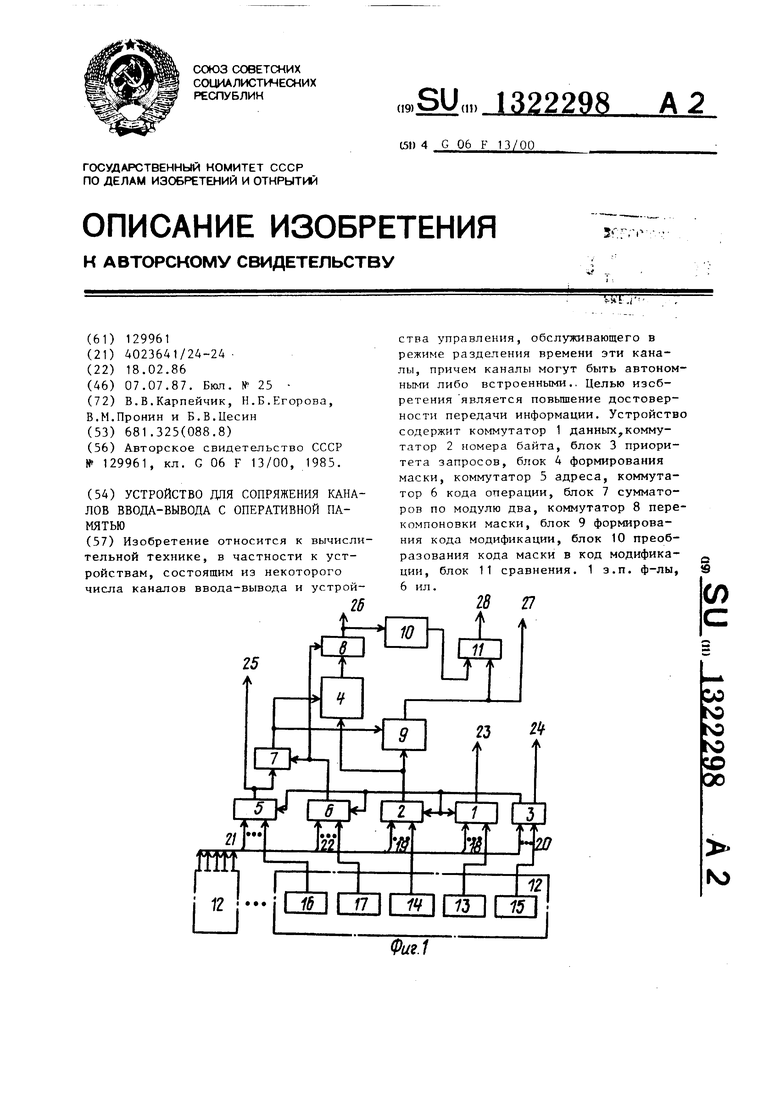

Устройство для сопряжения каналов ввода-вывода с оперативной памятью (фиг. 1) содержит коммутатор 1 данных, коммутатор 2 номера байта, блок 3 приоритета запросов, блок 4 формирования маски, коммутатор 5 адреса, коммутатор 6 кода операции, блок 7 сумматоров по модулю два, коммутатор 8 перекомпоновки маски, блок 9 фор- мирования кода модификации, блок 10 преобразования кода маски в код модификации, блок 11 сравнения, канал 12 содержащий регистр 13 данных счетчик 14 байтов, блок 15 выдачи запросов, регистр 16 адреса данных, регистр 17 кода операции.

Кроме того, устройство содержит вход 18 данных, вход 19 номера байта вход 20 запросов, вход 21 адреса, вход 22 кода операции, выход 23 данных, выход 24 запроса, адресный выход 25, выход 26 маски, выход 27 кода модификации, выход 28 ошибки устрой- ства.

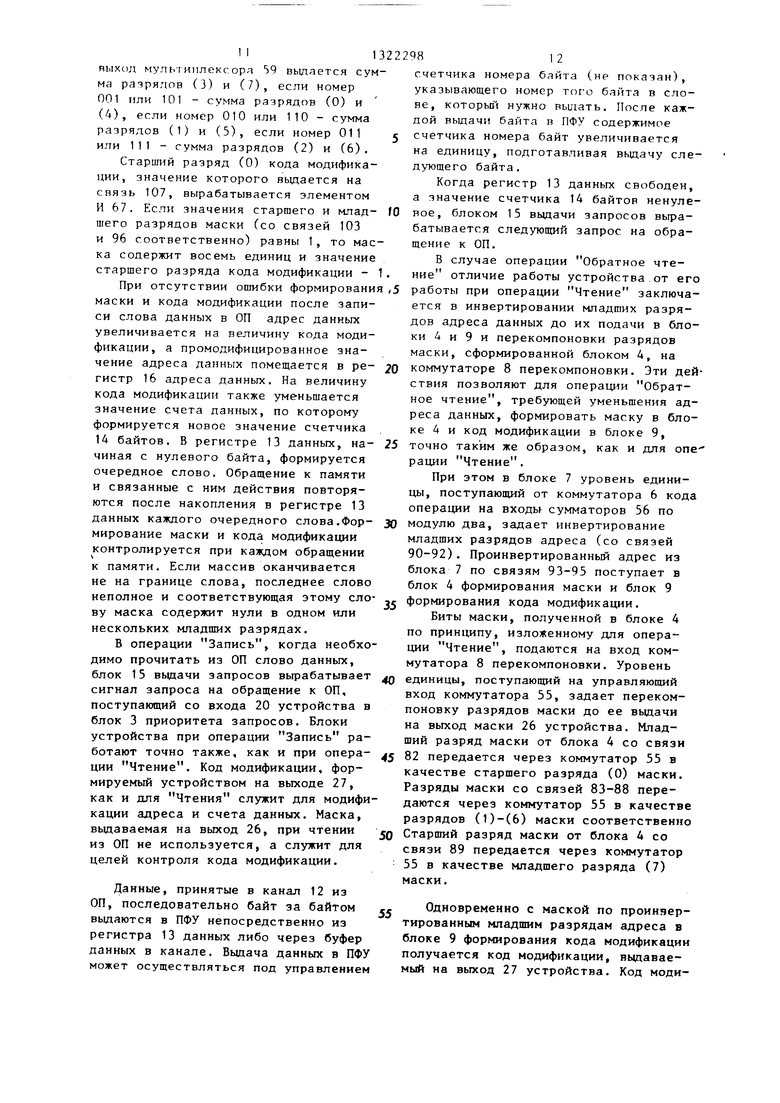

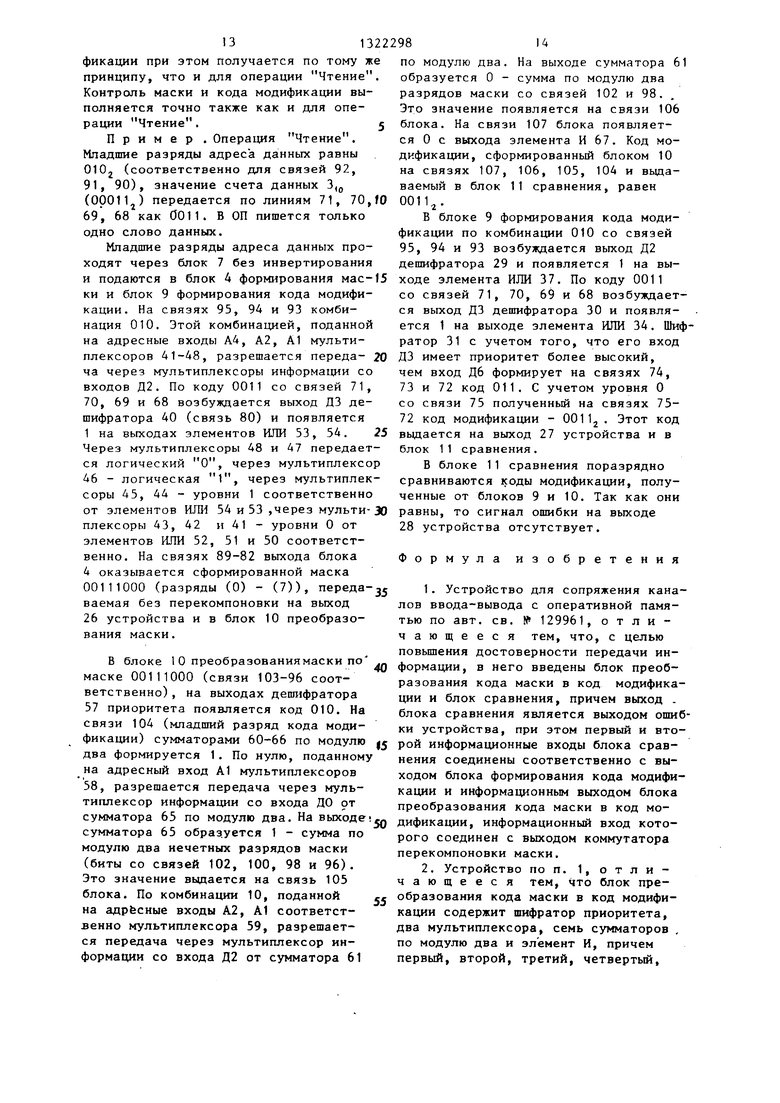

Блок формирования кода модификации (фиг. 2) содержит первый дешифратор 29, второй дешифратор 30, шифратор 31 приоритета, элементы ИЛИ 32-38, элемент И 39.

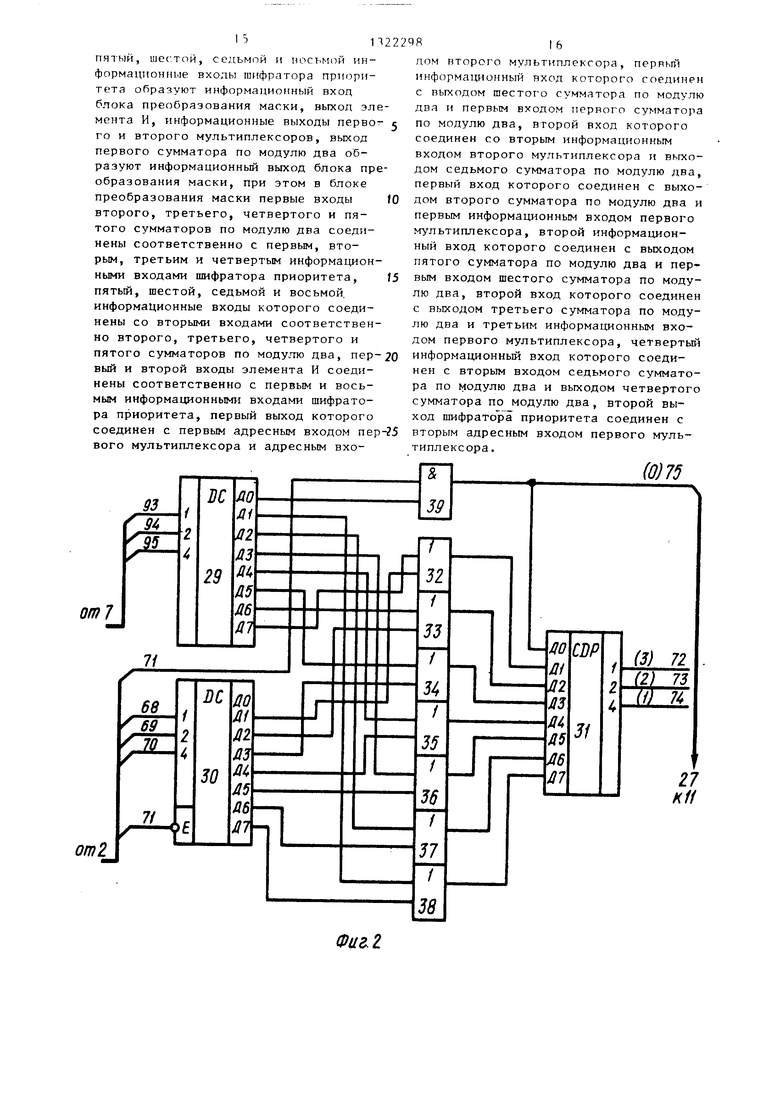

Блок формирования маски (фиг. 3) содержит дешифратор 40, мультиплексо25

5 О

-20 30 35 40

45 50

ры 41-48 разрядов маски, элементы ИЛИ 49-54.

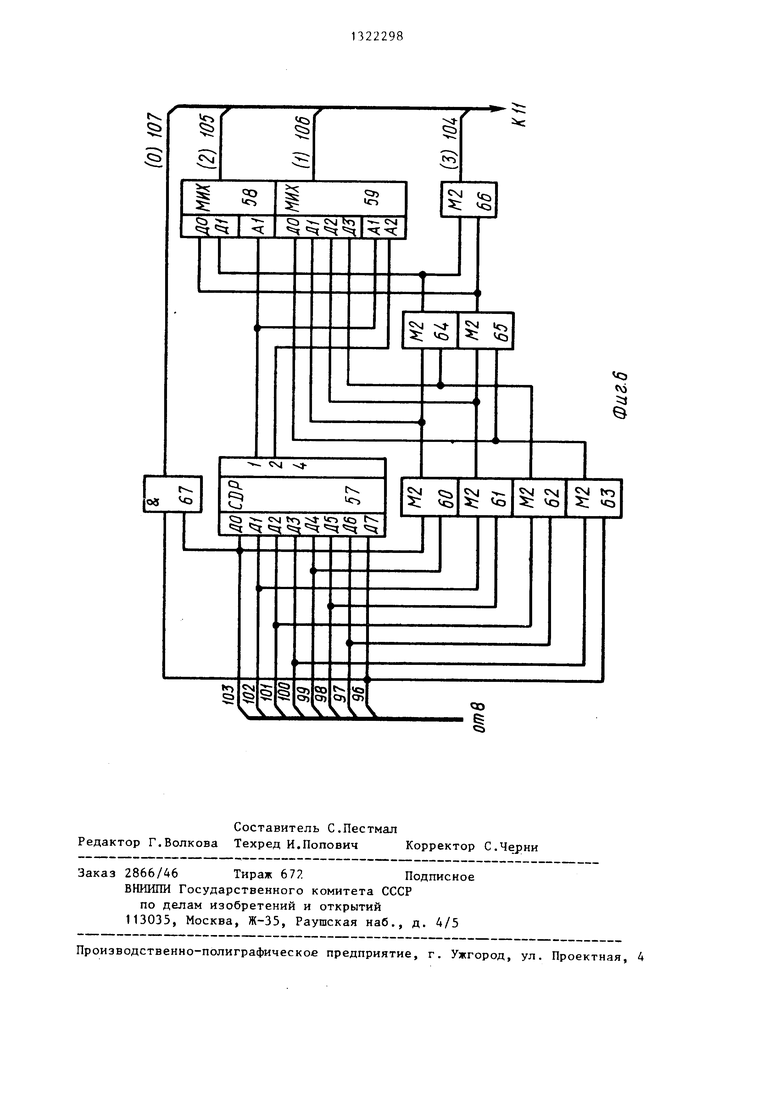

Коммутатор перекомпоновки маски (фиг. 4) содержит коммутатор 55.

Блок сумматоров по модулю два (фиг. 5) содержит группу сумматоров

56по модулю два.

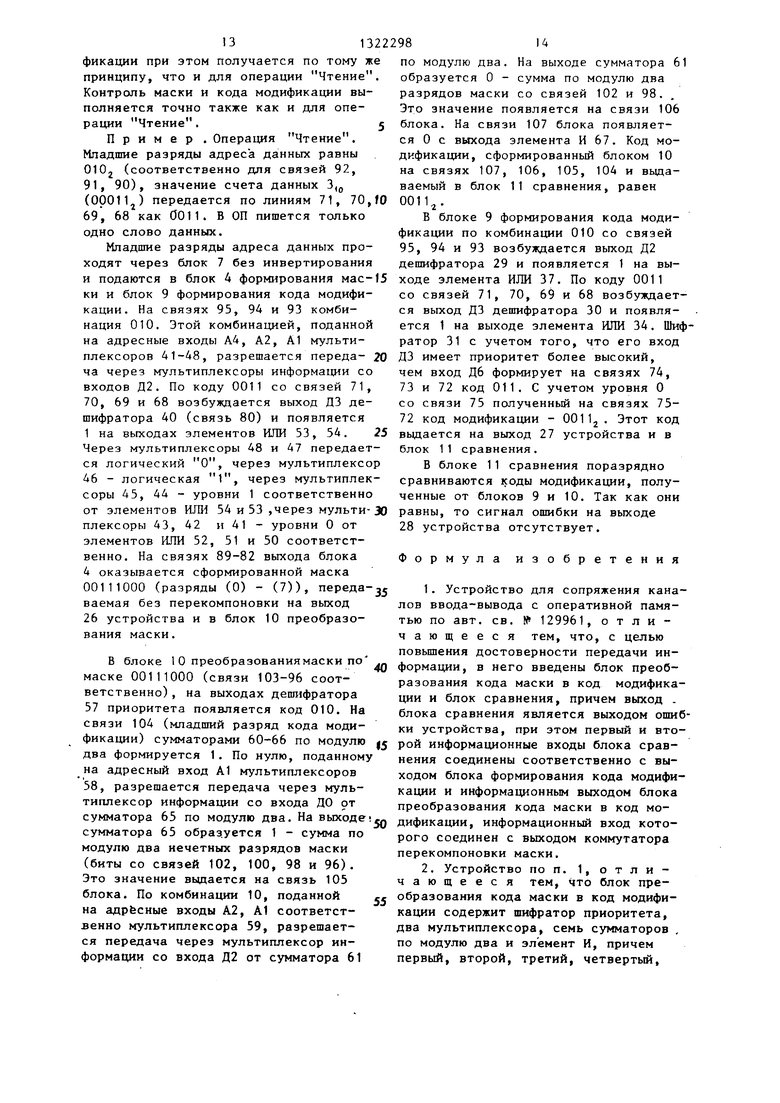

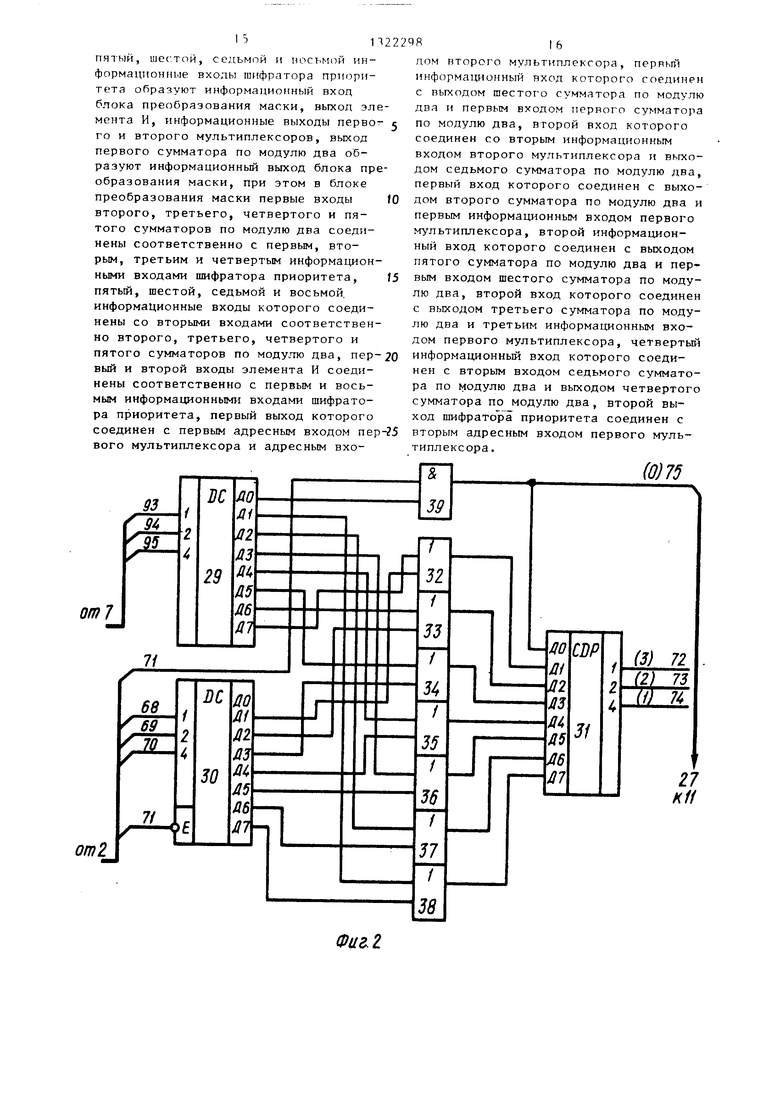

Блок 10 (фиг. 6) содержит шифратор

57приоритета, мультиплексоры 58 и 59, сумматоры 60-66 по модулю, элемент И 67.

На фиг. 2-6 обозначены: связи 68- 71 от коммутатора 2 к блоку 9 формирования кода модификации, связи 72- 73 блока 9 формирования кода модификации, связи 76-81 дешифратора 40; связи 82-89 блока 4 формирования маски, связи 90-92 от коммутатора адресу 5 к блоку 7 сумматоров по модулю два; связи 93-95 от блока 7 к блокам

4и 9; связи 96-103 от коммутатора 8 перекомпоновки маски к блоку 10, связи 104-107 от блока 10 к блоку 11 сравнения.

Коммутатор 1 данных предназначен для передачи данных из регистра 13 данных выбранного канала на выход

23данных устройства.

Коммутатор 2 номера байта предназначен для передачи значения младших разрядов счета данных из счетчика 14 байтов выбранного канала в блок 4 формирования маски и блок 9 формирования кода модификации.

Блок 3 приоритета запросов на передачу данных служит для того, чтобы по запросам на передачу данных, поступившим от блоков 15 выдачи запросов каналов ввода вывода, определить номер наиболее приоритетного канала, требующего обмена данными с оперативной памятью (СП). Этот номер используется для управления коммататорами 1, 2, 5 и 6. Блок 3 также выдает запрос на обмен данными с ОП на выход

24запроса устройства.

Блок 4 формирования маски предназначен для получения маски записи в ОП по младшим разрядам адреса данных и младшим разрядам счета данных из счетчика 14 байтов.

Коммутатор 5 адреса предназначен для задачи на выход 25 в ОП адреса данных, поступающего из регистра 16 адреса выбранного канала. Младшие разряды адреса данньпс с коммутатора

5используются для формирования маекн и КОЛЯ м.1лификации в блоках А и 9 соответственно.

Олнора-эрядный коммутатор 6 кода операции предназначен для передачи разряда кода операции из регистра 17 кода операции канала на соответствующие входы блока 7 сумматоров по модулю два и коммутатора 8 перекомпоновки маски. Разряд кода операции определяет операцию, вьтолняемую каналом,fO данных, которое передается под управследующим образом: О - операция Чтение или Запись ; 1 - операция Обратное чтение.

Коммутаторы 1, 2, 5 и 6 выполнены на мультиплексорах, на адресные входы 15 которых поступает номер выбранного канала от блока 3 приоритета запросов. Этот номер задает передачу через мультиплексор на его выход информации от нужного канала.

Блок 7 сумматоров по модулю два служит для получения инвер тирован- ных младших разрядов адреса данных для операции Обратное чтение, выполняемой каналом, и пеоепачи без 25 инвертирования через блок младйих разрядов адреса данных в случае операции Чтение или операции Запись,

Обратное чтение - операция ввода данных из ПФУ в ОП, при которой адрес данных и значение счетчика дан ных в ходе операции уменьшаются на

Коммутатор 8 перекомпоновки маски служит для перестановки, в случае one- 30 код модификации.

рации Обратное чтение, разрядов При начальной загрузке информации маски записи в ОП, полученной в блоке 4 формирования маски. Коммутатор 8 передает на выход маски 26 устройства либо непосредственно маску, сфор- j мированную блоком 4 (в случае операций Чтение и Запись), либо маску с перекомпонованными разрядами (в случае операции Обратное чтение).

Блок 9 формирования кода модифи- 40 кации предназначен для получения (по младшим разрядам адреса данных и

из КСК в канал 12 код операции передачи данных, вьтолняемой каналом, по мещается в регистр 17 кода операции, начальный адрес данных - в регистр 16 адреса данных, начальное значение счетчика данных - в счетчик 14 байтов

Одновременно с занесением адреса данных в регистр 16 адреса данных младшие разряды адреса данных, указы вающие номер байта в слове, заносятся в счетчик номера байта (не показан) . Количество таких разрядов определяется длиной слова ОП и при восьмибайт- ном слове ОП этих разрядов - три.

счета данных) кода модификации, определяющего количество байтов, передаваемое в слове обмена с ОП, и чи полученного кода на выход 27 устройства.

Блок 10 служит для получения кода модификации из маски, сформированной устройством. Этот код модификации в 50 блоке 11 сравнения поразрядно сравнивается с кодом модификации, вьфа- ботанным блоком 9.

Одновременно с занесением адреса данных в регистр 16 адреса данных младшие разряды адреса данных, указывающие номер байта в слове, заносятся в счетчик номера байта (не показан) . Количество таких разрядов определяется длиной слова ОП и при восьмибайт- ном слове ОП этих разрядов - три.

Затем начинается передача данных. В операции Чтение данные из ПФУ последовательно байта за байтом принимаются в канал и непосредственно с

шин интерфейса либо через буфер данных в канале передаются в регистр 13 данных. Данные размещаются в регистре 13 под управлением счетчика номера Устройство работает следующим об- „ байта, содержимое которого после при- разом.нятия байта данных увеличивается на

Перед началом выполнения операции, единицу, подготавливая прием следую- требующей. обмена данными, произво- щего байта. Регистр имеет размер дится .загрузка в канал 12 управляющей слова обмена с ОП. После заполнения

информации, нео&ходимой для обмена. В каналах ЭВМ единой системы (ЕС) такая информация хранится в командном слове канала (КСК), в котором задаются: код команды, которую должно выполнять периферийное устройство (ПФУ), начальный адрес байта ОП,с которого должен начаться обмен} начальное значение счетчика того количества байтов

лением текущего КСК.

Код команды из КСК при этом задает каналу выполнение одной из следующих трех операций передачи данных:

Запись - операция вывода данных из ОП в ПФУ, при которой адрес байта данных в ходе операции увеличивается, а значение счетчика данных уменьшается в ходе операции на количество передаваемых байтов (код модификации),

Чтение - операция ввода данных из ПФУ в ОП, при которой адрес данных увеличивается, а значение счетчика данных уменьшается в ходе операции на величину кода модификацииj

Обратное чтение - операция ввода данных из ПФУ в ОП, при которой адрес данных и значение счетчика данных в ходе операции уменьшаются на

код модификации.

При начальной загрузке информации

из КСК в канал 12 код операции передачи данных, вьтолняемой каналом, помещается в регистр 17 кода операции, начальный адрес данных - в регистр 16 адреса данных, начальное значение счетчика данных - в счетчик 14 байтов

Одновременно с занесением адреса данных в регистр 16 адреса данных младшие разряды адреса данных, указывающие номер байта в слове, заносятся в счетчик номера байта (не показан) . Количество таких разрядов определяется длиной слова ОП и при восьмибайт- ном слове ОП этих разрядов - три.

Затем начинается передача данных. В операции Чтение данные из ПФУ последовательно байта за байтом принимаются в канал и непосредственно с

последнего байта регистра 13 либо приема последнего байта массива блок 15 выдачи запросов вьфабатывает запрос на обращение к ОП. Сигнал запроса поступает со входа 20 устройства 5 в блок 3 приоритета запросов. Клок 3 формирует сигнал запроса на обмен, поступающий на выход 24 устройства. По этому сигналу ОП подготавливается к обмену данными, а в случае встроен- 0 ньгх каналов по нему к обмену данными готовится и процессор. Блоком 3 также вырабатывается адрес наиболее приоритетного канала, затребовавшего передачу данных. Этот адрес поступает на t5 управляющие входы коммутаторов - 1, 2, 5 и 6. На выходы коммутаторов передается информация от выбранного канала. Через коммутатор 1 данных на выход 23 устройства в ОП вьщается . 20 слово данных из регистра 13. Через коммутатор 5 адреса на выход 25 устройства в ОП выдается из регистра 16 адреса адрес слова, по которому должсвязи 68-70 выдаются младшие разряды

счетчика данных (по связи 68 выдается самый младший разряд счета). На связь 71 вьщается О в том случае, если все остальные старшие разряды счета данных нулевые и выдается 1 если в разрядах счета данных, исключая три младших бита, имеется хотя бы один бит, установленный в 1. Единичный сигнал на связи 71 означает, что значение счета данных в канале не меньше, чем 8 (комбинация 1000).

Данные, записываемые в ОП, сопровождаются маской, задающей те байты в слове данных, которые должны замещать соответствующие байты слова, прочитанного из ОП.

Разрядность маски определяется количеством байтов в слове и для рассматриваемого примера реализации устройства равна восьми. Каждый разряд маски соответствует одному байту слова: разряд О - байту О, разряд 1 - байту 1 и т.д. Если разряд маски соны быть записаны данные. Три младших 25 держит единицу, соответствующий байт

разряда адреса данных подаются на вход блока 7 сумматоров по модулю два посредством связей 90-92.

Через одноразрядный коммутатор 6 кода операции на управляющие входы блока 7 и коммутатора 8 перекомпоновки подается потенциал, формируемый по содержимому регистра 17 кода операции.

При этом О означает, что выполняется операция Чтение или операция Запись, 1 - операция Обратное чтение. Для операции Чтение, поступая в блоке 7 на входы сумматоров 40 56 по модулю два, нулевой уровень задает передачу младших разрядов адреса данных на вход блока 4 формирования маски и вход блока 9 формирования кода модификации (связи 93-95) без плексора 41 на связь 82 вьщается млад- вертирования. Поступая в блоке 8 на ший разряд маски (разряд 7). С мульти- управляющий вход коммутатора 55 нуле- плексора 48 на связь 89 выдается стар- вой уровень задает передачу маски, сформированной блоком 4, на выход масМаска записи в ОП вырабатывается блоком 4 формирования маски по значению младших разрядов адреса данных, полученному по связям 93-95 от блока 7, и значению разрядов счета данных, полученному по связям 68-71 от четырехразрядного коммутатора 2 номера байта. Маска образуется на выходах мультиплексоров 41-48 маски. С мультиший разряд маски (разряд 0).

Младшие разряды адреса данных поки 26 устройства без перекомпоновки (старший разряд маски, полученный от блока 4 связью 89, передается в качестве разряда О маски, младший разряд маски, полученный связью 82, пе50 средством связей 93-95 подаются на адресные входы мультиплексоров 41-48 (по связи 93 поступает младший из разрядов, по связи 95 - старший из разрядов). При этом разрешается перередается в качестве разряда 7 маски). дача информации со входов, выбирае- Через коммутатор 2 номера байта на мых подаваемой адресной комбинацией, входы блоков 4 и 9 по связям 68-71 на выходы мультиплексоров. Так, при . поступают четыре разряда, отображаю- комбинации 011, подаваемой на адрес- щие значение счетчика 14 байтов. Ня ные входы А4, А2, А1 мультиплексоров.

6

и 68-70 выдаются младшие разряды

счетчика данных (по связи 68 выдается самый младший разряд счета). На связь 71 вьщается О в том случае, если все остальные старшие разряды счета данных нулевые и выдается 1 если в разрядах счета данных, исключая три младших бита, имеется хотя бы один бит, установленный в 1. Единичный сигнал на связи 71 означает, что значение счета данных в канале не меньше, чем 8 (комбинация 1000).

Данные, записываемые в ОП, сопровождаются маской, задающей те байты в слове данных, которые должны замещать соответствующие байты слова, прочитанного из ОП.

Разрядность маски определяется количеством байтов в слове и для рассматриваемого примера реализации устройства равна восьми. Каждый разряд маски соответствует одному байту слова: разряд О - байту О, разряд 1 - байту 1 и т.д. Если разряд маски со0

5

0 з плексора 41 на связь 82 вьщается млад- ший разряд маски (разряд 7). С мульти- плексора 48 на связь 89 выдается стар- слова данных записывается в ОП, если нуль - не записывается и в ОП сохраня ется прежний байт. В частности, если маска содержит единицы во всех разрядах, в ОП пишется полное слово. Чаще всего запись в ОП производится полными словами, но если границы массива данных не совпадают с границами слов в ОП, первое и последнее слова массива не полные.

Маска записи в ОП вырабатывается блоком 4 формирования маски по значению младших разрядов адреса данных, полученному по связям 93-95 от блока 7, и значению разрядов счета данных, полученному по связям 68-71 от четырехразрядного коммутатора 2 номера байта. Маска образуется на выходах мультиплексоров 41-48 маски. С мультиплексора 41 на связь 82 вьщается млад ший разряд маски (разряд 7). С мульти плексора 48 на связь 89 выдается стар

ший разряд маски (разряд 0).

Младшие разряды адреса данных посредством связей 93-95 подаются на адресные входы мультиплексоров 41-48 (по связи 93 поступает младший из разрядов, по связи 95 - старший из разрядов). При этом разрешается перена выходы мультиплеесоров 41-48 будет передана информация со входов ДЗ. На выходах мультиплексоров соответствующих разрядам с номерами, меньшими, чем восьмиричное число К, определяе- мое комбинацией, подаваемой на адресные входы А4, А2, А1, формируются кули за счет того, что на выбранные входы этих мультиплексоров подается уровень логического О. На выходе мультиплексора разряда с номером К формируется 1, так как на выбранный вход этого мультиплексора подается уровень логической единицы - 1, Единица в этом разряде маски обусловле- на тем, что счет данных перед передачей данных не может быть нулевым. На выходах мультиплексоров, соответствующих разрядам с номерами, большими чем К, формируются значения, обусловленные счетом данных.

Мпадшие разряды счета данных (восьмиричное число М) дешифруются в блоке 4 формирования маски дешифратором 40. Сигналы с выходов дешифрато- ра 40, соответствующие счету данных от 2 до 7, поступают на элементы ИЛИ 49-54. На эти же элементы подается сигнал со связи 71, соответствующий счету данных большему, чем 7. Уро вень единицы появляется на выходах: элемента ИЛИ 54 - при счете данных больше 1, элемента ИЛИ 53 - при счете больше 2, элемента ИЛИ 52 -при счете больше 3, элемента ИЛИ 51 - при счете больше 4, элемента ИЛИ 50 - при счете больше 5, элемента ИЛИ 49 - при счете больше 6. При счете данных большем, чем 7, уровни единицы появляются на выходах всех шести элемен- тов ИЛИ 49-54, а также на входе ДО мультиплексора 41 .благодаря наличию сигнала на связи 71. На выбранные входы мультиплексоров, соответствующих разрядам с номерами большими чем К, подаются в порядке возрастания номеров разрядов сигналы с выходов элементов ШШ 54, 53 и т.д. соответственно.

В случае, если М меньше, чем количество разрядов с номерами большим,, чем К, то на выходах М разрядов маски, начиная с разряда с номером К, появляются единицы. Когда М больше или равно количеству разрядов с номерами большими К, единицы появляются на выходах мультиплексоров всех этих разрядов маски. Маска, полученная в

блоке 4, передается на выход устройства 26 без перекомпоновки разрядов. Одновременно с получением маски блоком 9 формирования кода модификации по значению младших разрядов адреса данных, полученному от блока 7, и значению разрядов счета данных, полученному от коммутатора 2, вырабатывается код модификации. Код модификации выдается из блока 9 на выход 27 устройства и используется для модификации адреса данных и счета байтов. Эта модификация для встроенных каналов обычно выполняется в процессоре, для автономных каналов может выполняться в каналах.

В блоке 9 младшие разряды адреса данных со связей 93-95 подаются на информационные входы дешифратора 29, младшие разряды счета со связей 68- 70 подаются на информационные входы дешифратора 30. Управление дешифратором 30 производит разряд счета, поступающий по связи 71. При счете больше или равном 8 сигнал со связи 71 блокирует дешифратор 30 и код модификации формируется по мпадшим разрядам адреса данных (по сигналу с выхода дешифратора 29). При комбинации 111 на связях 94, 95 и 93 возбуждается выход Д7 дешифратора 29 единичньш уровень подается через элемент ИЛИ 32 на вход Д1 шифратора 31. На связях 75, 74, 73, 72 формируется код модификации 0001. Подобным образом при подаче по связям 95, 94, 93 комбинаци 110 на выходах элемента И 39 и шифратора 31 (связи 75, 74, 73 и 72) формируется код 0010, при комбинации 101 - код 0011, при комбинации 100 - код 0100, при комбинации 011 - код 0101, при комбинации 010 - код 0110, при комбинации 001 возбуждается выход ДО дешифратора 29 и формируется код модификации 1000.

При счете, меньшем чем 8 (сигнал на связи 71 нулевой) адресе данных, находящемся на границе слова (комбинация 000 на связях 95, 94 и 93) код модификации формируется по разрядам счета данных (по сигналу с возбужденного выхода дешифратора 30 счета). Кобинация 001 на связях 70, 69 и 68 вызывает возбуждение выхода Д1 дешифратора 30 и подачу единичного сигнала через элемент ИЛИ 32 на вход Д1 шифратора 31. На связях 75, 74, 73 и 72 формируется код модификации 0001. Полобным образом при подаче на снячи Л, 79, 69, 68 комбинации 0010 на выходах элемента И 39 и шифратора 31 (связи 7.5, 74, 73, 72) формируется код 0010, при комбинации 0011 - код ООП, при комбинации 0100 - код 0100, при кбмбинации 0101 - код 0101, при комбинации 0110 - код 0100, при комбинации 0101 - код 0101, при комбинации 01.10 - код 0110, при комбинации 0111 возбуждается выход Д7 дешифратора 30 и формируется код модификации 0111.

При счете, меньшем чем 8, и адре

се данных не на границе слова на элементы ИЛИ 32-38 подан единичный сигнал с одного из выходов дешифратора 29 адреса и единичный сигнал с одного из выходов дешифратора 30 счета Эти единичные сигналы соответствуют получению кода модификации соответ- стпенно по адресу данных или счету данных. Единичные сигналы при этом могут быть поданы на два входа шифратора 31. Так как шифратор 31 формирует код для более приоритетного входа, то на связях 72-74 появляется меньший из возможных двух кодов (кода, получаемого по адресу данных, и кода, получаемого по счету данных). Код модификации со связей 72-75 выдается на выход 27 устройства.

Маска записи, сформированная в устройстве, подается в блок 10 преобразования маски по связям 96-103. По связи 103 подается старший разряд маски (разряд 0), по связи 96 - младший разряд маски (разряд 7). Блок 10 формирует по полученной маске код модификации, подаваемый по связям 104- 107 в блок 11 сравнения. При несовпадении этого кода модификации с кодом, полученным в блоке 9, блок 11 сравнения выдает на выход 28 устройства сигнал ошибки. По наличию этого сигнала в процессоре либо в канале, вьшолняющем передачу данных, может быть зафиксирована ошибка формирования маски или кода модификации.

Преобразование маски в блоке 10 оновано на том, что последовательност единиц маски не может прерываться нулями при нормально сформированной маске. Блок 10 работает следующим образом.

Значение младшего разряда кода модификации, характеризующего четность количества единиц маски, получается суммированием по модулю два значения

5

0

5

0

5

0

Q

всех разрялов маски сумматорами 66. Полученный бит выдается в качестве разряда (3) кода модификации на связь 104.

Разряды маски в блоке 10 подаются также на входы шифратора 57 приоритета. На наиболее приоритетный вход шифратора подается старший разряд маски, на вход наименьшего приоритета - младший разряд маски. а выходах приоритетного шифратора образуется код номера старшего разряда маски, содержащего единицу.

Разряд (2) кода модификации, выдаваемый на связь 105, образуется на выходе мультиплексора 58. Значение этого разряда характеризует четность количества заполненных единицами пар разрядов маски и получается суммированием по модулю два четных либо нечетных разрядов маски. Суммирование значений четных разрядов маски вьтол- няется сумматорами 60, 62 и 64 по модулю два, суммирование значений нечетных разрядов маски - сумматорами 61, 63 и 65. Выбор того, какая из сумм используется в качестве разряда (2) кода модификации производится мультиплексором 58 по значению младшего разряда кода, вьфаботанного шифратором 57. Если номер старшего из разрядов маски, содержащих единицы четный, то на выход мультиплексора 58 вьдается сумма значений нечетных разрядов маски, если нечетный - сумма значений четных разрядов.

Разряд (1) кода модификации, вьща- ваемый на связь 106, образуется на выходе мультиплексора 59. Значение этого разряда характеризует четность количества заполненных единицами групп из четырех разрядов маски. Эту четность определяет сумма по модулю два значений одной из четьфех пар раз- 5 рядов маски. В пары разряды маски

группируются следующим образом: разряды (0) и (4); разряды (1) и (5)-, разряды (2) и (6)i разряды (3) и (7).

0

Суммирование значений разрядов пары производится соответственно сумматорами 60-63 по модулю два. Выбор того, какая из сумм используется в качестве разряда (1) кода модификации производится мультиплексором 59 по значению двух младших разрядов кода выработанного шифратором 57. Если номер старшего из разрядов маски, содержащих единицы 000J или 100, то на

выход мультиплексора 59 выдается сумма разрядов (3) и (7), если номер 001 иди 101 - сумма разрядов (0) и (4), если номер 010 или 110 - сумма разрядов (1) и (5), если номер 011 или 111 - сумма разрядов (2) и (6).

Старший разряд (0) кода модификации, значение которого выдается на связь 107, вырабатывается элементом И 67. Если значения старшего и млад- шего разрядов маски (со связей 103 и 96 соответственно) равны 1, то маска содержит восемь единиц и значение старшего разряда кода модификации -

При отсутствии ошибки формировани маски и кода модификации после записи слова данных в ОП адрес данных увеличивается на величину кода модификации, а промодифицированное значение адреса данных помещается в ре- гистр 16 адреса данных. На величину кода модификации также уменьшается значение счета данных, по которому формируется новое значение счетчика 14 байтов. В регистре 13 данных, на- чиная с нулевого байта, формируется очередное слово. Обращение к памяти и связанные с ним действия повторяются после накопления в регистре 13 данных каждого очередного слова.Фор- мирование маски и кода модификации контролируется при каждом обращении к памяти. Если массив оканчивается не на границе слова, последнее слово неполное и соответствующая этому слову маска содержит нули в одном или нескольких младших разрядах.

В операции Запись, когда необходимо прочитать из ОП слово данных, блок 15 выдачи запросов вырабатывает сигнал запроса на обращение к ОП, поступающий со входа 20 устройства в блок 3 приоритета запросов. Блоки устройства при операции Запись работают точно также, как и при опера- ции Чтение. Код модификации, формируемый устройством на выходе 27, как и для Чтения служит для модификации адреса и счета данных. Маска, выдаваемая на выход 26, при чтении из ОП не используется, а служит для целей контроля кода модификации.

Данные, принятые в канал 12 из ОП, последовательно байт за байтом выдаются в ПФУ непосредственно из регистра 13 данных либо через буфер данных в канале. Выдача данных в ПФУ может осуществляться под управлением

O

5 0 5 O

Q

5

5

счетчика номера байта (не показан), указывающего номер того байта в слове, которьп нужно вьшать. После каждой выдачи байта в ПФУ содержимое счетчика номера байт увеличивается на единицу, подготавливая вьщачу следующего байта.

Когда регистр 13 данных свободен, а значение счетчика 14 байтов ненулевое, блоком 15 выдачи запросов вьфа- батывается следующий запрос на обращение к ОП.

В случае операции Обратное чтение отличие работы устройства.от его работы при операции Чтение заключается в инвертировании младших разрядов адреса данных до их подачи в блоки 4 и 9 и перекомпоновки разрядов маски, сформированной блоком 4, на коммутаторе 8 перекомпоновки. Эти действия позволяют для операции Обратное чтение, требующей уменьшения адреса данных, формировать маску в блоке 4 и код модификации в блоке 9, точно таким же образом, как и для one рации Чтение.

При этом в блоке 7 уровень единицы, поступающий от коммутатора 6 кода операции на входы сумматоров 56 по модулю два, задает инвертирование младших разрядов адреса (со связей 90-92). Проинвертированный адрес из блока 7 по связям 93-95 поступает в блок 4 формирования маски и блок 9 формирования кода модификации.

Биты маски, полученной в блоке 4 по принципу, изложенному для операции Чтение, подаются на вход коммутатора 8 перекомпоновки. Уровень единицы, поступающий на управляющий вход коммутатора 55, задает перекомпоновку разрядов маски до ее вьщачи на выход маски 26 устройства. Младший разряд маски от блока 4 со связи 82 передается через коммутатор 55 в качестве старшего разряда (0) маски. Разряды маски со связей 83-88 передаются через коммутатор 55 в качестве разрядов (1)-(6) маски соответственно Старший разряд маски от блока 4 со связи 89 передается через коммутатор 55 в качестве младшего разряда (7) маски.

Одновременно с маской по проиняер- тированным младшим разрядам адреса в блоке 9 формирования кода модификации получается код модификации, выдаваемый на выход 27 устройства. Код модификации при этом получается по тому же принципу, что и для операции Чтение. Контроль маски и кода модификации выполняется точно также как и для операции Чтение.5

Пример . Операция Чтение. Младшие разряды адреса данных равны OlOj (соответственно для связей 92, 91, 90), значение счета данных 3, (00011 ) передается по линиям 71, 70,fO

69,68 как 0011. В СП пишется только одно слово данных.

Младшие разряды адреса данных проходят через блок 7 без инвертирования и подаются в блок 4 формирования мае-15 ки и блок 9 формирования кода модификации. На связях 95, 94 и 93 комбинация 010. Этой комбинацией, поданной на адресные входы А4, А2, А1 мультиплексоров 41-48, разрешается переда- 20 ча через мультиплексоры информации со входов Д2. По коду 0011 со связей 71,

70,69 и 68 возбуждается выход ДЗ дешифратора 40 (связь 80) и появляется

1 на выходах элементов ИЛИ 53, 54. 25 Через мультиплексоры 48 и 47 передается логический О, через мультиплексор 46 - логическая 1, через мультиплексоры 45, 44 - уровни 1 соответственно от элементов ИЛИ 54 и 53 ,через мульти-30 плексоры 43, 42 и 41 - уровни О от элементов ИЛИ 52, 51 и 50 соответственно. На связях 89-82 выхода блока 4 оказывается сформированной маска 00111000 (разряды (0) - (7)), переда-35 ваемая без перекомпоновки на выход 26 устройства и в блок 10 преобразования маски.

В блоке 10 преобразованиямаски по

маске 00111000 (связи 103-96 соответственно) , на выходах дешифратора 57 приоритета появляется код 010. На связи 104 (младший разряд кода модификации) сумматорами 60-66 по модулю два формируется 1. По нулю, поданном на адресный вход А1 мультиплексоров 58, разрешается передача через мультиплексор информации со входа ДО от сумматора 65 по модулю два. На выходе сумматора 65 образуется 1 - сумма по модулю два нечетных разрядов маски (биты со связей 102, 100, 98 и 96). Это значение выдается на связь 105 блока. По комбинации 10, поданной на адресные входы А2, А1 соответственно мультиплексора 59, разрешается передача через мультиплексор информации со входа Д2 от сумматора 61

O

5 0

5 05

0

e g е

по модулю два. На выходе сумматора 61 образуется О - сумма по модулю два разрядов маски со связей 102 и 98. . Это значение появляется на связи 106 блока. На связи 107 блока появляется О с выхода элемента И 67. Код модификации, сформированный блоком 10 на связях 107, 106, 105, 104 и выдаваемый в блок 11 сравнения, равен 0011.J.

В блоке 9 формирования кода модификации по комбинации 010 со связей 95, 94 и 93 возбуждается выход Д2 дешифратора 29 и появляется 1 на выходе элемента ИЛИ 37. По коду 0011 со связей 71, 70, 69 и 68 возбуждается выход ДЗ дешифратора 30 и появляется 1 на выходе элемента ИЛИ 34. Шифратор 31 с учетом того, что его вход ДЗ имеет приоритет более высокий, чем вход Д6 формирует на связях 74, 73 и 72 код 011. С учетом уровня О со связи 75 полученный на связях 75- 72 код модификации - 001Ij . Этот код выдается на выход 27 устройства и в блок 11 сравнения.

В блоке 11 сравнения поразрядно сравниваются коды модификации, полученные от блоков 9 и 10. Так как они равны, то сигнал ошибки на выходе 28 устройства отсутствует.

Формула изобретения

1.Устройство для сопряжения каналов ввода-вывода с оперативной памятью по авт. св. № 129961, отличающееся тем, что, с целью повьш1ения достоверности передачи информации, в него введены блок преобразования кода маски в код модификации и блок сравнения, причем выход . блока сравнения является выходом ошибки устройства, при этом первый и второй информационные входы блока сравнения соединены соответственно с выходом блока формирования кода модификации и информационным выходом блока преобразования кода маски в код модификации, информационный вход которого соединен с выходом коммутатора перекомпоновки маски.

2.Устройство по п. 1, отличающееся тем, что блок преобразования кода маски в код модификации содержит шифратор приоритета, два мультиплексора, семь сумматоров , по модулю два и элемент И, причем первый, второй, третий, четвертый.

пятый, шес .той, соцьмой и носьмпй нн- формациониь1е входы шифратора приоритета образуют информационный вход блока преобразования маски, выход элемента И, информационные выходы перво- го и второго мультиплексоров, выход первого сумматора по модулю два образуют информационньш выход блока преобразования маски, при этом в блоке преобразования маски первые входы второго, третьего, четвертого и пятого сумматоров по модулю два соединены соответственно с первым, вто- pbw, третьим и четвертым информационными входами шифратора приоритета, пятый, шестой, седьмой и восьмой, информационные входы которого соединены со вторыми входами соответственно второго, третьего, четвертого и пятого сумматоров по модулю два, первый и второй входы элемента И соединены соответственно с первым и восьмым информационными входами шифратора приоритета, первый выход которого соединен с первым адресным входом пер вого мультиплексора и адресным вхоФиг. 2

дом второго мультиплексора, первый ннформащюнный вход которого соединен с выходом шестого сумматора по модулю два и первым входом первого сумматора по модулю два, второй вход которого соединен со вторым информационным входом второго мультиплексора и выходом седьмого сумматора по модулю два, первый вход которого соединен с выходом второго сумматора по модулю два и первым информационным входом первого мультиплексора, второй информационный вход которого соединен с выходом пятого сумматора по модулю два и первым входом шестого сумматора по модулю два, второй вход которого соединен с выходом третьего сумматора по модулю два и третьим информационным входом первого мультиплексора, четвертый информационный вход которого соединен с вторым входом седьмого сумматора по модулю два и выходом четвертого сумматора по модулю два, второй выход шифратора приоритета соединен с вторым адресным входом первого мультиплексора.

24

кЮ

Фиг. 4

к4.9

rv.

Cb

§

Ni

.00

Cb

al

( CSI NI 1 «Nl

JL

t vo

ex

r

U)

сэ f

n

SN

O)

Составитель С.Пестмал Редактор Г.Волкова Техред И.Попович Корректор

Заказ 2866/46 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

rr

c

Ur

tQ 5: vci

- I o 5; vo

«V

5

f 4:5

:: to

5N CS4

5: VQ

sl to

5: o

03

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения каналов ввода-вывода с оперативной памятью | 1985 |

|

SU1267427A1 |

| Устройство для предварительной обработки операндов переменной длины | 1984 |

|

SU1269147A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1985 |

|

SU1260970A2 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1837305A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1987 |

|

SU1587521A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1829038A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

Изобретение относится к вычислительной технике, в частности к устройствам, состоящим из некоторого числа каналов ввода-вывода и устрой26 ства управления, обслуживающего в режиме разделения времени эти каналы, причем каналы могут быть автономными либо встроенными.. Целью изобретения является повьппение достоверности передачи информации. Устройство содержит коммутатор 1 данных,коммутатор 2 номера байта, блок 3 приоритета запросов, блок 4 формирования маски, коммутатор 5 адреса, коммутатор 6 кода операции, блок 7 сумматоров по модулю два, коммутатор 8 перекомпоновки маски, блок 9 формирования кода модификации, блок 10 преобразования кода маски в код модификации, блок 11 сравнения. 1 з.п. ф-лы, 6 ил. 28 27 а (Л 10 Го Фиг.1

| Устройство для доводки (полирования, заточки) плоских поверхностей изделий, в частности режущих граней резцов, применяемых при строжке пленок фторопласта | 1959 |

|

SU129961A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-07—Публикация

1986-02-18—Подача