1

Изобретение отиоситея к области вычислительной техники и, в частности, к организации диагностического контроля мнкропрограл много процессора.

Известен микроирограммиый ироцессор, включающий арифметико-логический блок, связанный с заиоминаюнднм блоком, блок контроля, выходы которого соединены с первыми входами блока синхронизации и блока дешифрации микрокоманд, блок управления диагиостикой, иервый выход которого соединен со вторым входом блока синхронизации, узел контроля четности, блок запоминания микрокомаид, связанный с первым входом регистра микрокоманд, с выходами дешифраторов горизонтальных и вертикальных шин, соответствующие входы которых соединены с выходами блока синхронизации, адресного регистра блока запоминания микрокоманд н выходами горизонтального и вертикального вентилей блокировки, причем вход блока управлеиия диагностикой соединен с одним выходом переключателя режимов, другой выход которого соединен с третьим входом блока синхронизации, первый выход блока и дешифрации микрокоманд соединен со входом арифметико-логического блока, соответствующий выход которого соединен с первым входом блока контроля, второй вход которого через узел контроля четности соединен с выходом

2

регистра микрокоманд и вторым входом блока дешифрации микрокоманд.

Недостаток известного микропрограммного процессора заключается в том, что автоматическая диагиостика аппаратуры требует больших затрат оборудования.

Цель изобретения - упрощение нроцессора.

Поставленная ноль достигается тем, что мнкропрограммный ироцессор содержит блок изменения длительности импульсов, трнггеры переключения выборки, ннверснн контроля и инверсии блокировки, причем входы триггера инверсии контроля соединены со входом и вторым выходом блока управления диагностикой, третий выход которого соединен с одним из входов триггера инверсии блокнровкн, выходы которого соедннеиы с первыми входами горизонтального н вертикального вентилей блокировки, вторые входы которых соединены с одним из выходов трнггера инверсии KOirrроля н с третьим входом блока контроля, четвертый выход блока управлепия диагносппчоА через блок изменения длительности илшульсов соединен с четвертым входом блока синхронизации, иятый вход которого соединен со вторым входом микрокоманд и через триггер переключения выборки - со вторым В1ЛХОДОМ блока дешифрации микрокоманд, а третий вход регистра микрокомаид соединен с выходом заноминающего блока.

3

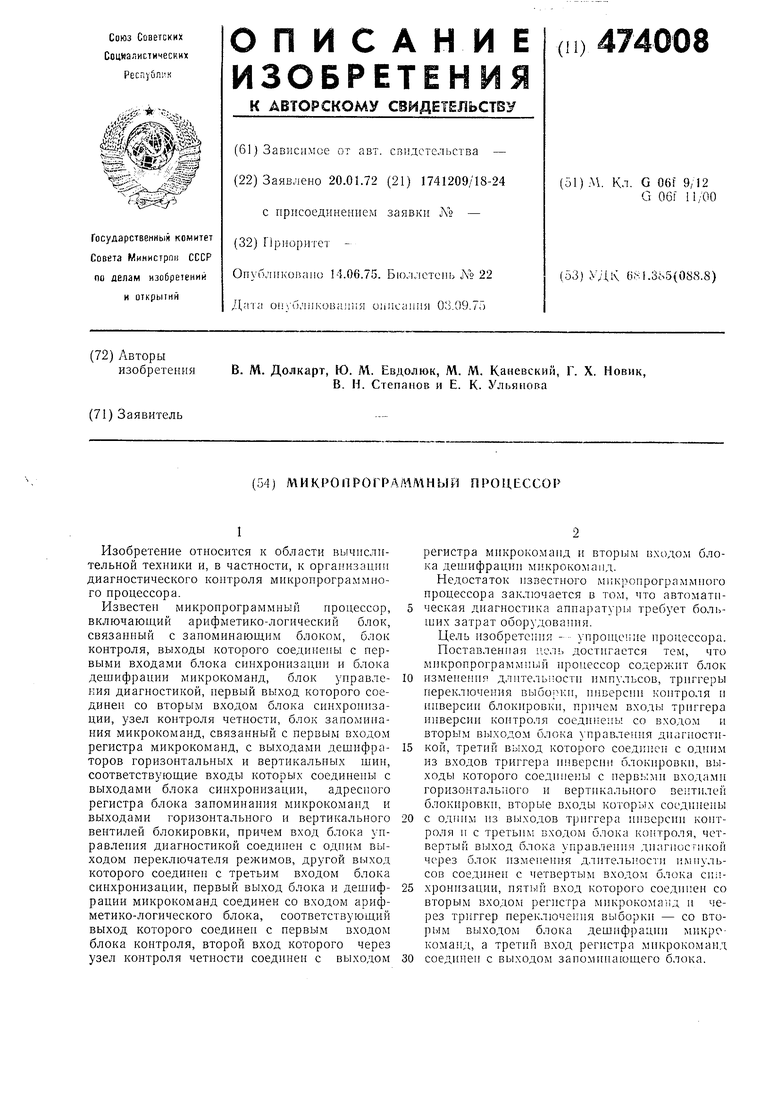

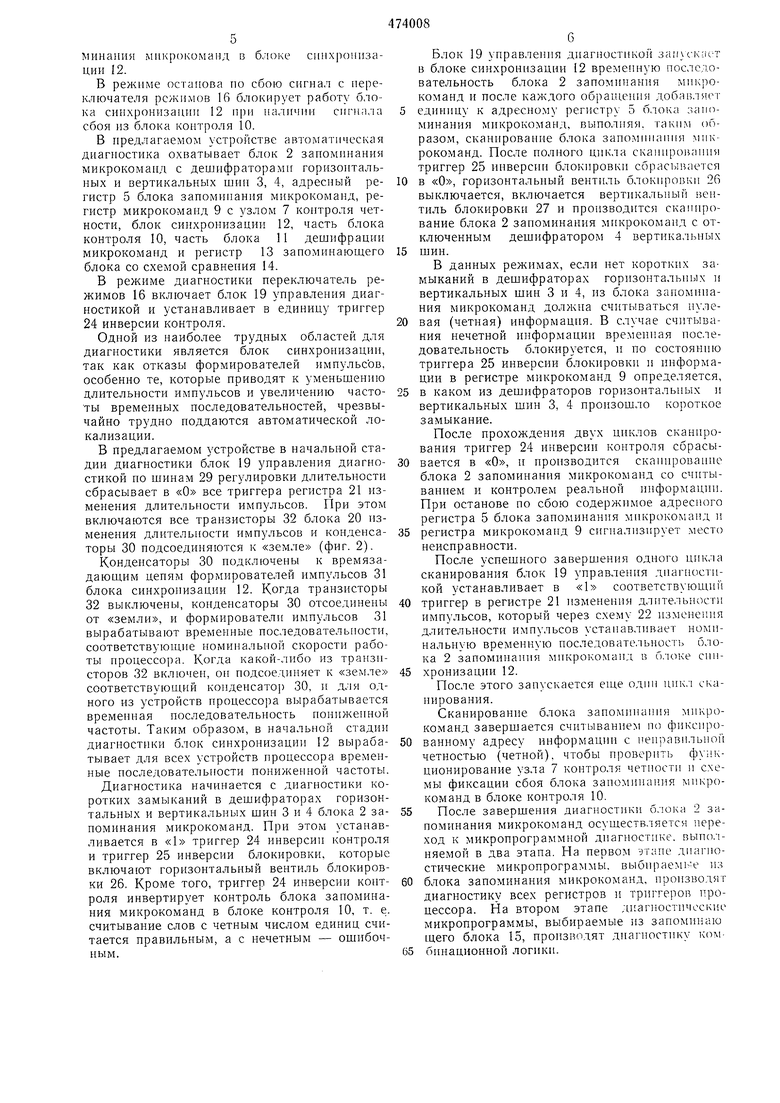

Блок-схема микропрограммного процессора представлена на фиг. 1; на фпг. 2 приведеjia схема блока нзменения длительности импульсов.

Микронрограммный процессор (фиг. 1) содержит арифметико-логический блок 1, блок 2 запоминания микрокоманд, дешифратор 3 горизоитальпых шин, дешифратор 4 вертикальных шин, адресный регистр 5 блока запоминания микрокоманд, узлы 6, 7, контроля четкости, адресный регистр 8 повтора микрокоманд, регистр микрокоманд 9, блок контроля 10, блок 11 дешифрации микрокоманд, блок синхронизации 12, регистр 13 заиоминающего блока, схему сравнения 14, запоминающий блок 15, переключатель режимов 16, реnicip ключей 17 останова по адресу, схему cpaiuieHiiii 18 регистра ключей, блок 19 управ.чепня диагностикой, блок 20 изменения длительности импульсов, регистр 21, схему 22 изменения длительности импульсов, блок 23 зацикливания микропрограмм, триггер 24 инверсии контроля, триггер 25 инверсии блокировки, горизонтальный вентиль блокировки 26, вертикальный вентиль блокировки 27, триггер 28 переключения выборки, шипы 29 регулпровки длительности.

На фи1-. 2 обозначены; 30-конденсаторы; 31 - формирователи; 32 - транзисторы.

Микропрограммный нроцессор работает следующим образом.

Все преобразования информации при работе процессора выполняются в арифметикологическом блоке (АЛБ) 1. В процессоре использован микропрограммный иринциц управления. Управляющие слова (микрокоманды) хранятся в блоке 2 запоминания микрокомапд, представляющем собой постоянную память с матричной выборкой. Разрядность управляющего слова совпадает с разрядностью команд и информационных слов процессора.

Выбор определенного управляющего слова производится с помощью дешифратора 3 горизонтальных щин и дешифратора 4 вертикальных шин, соединеииых с младшими и старшими разрядами адресного регистра 5 блока запоминания микрокоманд. Передачи информации в адресный регистр блока запоминания микрокоманд контролируются по четпости с помощью узла 6 контроля четности.

Выполнение текущей микрокоманды совмещеио с выборкой следующей микрокоманды из блока 2 запоминаиия микрокоманд.

Перед образованием адреса очередного управляющего слова в адресном регистре 5 блока запоминания микрокоманд его содержимое передается в адресный регистр 8 повтора микрокоманд. В случае обнаружения сбоя при выполнении микрокоманды содержимое адресного регистра повтора микрокоманд передается в адресный регистр блока запоминания микрокоманд, и повторяется выполнение микрокол1анды, в которой обнаружен сбой.

4

Микрокоманды выбираются н регистр микрокоманд 9 п контролируются но четности с помоп1,ью узла 7 контроля четности. При этом все управляющие слова имеют нечетное число единиц.

Выходы узлов 6 и 7 ко1ггроля четности, а также выход схемы контроля ЛЛБ 1 соединяются с блоком контроля 10, который осуществляет синхронизацию конгроля, фиксирует сбои и управляет режимами работы процессора при сбоях и отказах.

Группа млaдпJиx разрядов регпстра микрокоманд 9 перед выборкой следующей микрокоманды передается в младшие разряды адресного регистра 5 блока запомпнання микрокоманд.

При выполпе1П И микрокоманд блок 11 дешифрации микрокоманд декодирует состояние унравляюп1,пх нолей регист за микрокоманд 9 и вырабатывает уровпп управления для выиолиепия полпого набора микрокомаид процессора.

Блок синхронизации 12 вырабатывает синхронизирующие носледовательности для работы АЛ Б 1, блока 2 запоминания микрокоманд и запоминающего блока 15. Обмен информацией с запоминающим блоком 15 производится через регистр 13 запомп 1аюн1его блока, который может быть связан с любым регистром

АЛ Б 1.

Схема сравпения 14 производит сравнение информации в регистра 13 запоминающего блока и па выходной шине АЛБ 1. Выход схемы сравнения 14 соединен с младшим разрядом адресного регистра 5 блока заноминапия

микрокоманд и исиользуется для ветвления

микронрограмм при работе процессора и в

процедурах диагностики.

Режимы работы процессора задаются с переключателя режимов 16. Имеются следую1цие режимы работы:

1)рабочий;

2)с остановом но адресу микрокоманды;

3)с остановом по сбою; 4) диагностики;

5) зацикливания микропрограмм.

Б рабочем режиме процессор автоматически выполняет текущпе команды программы. При обпаружении отказа производятся переход в ловушку и п|эрграммпая обработка ипформации об отказе.

Режим с остановом по адресу микрокоманды используется при отладке и для облегчения ручной диагностики. Для реализации этого режима на пульте управления имеется регистр ключей 17 останова по адресу, с помощью которого набирается адрес блока 2 запоминания микрокоманд, после выборки из которого микрокоманды необходим останов. После того, как адрес в адресном регистре 5 блока запомипания микрокоманд совпадает с содержимым регистра ключей 17 останова по адресу, схема сравнения 18 возбудит блокирующий сигнал, который остановит синхроннзирующую последовательность блока запоМинания микрокоманд в блоке синхронизации 12.

В режиме останова по сбою сигнал с иереключателя режимов 16 блокирует работу блока синхронизаиии 12 при наличии сигнала сбоя из блока контроля 10.

В предлагаемом устройстве автоматнческая диагностика охватывает блок 2 заиоминания микрокоманд с дешифраторами горизоитальиых и вертикальных шин 3, 4, адресиый регистр 5 блока заиомипания микрокоманд, регистр микрокоманд 9 с узлом 7 контроля четности, блок синхронизации 12, часть блока контроля 10, часть блока 11 дешифрации микрокоманд и регистр 13 запоминающего блока со схемой сравнепия 14.

В режиме диагностики переключатель режимов 16 включает блок 19 управления диагностикой и устанавливает в единицу триггер 24 инверсии контроля.

Одной из наиболее трудных областей для диагностики является блок синхронизации, так как отказы формирователей импульсов, особенно те, которые приводят к уменьшению длительности импульсов и увеличению частоты временных последовательностей, чрезвычайно трудно поддаются автоматической локализации.

В предлагаемом устройстве в начальной стадии диагностики блок 19 управления диагностикой по шинам 29 регулировки длительности сбрасывает в «О все триггера регистра 21 изменения длительности импульсов. При этом включаются все транзисторы 32 блока 20 изменения длительности импульсов и коиденсаторы 30 подсоедиияются к «земле (фиг. 2).

Конденсаторы 30 иодключены к времязадающим цеиям формирователей импульсов 31 блока синхронизации 12. Когда транзисторы 32 выключены, конденсаторы 30 отсоединены от «земли, и формирователи импульсов 31 вырабатывают временные последовательности, соответствующие номинальной скорости работы процессора. Когда какой-либо из транзисторов 32 включен, он подсоединяет к «земле соответствующий конденсатор 30, и для одного из устройств процессора вырабатывается временная последовательность ионнженной частоты. Таким образом, в начальной стадии диагностики блок синхронизации 12 вырабатывает для всех устройств процессора временные носледовательности пониженной частоты.

Диагностика начинается с диагностики коротких замыканий в дешифраторах горизонтальных и вертикальных шин 3 и 4 блока 2 запоминания микрокоманд. При этом устанавливается в «1 триггер 24 инверсии контроля и триггер 25 инверсии блокировки, которые включают горизоитальный веитиль блокировки 26. Кроме того, триггер 24 инверсии контроля инвертирует контроль блока запоминания микрокоманд в блоке контроля 10, т. е. считывание слов с четным числом единиц считается правильным, а с нечетным - ошибочным.

Блок 19 управлення днагностикой запускает в блоке синхронизации 12 временную последовательность блока 2 запоминания микрокоманд и после каждого обращения добавляет един1щу к адресному регистру 5 блока заиоминания микрокоманд, выполняя, таким образОдМ, сканироваиие блока запол1ннання мнк рокомаид. После полного цикла ска11иро);а11ия триггер 25 инверсии блокировки сбрасывается

в «О, горизонтальный вентиль блокировки 26 выключается, включается вертикальный вентиль блокировки 27 и производится сканирование блока 2 заиоминания микрокоманд с отключенным дешифратором 4 вертикальных

шин.

В данных , если нет коротких замыканий в дешифраторах горизонтальиых и вертикальных шип 3 и 4, из блока запомииания микрокоманд должна считЕ ваться нулевая (четная) информация. В случае считывания нечетной информации временная последовательность блокируется, и по состоянню триггера 25 инверсии блокировки и информации в регистре микрокоманд 9 определяется,

в каком из дешифраторов горизонтальных и вертикальных шин 3, 4 произошло короткое замыкание.

После прохождения двух циклов сканирования триггер 24 инверсии контроля сбрасывается в «О, и ироизводится скаиироваиие блока 2 запомииания микрокоманд со считыванием и контролем реальной 1нформации. При останове по сбою содержимое адресного регистра 5 блока заиоминания микрокоманд и

регистра микрокоманд 9 сигнализирует место неисправности.

После успешного завершения одного цикла сканирования блок 19 управления диагностикой устанавливает в «1 соответствующий

триггер в регистре 21 изменения дл п-ельности импульсов, который через схему 22 изменения длительности импульсов устанавливает номинальиую временную носледовательность блока 2 запоминания микрокоманд в б/юке сипхронизации 12.

После этого запускается еще один цнкл сканирования.

Сканированне блока заноминания микрокоманд завершается считыванием но фиксированному адресу информации с ненравильной четностью (четной), чтобы проверить функционирование узла 7 контроля четности и схемы фиксации сбоя блока заноминания микрокоманд в блоке контроля 10.

После завершения диагностики блока 2 запоминания микрокоманд осуществляется переход к микропрограммной диагностике, выполняемой в два этапа. На первом этане диагностические микропрограммы. выбираемь;е из

блока запоминания микрокоманд, производят диагностику всех регистров и триггеров процессора. На втором этапе диагностичоские микропрограммы, выбираемые из запоминаю щего блока 15, производят диагностику комбинационной логики.

Первый этап микропрограммной диагностики производится методом «раскрутки, начиная с регистра 13 запоминающего блока и постепенно захватывая регистры и триггеры АЛБ 1.

Диагностика проводится обычными методами с использованием для локализации неисправностей диагностических словарей остановов.

Первый этап микропрограммной диагностики нроводится сначала с временной последовательностью АЛБ 1 пониженной частоты. При успеплиом завершении этого иодэтаия блок 19 управления диагностикой через соответствуюашй разряд регистра 21 изменения длительности импульсов и схему 22 изменения длительности импульсов устапавливает номинальную временную последовательность АЛБ 1, и цикл микроирограммной диагностики первого этапа повторяется.

Первый этап микропрограммной диагностики завершается проверкой аппаратуры считывания запоминающего блока 15 в региетр 13 запоминающего блока в режиме номинальной временной последовательности запоминающего блока и установкой триггера 28 переключения выборки в единичное состояние. При этом в блоке синхронизации 12 блокируется временная последовательность блока 2 запоминания микрокоманд и перед выборкой каждой микрокоманды з пускается времен 1ая носледовательности запоминающего блока 15. Адрес выборки определяется адресным регнстролт 5 блока запоминания микрокоманд ir в регистре микрокоманд 9 включаются нени приема информации из заноминающего блока 15.

Таким образом, второй этан микронрограммной диагностики производится под управлением запоминающего блока 15, что существенно сокран1,ает объем блока 2 запоминания микрокоманд, необходимый для днйгпостики. Кроме того, данный режим работы используется при отладке микропрограмм, что позволяет оперативно вносить изменения.

В случае, если автоматическая диагностик не может точно локализовать место неисправности, в предлагаемом устройстве используется режим заликливаиия микропрограмм, существенно облегчающий режим ручной диагностики.

Данный режим позволяет зацикливать любые микропрограммы, а также фрагменты из них. Режим зацикливания микропрограмм, н основном, иснользует аппаратуру пстанот я адресу и повтора микрокоманд.

Начальный адрес цикла набирается в адресном регистре 8 повтора микрокоманд, а конечный адрес цикла набирается в регистре ключей 17 останова по адресу.

При пуске процессора в работу блока 23 зацикливания микроирограмм передает содержимое адресного регистра 8 повтора микрокоманд в адресный регистр 5 блока запоминания микрокоманд и блокирует обратную нередачу. Когда содержимое адресного регистра

олока заноминания микрокоманд будет равно конечному адресу цикла, набранному н ре1истре ключей 17 останова но адресу, схема сравнения 18 передает сигнал в блок 23 зацикливания микропрограмм, который вновь осуществляет передачу содержимого адресного регистра 8 новтора микрокоманд в ад|1есный регистр 5 блока заномина1П я микрокоманд и т. д,

Предмет li з о б р е т е н и я

Микропрограммный процессор, содержащий арифметико-логический блок, связанный с заноминающим блоком, блок контроля, выходы которого соединены с первыми входами блока синхроннзации и блока дешифрации микрокоманд, блок унравле 1ня диагностикой, первый выход которого соединен со вторым входом блока синхронизанни, узел контроля четности, блок заноминания микрокоманд, связанный с нерБым входом регистра микрокоманд, с выходами денщфраторов горизонтальных и вертикальных шии, соответствуюuiiie входы которых соединены с выходами блока сиихронизании, адресного регистра блока заномина1И1я микрокоманд, и выходами горизонтального и вертикального вентилей блокировки, нричем вход блока унравления диагностикой соедииен с одним выходом переключателя режимов, другой выход которого соедннен с третьим входом блока синхронизации,

непвый выход блока дещнфрации микрокоманд соедииен со входом арифметико-логического блока, соответствую}ций выход которого соединен с первым входом блока контроля, второй вход которого через узел контроля четности соединен с выходом регистра микрокоманд и вторым входом блока дещифрании микрокоманд, отличающийся тем, что, с целью уирощения процессора, он содержит блок изменения длительности имнульсов, трнггерг г переключения выборки, инверсии контроля и инверсии блокировки, нричем входы триггера инверсии контроля соединены со входом и со вторым выходом блока управления диагностикой, третий выход которого

соедииен с одним из входов триггера инверсии блокировки, выходы которого соединены с нервымн входами горизоитального и вертикального вентилей блокировки, вторые входы которых сордипоп - С ОДНИМ ИЗ ВЫХОДОВ триггеда инверсии контроля и с третьим входом, блока контроля, четвертый выход блока управления диагностикой через блок изменения длительности импульсов соединен с четвертым входом блока синхронизации, пятый вход которого соединен со вторым входом регистра микрокоманд и через триггер переключения выборки -- со вторым выходом блока дещифрации микрокоманд, а третий вход регистра микрокоманд соединен с выходом запоминающего блока.

Pu2.f

Г

125 125 1

29 1 29 1 Z3

Фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор | 1984 |

|

SU1246108A1 |

| Микропрограммный процессор | 1973 |

|

SU490122A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Процессор программируемого контроллера | 1985 |

|

SU1406595A1 |

| Процессор для выполнения математических операций | 1986 |

|

SU1381533A1 |

| Микропрограммный процессор | 1974 |

|

SU512471A1 |

| Микропрограммный процессор | 1974 |

|

SU535567A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Устройство для сопряжения ЦВМ с накопителями на магнитной ленте | 1985 |

|

SU1288708A1 |

| Процессор программируемого контроллера | 1988 |

|

SU1550515A2 |

Авторы

Даты

1975-06-15—Публикация

1972-01-20—Подача