1

Изобретение относится

к вычислительной технике и, в частности, к проектированию процессоров с контролем.

Известны микропрограммные процессоры, содержащие операционный блок, блок иамяти микрокоманд, регистр микрокоманд, регистр адреса микрокоманд, счетчик микрокоманд, схему сравнения, триггер фиксации сбоя, два элемента «И, элементы «ИЛИ и «НЕ.

Иервый выход операционного блока соединен шиной чтения микрокоманд с первым входом блока памяти микрокоманд, выход блока памяти микрокоманд - с входом регистра микрокоманд, первый выход которого подключен к первому входу операционного блока. Второй выход операционного блока соединен шиной начала операции с первым входом элемента «ИЛИ и с нервым входом первого элемента «И. Второй вход первого элемента «И связан с входом процессора, а выход этого элемента «И - с первым входом регистра адреса микрокоманд. Выход регистра адреса микрокоманд подключен к второму входу блока памяти микрокоманд. Третий выход операционного блока соединен шиной конца операции с вторым входом регистра адреса микрокоманд и с вторым входом элемента «ИЛИ, выход которого подключен к первому входу счетчика микрокоманд, первому входу схемы сравнения и через элемент «НЕ к первому

2

входу второго элемента «И. Второй вход второго эле.мента «И соединен с вторым выходо.м регистра микрокоманд, выход - с третьим входом регистра адреса микрокоманд, а выход схемы сравнения - с входом триггера фиксации сбоя, выход которого подключен к второму входу операционного блока. Однако в известных процессорах контроль микропрограммных последовательностей требует значительных затрат оборудования и дополнительного времени для выборки проверочных чисел из оперативной памяти.

Цель изобретения - упрощение процессора

и повышение его быстродействия.

Это достигается тем, что on дополнительно содержит триггер блокировки и третий элемент «И, причем четвертый выход операционного блока соединен шиной блокировки счета с входом установки триггера блокировки, вход гашения которого связан шиной конца операции с третьим выходом операционного блока, а выход триггера блокировки подключен к первому входу третьего элемента «И,

второй вход которого соединен шиной чтения микрокоманд с нервым выходом операционного блока. Выход третьего элемента «И подсоединен к второму входу счетчика микрокоманд. Выход счетчика связан с вторым входом схемы сравнения, третий вход схемы

сравнения - с вторым выходом регистра микрокоманд.

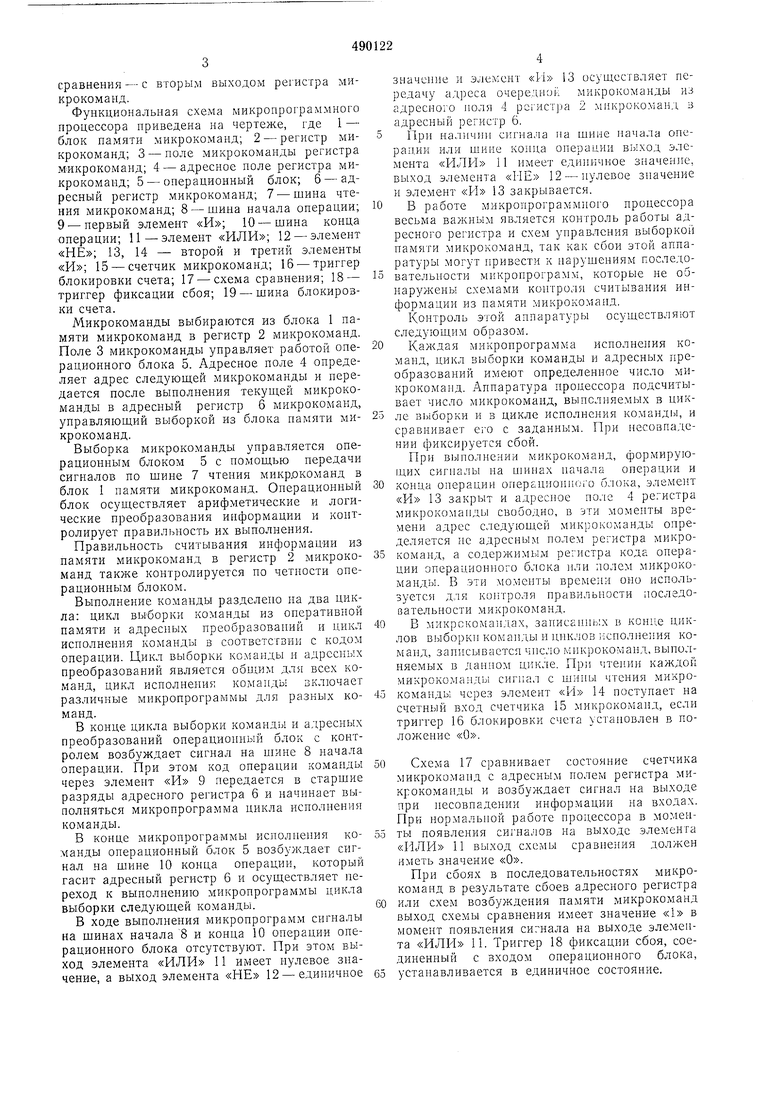

Функциональная схема микропрограммного процессора приведена на чертеже, где 1 - блок памяти микрокоманд; 2 - регистр микрокоманд; 3 - поле микрокоманды регистра микрокоманд; 4 - адресное ноле регистра микрокоманд; 5 - оиерационный блок; 6 - адресный регистр микрокоманд; 7 - шина чтения микрокоманд; 8 - шина начала операции; 9 - первый элемент 10 - шина конца операции; 11-элемент 12 - элемент 13, 14 - второй и третий элементы 15 - счетчик микрокоманд; 16 - триггер блокировки счета; 17 - схема сравнения; 18- триггер фиксации сбоя; 19 - шина блокировки счета.

Микрокоманды выбираются из блока 1 памяти микрокоманд в регистр 2 микрокоманд. Поле 3 микрокоманды управляет работой oneрационного блока 5. Адресное поле 4 определяет адрес следующей микрокоманды и передается после выполнения текущей микрокоманды в адресный регистр 6 микрокоманд, управляющий выборкой из блока памяти микрокоманд.

Выборка микрокоманды управляется операционным блоком 5 с помощью передачи сигналов по шине 7 чтения микрокоманд в блок 1 памяти микрокоманд. Операционный блок осуществляет арифметические и логические преобразования информации и контролирует правильность их выполнения.

Правильность считывания информации из памяти микрокоманд в регистр 2 микрокоманд также контролируется но четности операционным блоком.

Выполнение команды разделено на два цикла: цикл выборки команды из оперативной памяти и адресных преобразований и цикл исполнения команды в соответствии с кодом операции. Цикл выборки команды н адресных преобразований является общим для всех команд, цикл исполнения команды включает различные микропрограммы для разных команд.

В конце цикла выборки команды и адресных преобразований операционный блок с контролем возбуждает сигнал на шине В начала операции. При этом код операции команды через элемент «И 9 передается в старшие разряды адресного регистра 6 и начинает выполняться микропрограмма цикла исполнения команды.

В конце микропрограммы исполнения комаиды операционный блок 5 возбуждает сигнал на шине 10 конца операции, который гасит адресный регистр 6 и осуществляет переход к выполнению микропрограммы цикла выборки следующей команды.

В ходе выполнения микропрограмм сигналы на шинах начала 8 и конца 10 операции операционного блока отсутствуют. При этом выход элемента «ИЛИ 11 имеет нулевое значение, а выход элемента «НЕ 12 - единичное

значение и элемент «И 13 осуществляет передачу адреса очередной микрокоманды из адресного поля 4 регистра 2 микрокоманд з адресный регистр 6.

При наличии сигнала па шине начала операции или шине конца операции выход элеЛ1ента «ПЛРЬ И имеет единичное значение, выход элемента «ME 12 - пулевое зпачение и элемент «И 13 закрывается.

В работе микропрограммного процессора весьма важным является контроль работы адресного регистра и схем управления выборкой памяти микрокоманд, так как сбои этой аппаратуры могут привести к нарушениям последовательности микропрограмм, которые не обнаружены схемами контроля считывания информации из намяти микрокоманд.

Контроль этой аппаратуры осуществляют следующим образом.

Каждая микропрограмма исполнения команд, цикл выборки команды и адресных преобразований имеют определенное число микрокоманд. Аппаратура процессора подсчитывает число микрокоманд, выполняемых в цикле выборки и в цикле исполнения команды, и сравнивает его с заданным. При несовпадении фиксируется сбой.

При выполнении микрокоманд, формирую1ДИХ сигналы па шинах начала операции и конца операции опер циопиого блока, элемент «И 13 закрыт и адресное поле 4 регистра микрокоманды свободно, в эти моменты вреvieHH адрес следуюпяей микр окоманды определяется не адресным полем регистра микрокоманд, а содержимым регистра кода операции операционного блока пли полем микрокоманды. В эти моменты времени оно используется для ко11троля правильности последовательности микрокоманд.

В микрокомандах, записанг.ых в конце циклов выборки команды и циклов исполнения команд, записывается число )окоманд, выполняемых в данном . При чтеипп каждой микрокоманды сигнал с шипы чтения микрокоманды через элемент «И 14 поступает на счетный вход счетчика 15 микрокоманд, если триггер 16 блокировки счета установлен в положение «О.

Схема 17 сравнивает состояние счетчика микрокоманд с адресным полем регистра микрокоманды и возбуждает сигнал на вЕ ьходе при несовпадении информации на входах. При нормальной работе процессора в моменты появления сигналов на выходе элемента «ПЛИ 11 выход схемы сравнения должен иметь значение «О.

При сбоях в последовательностях микрокоманд в результате сбоев адресного регистра или схем возбуждения памяти микрокоманд выход схемы сравнения имеет значение «1 в момент появления сигнала на выходе элемента «ПЛИ 11. Триггер 18 фиксации сбоя, соединенный с входом операционного блока, устанавливается в единичное состояние.

В конце цикла выборки команды и цикла исполнения команды сигнал с выхода элемента «ИЛИ 11 передается на вход гашения счетчика 15 микрокоманд и с началом нового цикла снова проводится подсчет микрокоманд. При выполнении некоторых команд количество микрокоманд в микропрограмме не постоянно, а зависит от дополнительных условий выполнения команды. В этом случае в конце последовательности микрокоманд, которая постоянна для данной команды, подается микрокоманда, возбуждающая сигнал на шине блокировки счета операционного блока, который устанавливает в «1 триггер блокировки счета. При этом элемент «И 14 закрывается и добавление «1 к счетчику микрокоманд прекращается.

В этом случае в адресном поле последней микрокоманды данной команды записывается число микрокоманд, которое выполняется до момента исполнения микрокоманды блокировки счета, и, независимо от количества выполняемых микрокоманд в последующей переменной части выполняемой командь, содержимое счетчика микрокоманд должно быть равно содержимому адресного поля последней микрокоманды. В таком режиме работы также осуществляется контроль правильности последовательности микрокоманд, так как при сбое в адресном регистре или схемах возбуждения памяти микрокоманд начинает выполняться другая микропрограмма и содержимое счетчика микрокоманд не совпадает с содержимым адресного поля последней микрокоманды.

Предмет изобретения

Микропрограм.мный процессор, содержащий операционный блок, блок памяти микрокоманд, регистр микрокоманд, регистр адреса микрокоманд, счетчик микрокоманд, схему сравнения, триггер фиксации сбоя, два элемента «И, элементы «ИЛИ и «НЕ, причем первый выход операционного блока соединен

6

шиной чтения микрокоманд с первым входом блока памяти микрокоманд, выход которого соединен с входом регистра .микрокоманд, первый выход которого соединен с первым входом операционного блока, второй выход которого соединен шиной начала операции с первым входом элемента «ИЛИ и с первым входом первого элемента «И, второй вход которого соединен с входом процессора, а выход первого элемента «И соединен с первым входом регистра адреса микрокоманд, выход которого соединен с вторым входом блока памяти .микрокоманд, третий выход операционного блока соединен шиной конца операции с вторым входом регистра адреса микрокоманд и с вторым входом элемента «ИЛИ, выход которого соединен с первым входом счетчика микрокоманд, первым входом схемы сравнения и через элемент «НЕ с первым входом второго элемента «И, второй вход которого соединен с вторым выходом регистра микрокоманд, а выход - с третьи.м входом регистра адреса микрокоманд, выход схемы сравнения соединен с входом триггера фиксации сбоя, выход которого соединен с вторым входом операционного блока, отличающийся тем, что, с целью упрошения процессора и увеличения его быстродействия, он дополнительно содерл ит триггер блокировки и третий элемент «И, причем четвертый выход операционного блока соединен шиной блокировки счета с входом установки триггера блокировки, вход гашения которого соединен шиной конца операции с третьим выходом операционного блока, а выход триггера блокировки соединен с первым входом третьего элемента «И, второй вход которого соединен шиной чтения микрокоманд с первым выходом операционного блока, а выход третьего элемента «И соединен с вторым входом счетчика микрокоманд, выход которого соединен с вторым входом схемы сравнения, третий вход которой соединен с вторым выходом регистра микрокоманд.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор | 1974 |

|

SU512471A1 |

| Микропрограммный процессор | 1974 |

|

SU535567A1 |

| Микропрограммный процессор с контролем | 1981 |

|

SU985791A1 |

| Микропрограммный процессор | 1978 |

|

SU765809A2 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Микропрограммный процессор | 1977 |

|

SU705452A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Процессор | 1984 |

|

SU1246108A1 |

| Микропрограммный процессор с контролем | 1980 |

|

SU862144A1 |

Авторы

Даты

1975-10-30—Публикация

1973-05-07—Подача