1

Изобретение относится к вычислительной технике, в частности к проектированию микропрограммных процессоров с контролем.

Известны микропрограммные процессоры, содержащие память микрокоманд, адресный регистр, регистр микрокоманд, операционный блок, регистр кода операции, схему сравнения, триггер фиксации сбоя, первый и второй элементы «И, элемент «ИЛИ, элемент «НЕ. Первый выход операционного блока связан с входом регистра кода операции, выход этого регистра - с первым входом первого элемента «И, второй вход которого соединен с первым входом первого элемепта «ИЛИ и шиной начала операции с вторЫМ выходом oneрационного блока, а выход - с лервым входом адресного регистра. Выход адресного регистра подключен к первому входу памяти микро-команд, второй ее вход шиной чтения микрокоманд связан с третьим выходом oneрационного блока, а выход-с входом регистра микрокоманд, первый выход которого соединен с первым входоад операционного блока, а второй выход - с вторым входом операционного блока и с первым входом второго элемента «И. Выход последнего подключен к второму входу адресного регистра, третий вход регистра шиной коица операции связан с четвертым выходом операционного блока и с вторым входом первого элемента «ИЛИ,

выход которого через элемент «НЕ соединен с вторым входом второго элемента «И, а третий вход операционного блока - с выходом триггера фиксации сбоя, вход которого подсоединен к выходу схемы сравнения.

Однако в известных микропрограммных процессорах контроль последовательностей микрокоманд требует значительных затрат оборудования для хранения проверяемых адресов и подсчетов числа микрокоманд, а также усложняет процесс -микропрограммирования в связи с предварительным просчетом числа микрокОМанд в неразветвленной части .микропрограммы.

Цель изобретения - сокращение оборудования для контроля.

Это достигается тем, что в процессор дополнительно введен второй элемент «ИЛИ. Первый его вход соединен с выходом адресного регистра, второй вход - с вторым выходом регистра микрокоманд, а выход - с первым входом схемы сравиения, второй вход которой связан с выходом регистра кода операции, а третий вход -с выходом первого элемента «ИЛИ.

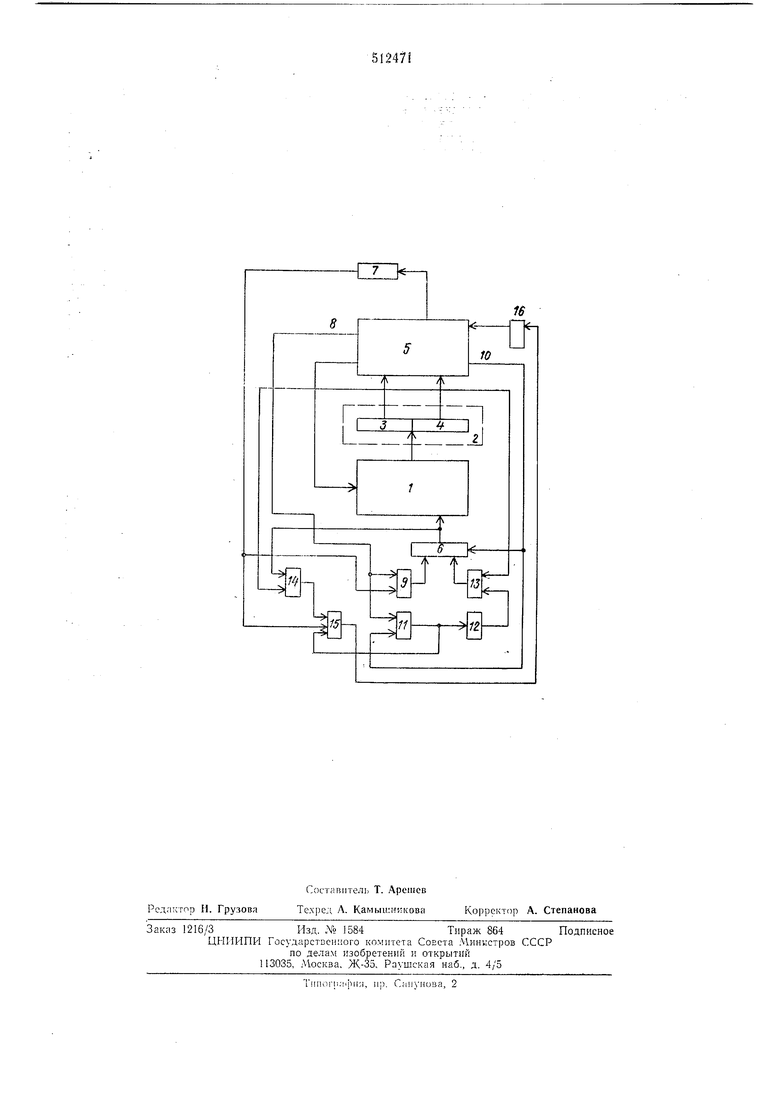

На чертеже показана функциональная схема микропрограммного процессора, где: 1 - память микрокоманд; 2 - регистр микрокоманд; 3- поле микрокоманды; 4-адресное поле; 5 - операционный блок; 6-адресный регистр; 7 -регистр кода операции; 8- шина начала операции; 9 -элемент 10- шида конца операции; 11-элемент 12 -элемент 13 - элемент 14- элемент 15 - схема сравнения; 16- триггер фиксации сбоя. Микропрограммный процессор ра-ботает следующим образом. Микрокоманды выбираются из памяти 1 микрокоманд в регистр 2 микрокоманды, разделенный на поле 3 микрокоманды и адресное поле 4. Иоле микрокоманды управляет работой операционного блока 5. Адресное поле определяет адрес следующей микрокоманды и передается после выполнения текущей микрокоманды в адресный регистр 6, управляющий выборкой из памяти микрокоманд. Выборка микрокоманды управляется операционным блоком 5 с помощью передачи сигналов по шине чтения микрокоманд в память 1 .микрокоманд. Операционный блок осуществляет арифметические и логические преобразования информации и контролирует правильность их выполнения. Правильность считывания информации из памяти микрокоманд в регистр 2 микрокоманд также .контролируется по четности операционным блоком 5. Выполнение команды разделено на два цикла: цикл выборки команды из оперативной памяти и адресных преобразований и цикл исполнения команды в соответствии с кодом операции. Цикл выборки команды и адресных преобразований является общим для всех команд, цикл исполнения команды включает различные микропрограммы для разных команд. Первоначальный вход в программу после пуска процессора осуществляется следующим образом. Перед пуском процессора в счетчике команд устанавливается начальный адрес программы, а все остальные регистры гасятся. Так как адресный регистр 6 погашен, то с момента пуска выполняется микропрограмма, начинающаяся с нулевого адреса, т. е. микропрограмма цикла выборки команды по адресу, указанному в счетчике команд. После исполненпя микропрограммы цикла выборки команды Процессор переходит к циклу исполнения команды и т. д. В конце цикла выборки команды и адресных преобразований ее код операции поступает в регистр 7 и операционный блок 5 возбуждает сигнал на шине 8 операции. При этом код операции команды через элементы «И 9 передается в старшие разряды адресното регистра 6 и начинает выполнятся микропрограмма цикла исполнения команды. В конце микропрограммы исполнения команды операционный блок 5 возбуждает сигнал на шине 10 операции, который гасит адресный регистр и осуществляет переход к нонолнению микропрограммы цикла выборки следующей команды, начинающейся с нулевого адреса. В ходе выполнения микропрограмм сигналы на шинах начала 8 и конца 10 операции блока 5 отсутствуют. Выход элемента «ИЛИ 11 имеет значение «О, а выход элемента «НЕ 12 - значение «1, и элементы «И 13 осуществляют передачу адреса очередной микрокоманды из адресного поля 4 регистра 2 микрокоманд в адресный регистр 6. При наличии сигнала на шинах 8 и 10 выход элемента 11 имеет значение «1, выход элемента 12 - значение «О, элементы 13 закрываются. Контроль работы адресного регистра 6 и схем управления выборкой памяти 1 микрокоманд особенно важен, так как сбои этой аппаратуры могут привести к нарушениям последовательности 1микроцрограмм, которые не будут обнаружены схемами контроля считывания информации из памяти микрокоманд. Контроль этой аппаратуры осуществляется следующим образом. При выполнении микрокоманд, формирующих сигналы на щинах начала и конца операции операционного блока 5, элементы «И 13 закрыты и адресное поле 4 регистра 2 микрокоманд свободно. В эти моменты времени адрес следующей микрокоманды определяется не адресным полем регистра микрокоманды, а либо содержимым регистра 7 кода операции, либо заданным фиксированным адресом (например, нулевым) начала цикла выборки команды. Адресное поле регистра микрокоманды используется для контроля правильности последователыности микрокоманд. В последней микрокоманде каждой микропрограммы исполнения команды в освободивщемся адресном поле регистра микрокоманд записывается код исполняемой команды. Операционный блок возбуждает сигнал на шине конца операции, который гасит адресный регистр и через элемент «ИЛИ 11 разрешает работу схемы 15, сравнивающей содержимое регистра кода операции с выходом элементов «ИЛИ 14. Входы последних связаны с адресным регистром и с адресным полем регистра микрокоманды. Так как адресный регистр должен быть погашен, то на выходе элементов «ИЛИ 14 должен быть код, записанный в адресном поле регистра микрокоманды, который, в свою очередь, должен быть равен содержимому регистра кода операции, и сигнал на выходе схемы сравнения равен нулю. Это является признаком правильного окончания выполняемой команды. Другими словами, при правильной работе адресного регистра и схем управления выборкой цоследовательность выполнения микрокоманд в данной микропрограмме не нарушается. При сбое в адресном регистре или в схемах управления выборкой памяти микрокоманд последовательность выполнения микроколманд нарушается и начинает выполняться другая микропрограмма, в последней микрокоманде которой в адресном поле записан другой код. В этом случае схема сравнения вырабатывает на своем выходе сигнал несобтветствИя кодов адресного поля и регистра кода операции. Этот сигнал устанавлива ет в единичное состояние триггер 16 фиксации сбоя, соединенный с операционным блоком 5. То же самое происходит, если из-за неисправности схем ;не гаснет адресный регистр 6.

В последней микрокоманде цикла выборки команды в освободившемся адресном поле регистра микрокоманды записывается .нулевой КОД. В этой микрокоманде операционным блоком возбуждается сигнал на шине начала операции, который через элементы «И 9 передает содержимое регистра кода операции в адресный регистр, а также через элемент «ИЛИ 11 разрешает работу схемы сравнения, которая в этом случае сравнивает содержимое регистра кода операции с содержимым адресного регистра, так как при нулевой информации в адресном поле микрокоманды на выходе элементов «ИЛИ 14 код равен содержимому адресного регистра. При неправильной работе адресного регистра его содержимое не равно регистру кода операции и схема сравнения вырабатывает сигнал несоответствия, устанавливающий в единичное состояние триггер фиксации сбоя.

Таким образом, в начале каждого цикла исполнения команды проверяется правильность передачи содержимого регистра кода операции в адресный регистр, а в конце каждого цикла исполнения команды - закончилось ли .выполнение той же самой микропрограммы, которая была запущена в цикла исполнения команды. Если в процессе выполнения микропрограммы возникает неисправность в адресном регистре либо в схемах выборки из памяти микрокоманд, то последовательность выполнения микрокоманд нарушается и происходит переход в зону исполнения другой команды, что обнаруживается в конце цикла исполнения команды. Кроме того, в конце цикла исполнения команды проверяется гашение адресного регистра для правильного перехода к циклу выборки следующей команды.

6 Ф о р .1 у л а изобретения

Микропрограммный процессор, содержащий память микрокоманд, адресный регистр, регистр микрокоманд, операционный блок, регистр кода операции, схему сравнения, триггер фиксации сбоя, первый и второй элементы «И, элемент «ИЛИ, элемент «НЕ, причем первый выход операционного блока соединен с входом регистра кода операции, выход которого соединен с первым входом первого элемента «И, второй вход которого соединен с первым входом первого элемента «ИЛИ и шиной начала операции с вторым

5 выходом операционного блока, вы.ход соединен с первым входом адресного регистра, выход которого соединен с первым входом памяти микрокоманд, второй вход которой щиной чтения микрокоманд соединен с третьим

0 выходом операционного блока, а выход соединен с входом регистра микрокоманд, первый выход которого соединен с первым входом операционного блока, а второй выход соединен с вторым в.ходом операционного блока и с

5 первым входом второго элемента «И, выход которого соединен с вторым входом адресного регистра, третий вход которого шиной конца операции соединен с четвертым выходом операционного блока и с вторым входом первого

0 элемента «ИЛИ, выход которого через элемент «НЕ соединен с вторым входом второго элемента «И, третий вход операционного блока соединен с выходом триггера фи.ксации сбоя, .вход которого соединен с выходом схемы

5 ср:авнения, отличаюшийся тем, что, с целью сокращения оборудования, он содержит второй элемент «ИЛИ, первый вход которого соединен с выходом адресного регистра, второй вход - с вторым выходом регистра микрокоманд, а выход-с первым входом схемы сравнения, второй вход которой соединен с выходом регистра кода операции, а третий вход - с выходом первого элемента «ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор | 1973 |

|

SU490122A1 |

| Микропрограммный процессор | 1974 |

|

SU535567A1 |

| Микропрограммный процессор | 1977 |

|

SU705452A1 |

| Микропрограммный процессор с самоконтролем | 1980 |

|

SU1007109A1 |

| Микропрограммный процессор | 1978 |

|

SU765809A2 |

| Микропрограммный процессор с контролем | 1980 |

|

SU862144A1 |

| Микропрограммный процессор с контролем | 1986 |

|

SU1372328A1 |

| Микропрограммный процессор с восстановлением при сбоях | 1973 |

|

SU470806A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Микропрограммный процессор с контролем | 1981 |

|

SU985791A1 |

Авторы

Даты

1976-04-30—Публикация

1974-05-29—Подача